Nand Flash存储器是Flash存储器的一种,其内部采用非线性宏单元模式,为固态大容量内存的实现提供了高性价比、高性能的解决方案。Nand Flash存储器具有容量较大、改写速度快等优点,适用于大量数据的存储,因而在业界得到了越来越广泛的应用。本文则将为大家介绍Nand Flash的工作原理和自身的特性。

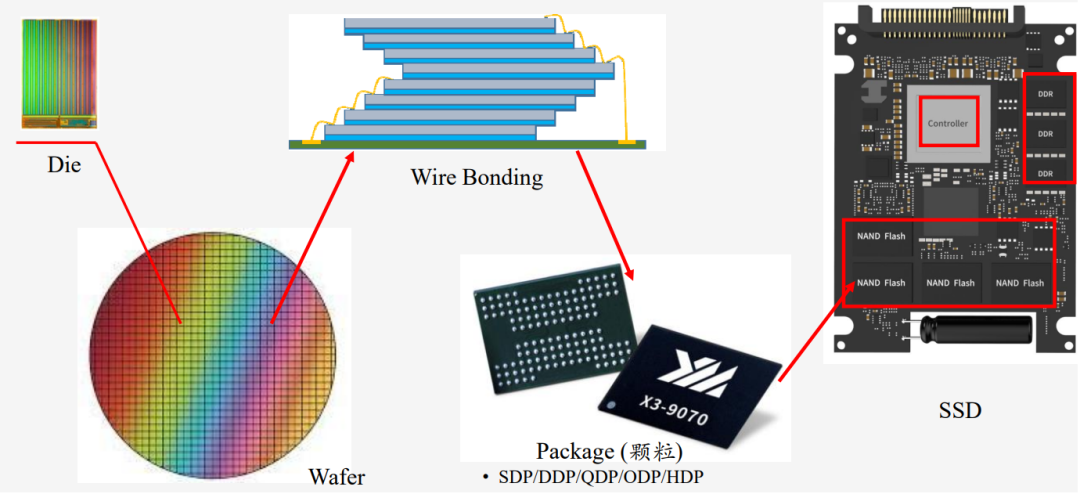

Nand Flash Die 是从Wafer身上切割出来,一个Wafer有很多个Die。之后再进行封装,变成一个颗粒。像图1所示,一个封装可以放1/2/4/8/16个Die,分别叫做SDP/DDP/QDP/ODP/HDP。将颗粒和主控、DDR,电阻、电容等一起焊到PCB板上,就形成了SSD产品。

图1

二、NAND 的历史

自1991年全球首个4MB NAND闪存问世,此后12MB NAND闪存、1GB NAND闪存、1GB MLC NAND闪存也相继推出,直至2007年NAND闪存正式从2D进入3D时代。

国际存储厂商们发布了10年的路标,未来10年介质将持续演进。综合半导体设备制造商以及原厂长期路标来看,预计3D NAND堆叠层数可达500层以上(~2030年)。在未来3年,预计介质存储密度(Gb/mm2)增加一倍,单位成本($/GB)降低50%+,因此,搭载最新的介质来打造SSD产品可以充分享受介质技术进步的红利。

三、NAND Flash 2D to 3D

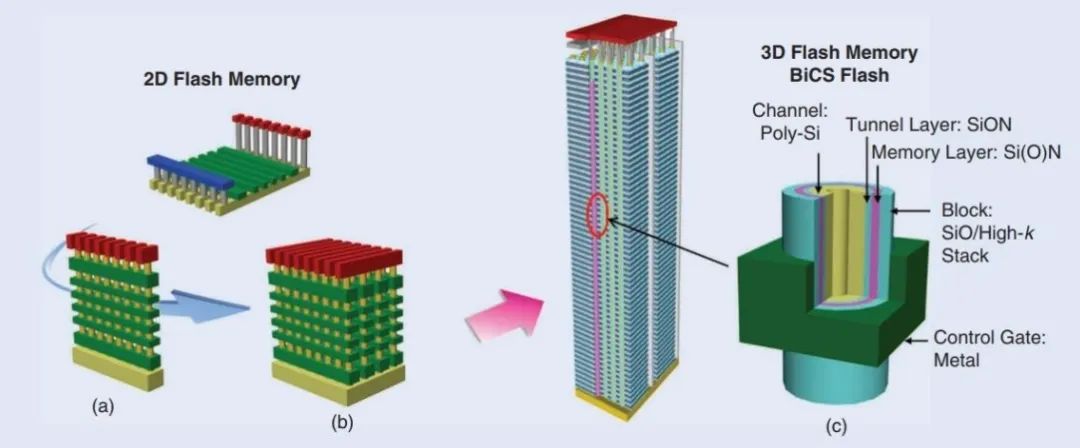

闪存的技术从2D演变到了3D。2D NAND主流技术是Floating Gate(FG) , 通过减小特征尺((e.g. 20nm到16nm) 提高存储密度;3D NAND主流技术是Charge Trap(CT),通过提高堆叠层数(e.g. 64L到96L)提高存储密度,现在主流的存储介质都是基于Charge Trap技术的3D NAND。

图2

3D NAND的演进趋势

- Multi-Stack

通过Multi-Stack技术解决3D堆叠工艺挑战,但Stack之间会产生额外可靠性问题。不同Layer间参数不同,可能导致单Block内RBER/tPROG/tR差异加剧。

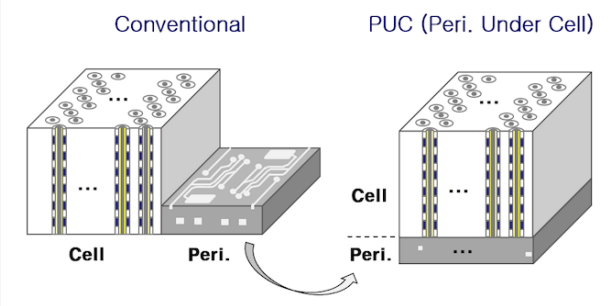

- CNA到CUA/PUC

闪存的Die里面分为存储阵列和外围控制电路,原来并排分布的,即CMOS Near Array(CNA)。后来随着尺寸越来越小,外围电路占的面积越来越大,不利于成本降低,因此把存储阵列放在了电路下面,即CMOS Under Array(CUA)。

图3

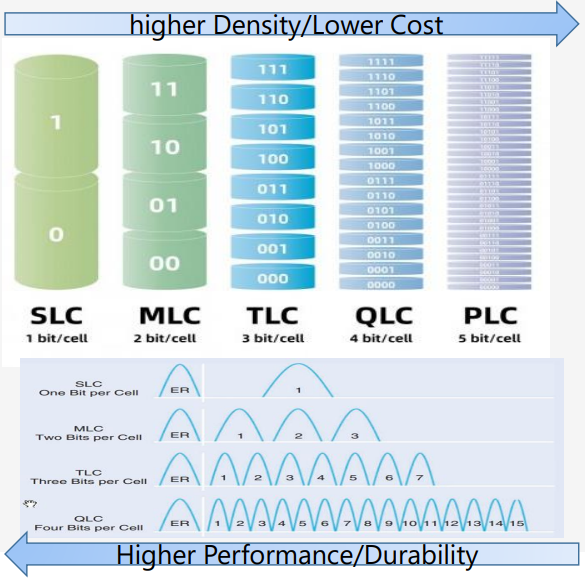

- TLC到QLC到PLC

随着存储密度不断增加,3D TLC (3bits/cell)成为主流存储介质,3D QLC (4bits/cell)蓄势待发。但是随着密度的增加,可靠性会随之降低,所以在应用的时候需要格外小心。现在PLC(5bits/cell)处于实验室技术预研阶段,将持续提高存储密度。

图4

- IOB/Interface Chip

随着介质接口的速度越来越高,Nand引入了接口芯片。现在主流NAND的接口速率是2.4Gbps左右,并快速向3.6/4.8Gbps演进。当产品对介质速率有要求、并且负载较重时,需要IO Buffer(即IOB)来提升介质总线速率。

四、介质持续演进带来的技术挑战

介质将会持续演进,随之带来的是在硬盘产品设计上的挑战,当介质随着层数增加,Block会越来越大。未来一个Block可能将从现在的20-30MB一直扩大到100+MB,而一旦Block受到损坏,将导致100+MB容量空间中的内容直接丢失,这是对系统管理的一大挑战。同时,多次堆叠形成的3D介质,其读写的时延和出错率的一致性,特别是边界上介质的可靠性,都需要特别关注。

下一期将继续为大家分享关于NAND Flash原理和应用的内容。

长按识别关注更多忆联资讯

了解更多:

PCIe标准演进历史

什么是PCIe?

忆联SSD端到端数据保护技术——企业关键业务的“守护者”

原文标题:NAND Flash 原理深度解析(上)

文章出处:【微信公众号:UnionMemory忆联】欢迎添加关注!文章转载请注明出处。

-

存储

+关注

关注

13文章

4296浏览量

85795 -

SSD

+关注

关注

21文章

2857浏览量

117359

原文标题:NAND Flash 原理深度解析(上)

文章出处:【微信号:UnionMemory忆联,微信公众号:UnionMemory忆联】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【半导体存储】关于NAND Flash的一些小知识

NAND Flash与其他类型存储器的区别

NAND Flash的擦写次数介绍

NAND Flash和NOR Flash哪个更好

贴片式tf卡 Nand flash芯片试用体验

NAND Flash上的Vpp是什么?有何功能?

NAND Flash市场营收飙升,厂商迈向300层技术

Flash存储芯片:NOR Flash、NAND Flash、UFS和eMMC的比较与解析

Flash存储芯片:NOR Flash、NAND Flash、UFS和eMMC的比较与解析

什么是NAND 型 Flash 存储器?

NAND Flash 原理深度解析(上)

NAND Flash 原理深度解析(上)

评论