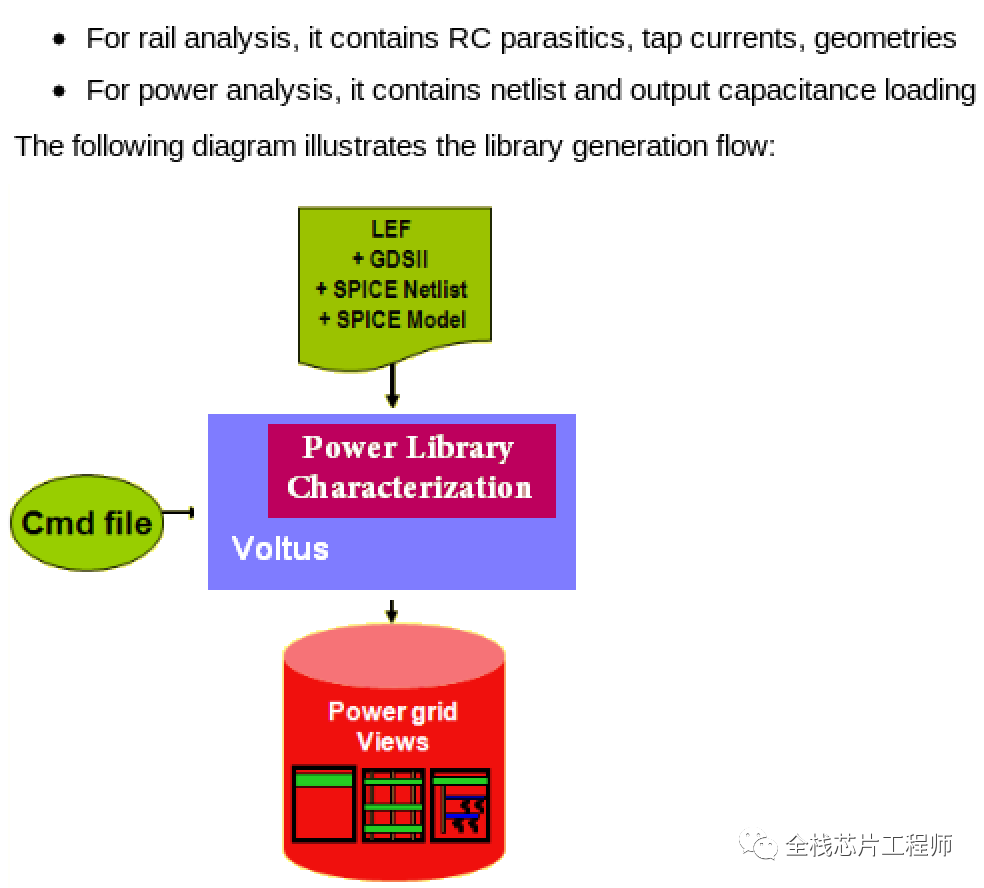

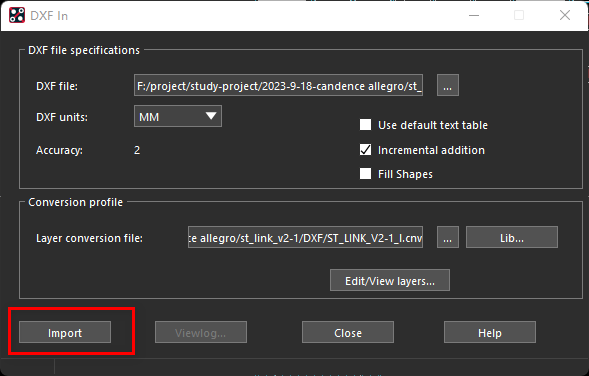

Cadence功耗分析首先需生成power grid library:

其次,power grid library包含如下三部分:

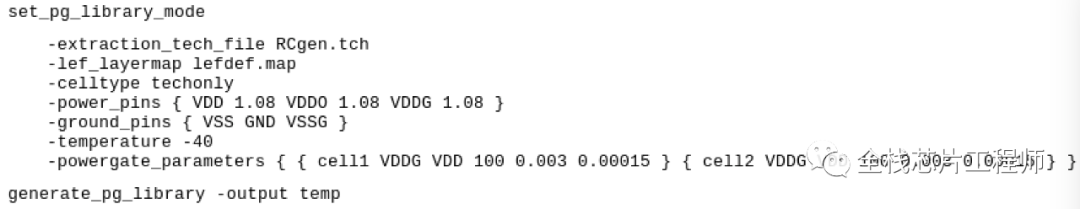

Power-grid library-TechnologyLibrary

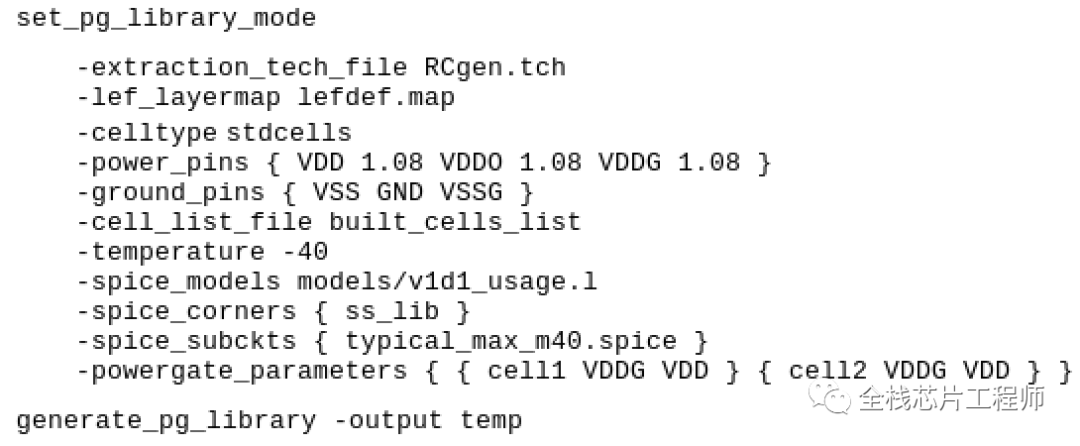

Power-grid library-Standard cell

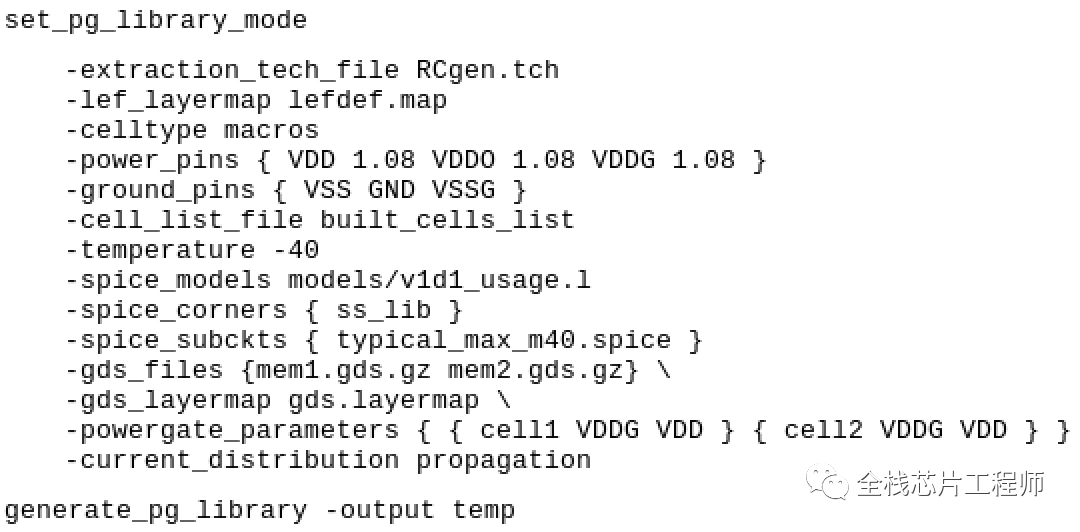

Power-grid library-Macro

按照以上脚本配置,即可完成power grid library库生成备用。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Cadence

+关注

关注

65文章

921浏览量

142061

原文标题:景芯SoC培训营-功耗分析(一)

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Cadence OrCAD and Allegro 17.2 安装破解步骤

Cadence OrCAD and Allegro 17.2 安装破解步骤PCB设计专业群:4676294

发表于 07-26 13:25

Cadence与Tensilica联手共创多媒体低功耗设计方

Tensilica 日前宣布与Cadence 合作,根据Tensilica 的330HiFi 音频处理器和388VDO 视频引擎,为其多媒体子系统建立一个通用功耗格式(CPF)的低功耗参考设计流程。

发表于 12-04 13:54

•32次下载

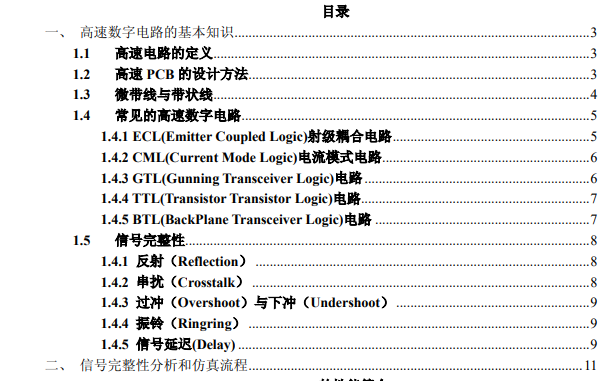

Cadence高速PCB的时序分析

Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资

发表于 04-05 06:37

•0次下载

Cadence PCB SI分析特性阻抗变化因素教程

Cadence PCB SI分析特性阻抗变化因素教程

Cadence 的PCB SI工具是一个强大的SI分析软件,下面我们将采用SI这个软件对对阻抗参数进行

发表于 03-21 18:37

•3498次阅读

Cadence混合信号低功耗设计流程 帮助Silicon Labs将新MCU功耗缩减一半

9月24日——全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,Silicon Labs采用完整的Cadence® 混合信号低功耗设计流程,使其最新款节能型

发表于 09-25 09:59

•1032次阅读

Cadence如何建立PCB?Cadence建立PCB步骤详解

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

发表于 02-07 17:11

•2.7w次阅读

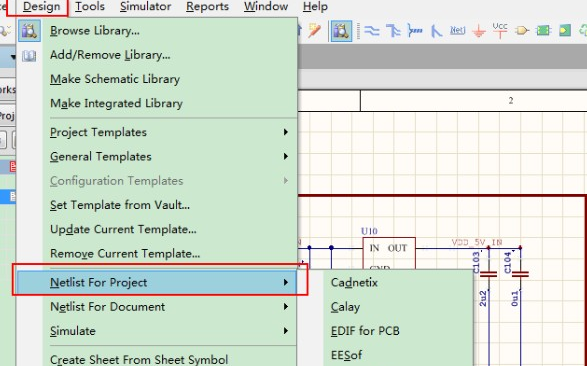

Altium Designer导出Cadence网表的步骤

本文,主要描述了,如何使用Altium Desginer 导出Cadence可以使用的网表

发表于 10-13 09:15

•1.2w次阅读

利用Cadence Allegro PCB SI进行SI仿真分析

本文主要针对高速电路中的信号完整性分析,利用Cadence Allegro PCB SI 工具进行信号完整性(SI)分析。

发表于 12-21 18:00

•0次下载

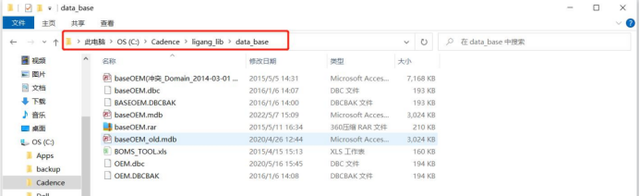

Cadence 16.6连接到数据库的详细步骤

在使用cadence进行硬件电子电路设计中,当原理图设计完成之后,下一个步骤就是将设计好的原理图导入PCB中,然后再进行布局和布线;但是在首次进行原理图导入PCB之前,我们需要先将原理图封装库

使用Xilinx功耗估算器进行准确最差情况功耗分析的七个步骤

德赢Vwin官网

网站提供《使用Xilinx功耗估算器进行准确最差情况功耗分析的七个步骤.pdf》资料免费下载

发表于 09-14 11:07

•2次下载

Cadence功耗分析步骤

Cadence功耗分析步骤

评论