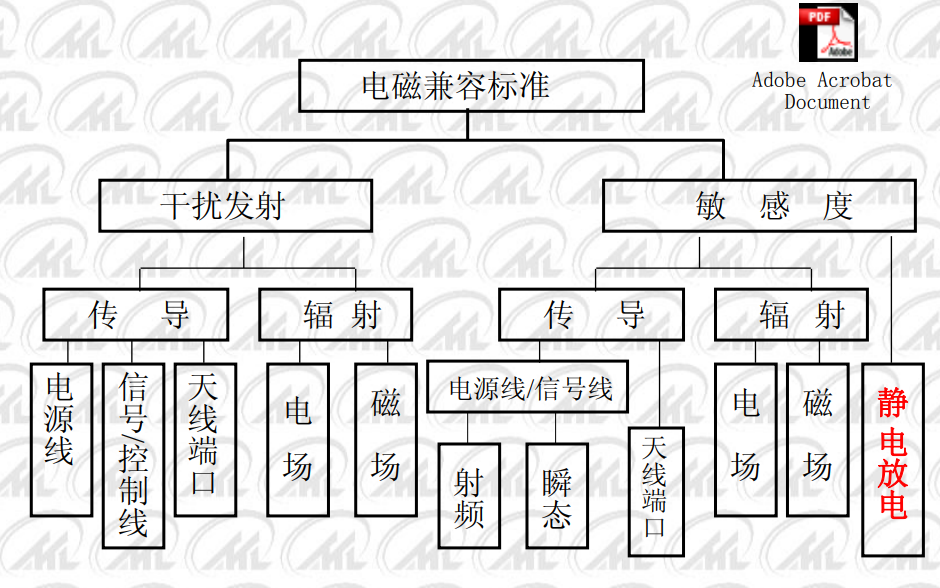

1. 静电放电ESD工程量化分析

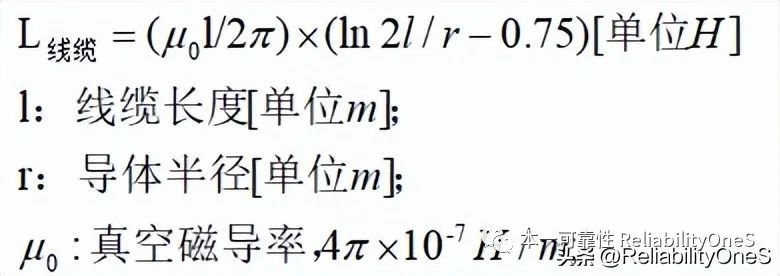

1.1 金属螺柱与线缆的分布电感工程估算

1.2 ESD放电电流估算

注:标准中ESD枪在50Ω阻抗下的电流值,但实际放电电流与放电回路阻抗相关。

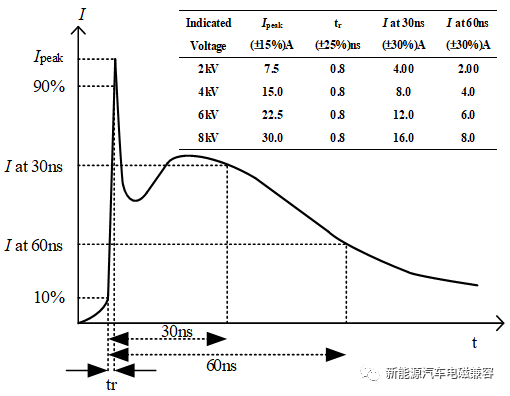

1.3 ESD放电电流等级

Contact discharge current waveform parameters

1.4 回路感应电压估算

1.5 回路感应电压计算过程

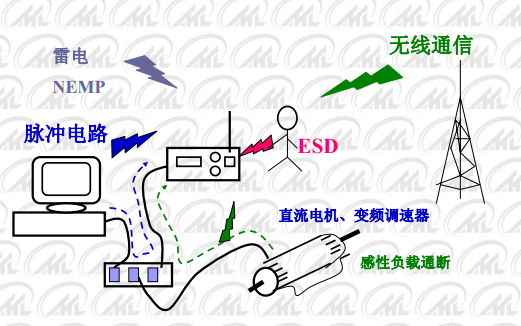

2. 多维路径耦合分析

2.1 驱动器过流问题描述

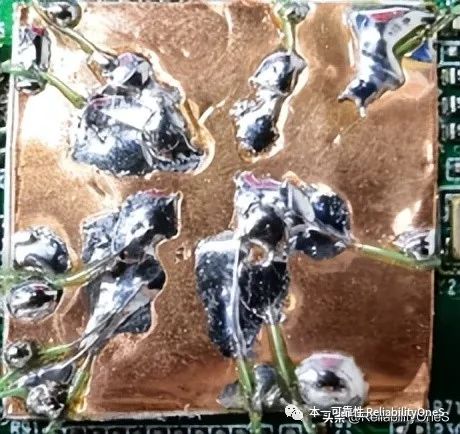

某驱动器在ESD试验中,间接耦合板HCP 1KV放电导致报过流,极度敏感,整改后满足CD-7KV,AD-9KV等级;

2.2 ESD多维路径耦合分析

2.2.1 ESD传导路径分析

(1)ESD传导路径示意图

(2)ESD传导路径排查分析步骤

- STEP1:割断路径①,无改善;

- STEP2:割断路径②,有改善,HCP-4KV放电不报错;

- STEP3:割断路径③,有改善,CD-4KV(注:需要同时去掉才有改善);

(3)ESD传导路径整改分析总结

ISENSE_DCBUS+_MCU、ISENSE_OC、ISENSE_RST的PCB走线为传导干扰的路径之一,且相互影响;

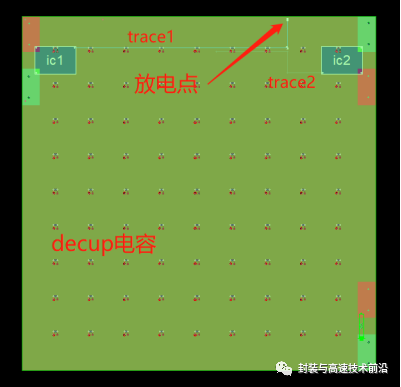

2.2.2 ESD近场耦合分析

(1)ESD近场耦合路径示意图

(2)ESD进场耦合排查分析步骤

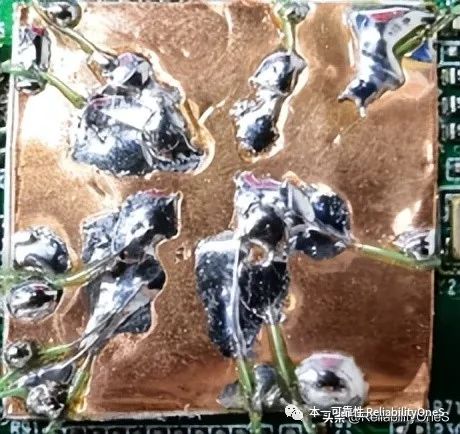

- STEP1:单片机采用铜箔进行屏蔽,无改善;

屏蔽MCU方法示意图

- STEP2:Top层GND进行割板,有改善,可达到CD-4KV;

GND割板方法示意图

- STEP3:ISENSE_OC信号单片机侧+磁珠和TVS管,有改善,可达到CD-6KV;

- STEP4:ISENSE_DCBUS+_MCU、ISENSE_OC、ISENSE_RST、15V电源在板对板连接器处+200pf电容,有改善,可达到CD-7KV;AD-9KV;

(3)ESD近场耦合整改分析总结

- 板对板连接器回路+15V电源的GND回路,在ESD电流下,间接影响母线过流信号;

- ISENSE_DCBUS+_MCU、ISENSE_OC、ISENSE_RST、15V电源在板对板连接器处+200pf 电容,同时ISENSE_OC单片机引脚处+磁珠和TVS管,可满足要求;

- 15V电源GND的TOP铺铜需要优化,保证面积最小;

2.3 总结

(1)近场耦合

top层的15V的GND铺铜回路面积过大(约200mm²),6KV-CD静电放电时,GND瞬间波动约为50V左右,是导致导致母线过流报错主要原因;

(2)传导路径

ESD干扰同步会耦合到母线过流相关信号,导致报错;

2.4 整改落地方法

2.4.1 15V电源处理

- 15V电源的top层铺铜优化,保证GND无U型及环路面积,且15V与GND环路面积最小;

- 15V电源叠层板对板连接器处增加200pf左右的滤波电容,减小回流面积;

2.4.2 信号处理

- PCB板上ISENSE_DCBUS+_MCU、ISENSE_OC、ISENSE_RST信号在板对板连接器处增加200pf滤波电容,减小回流面积及三个信号线间的ESD干扰引起的串扰;

- ISENSE_OC靠近单片机引脚处加200Ω左右磁珠及BV05C的TVS管,做为滤波及压差嵌位;

3. 设计指导建议

- 距离金属螺柱附近top层或bottom层上的敏感信号或伴地设计的回路面积小于≤4mm²;

- 超过4mm²面积的回路需要进行滤波和防护处理;

- 敏感信号尽量远离金属部件(15KV-ESD放电间距5mm左右);

- ESD为低压驱动器的设计难点,需要软件进行滤波类处理,减小硬件设计压力;

-

驱动器

+关注

关注

52文章

8226浏览量

146251 -

连接器

+关注

关注

98文章

14476浏览量

136428 -

静电放电

+关注

关注

3文章

286浏览量

44639 -

ESD保护

+关注

关注

0文章

433浏览量

27024 -

PCB走线

+关注

关注

3文章

135浏览量

13917

发布评论请先 登录

相关推荐

ESD静电放电

ESD静电放电产生的原理和危害

静电放电ESD的介绍和原理及解决方法概述

ESD静电放电问题仿真分析

静电放电ESD工程量化与多维路径耦合分析

静电放电ESD工程量化与多维路径耦合分析

评论