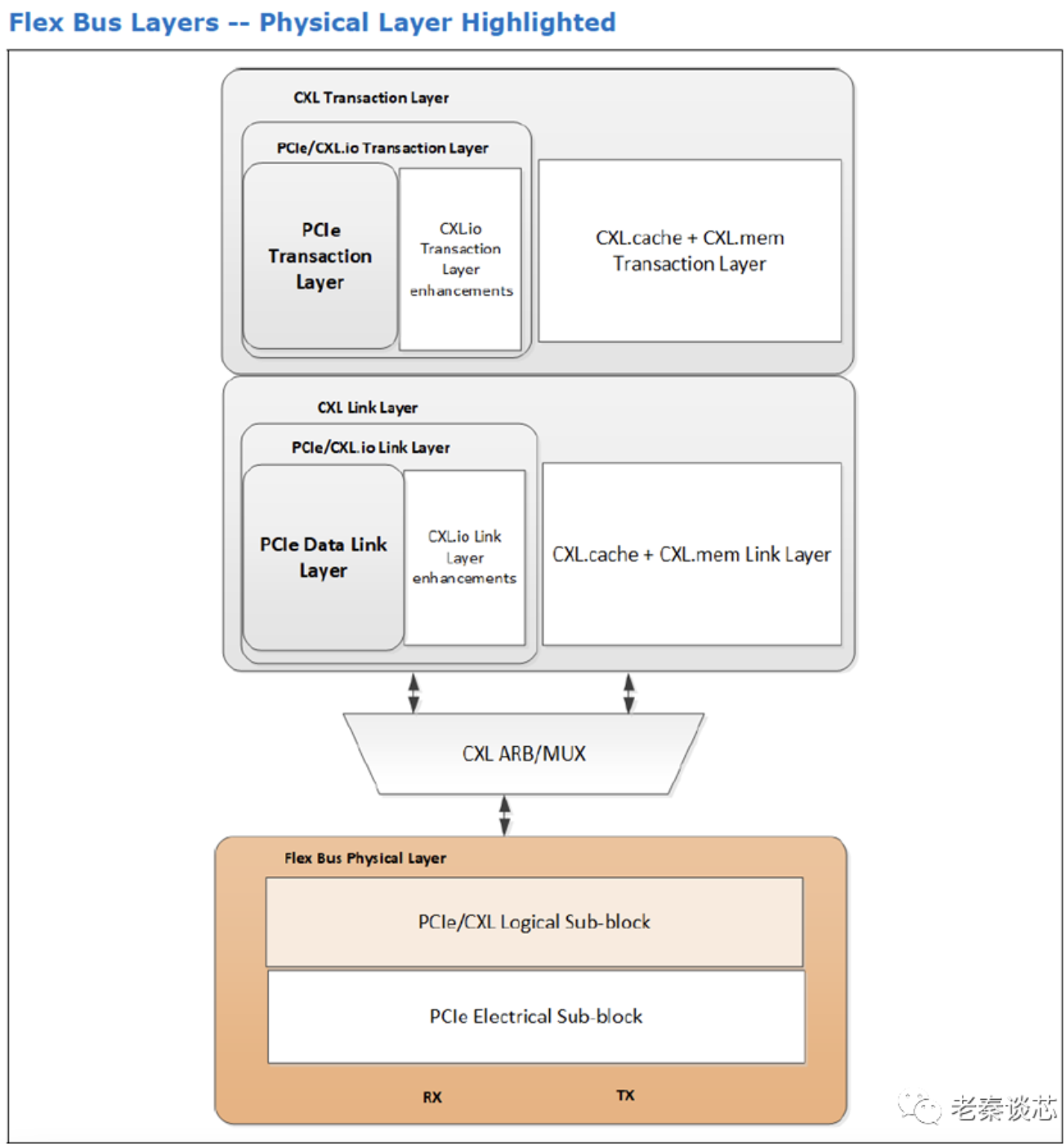

在传输端,Flex Bus物理层准备从PCIe链路层或CXL ARB/MUX接收的数据,以便通过Flex Bus链路进行传输。在接收端,Flex Bus物理层对Flex Bus链路上接收的数据进行串并转换,并将其转换为适当的格式,以转发到PCIe链路层或ARB/MUX。

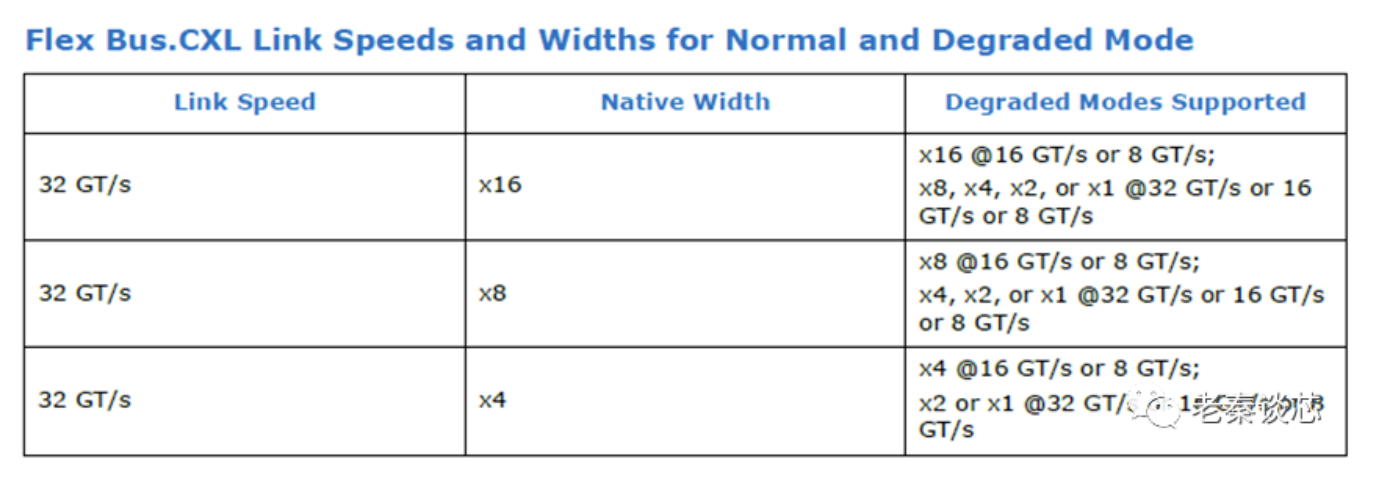

在初始链路训练期间,逻辑PHY在PCIe模式下工作,在训练至2.5 GT/s后,根据备用模式协商的结果,在适当的情况下切换到CXL模式。在CXL模式下,正常操作在本机链路宽度和32 GT/s链路速度下进行。降级运行模式包括8 GT/s或16 GT/s链路速度,和较小的x2和x1链路宽度。下表总结了协议支持的CXL链路宽度和链路速度组合。

6.2 Flex Bus的CXL帧和数据

6.2.1 有序集块和数据块

有序集块(Ordered Set Block)和数据块(Data Block)是PCIe里面的概念。有序集块用于训练、进入和退出电气空闲、转换到数据块,以及时钟容差补偿等,这个放到讲PCIe的时候再说。数据块用于传输从CXL链路层接收的flit。16-bit协议ID字段与从链路层接收到的每个528-bit(512-bit数据负载+16-bit CRC) flit相关联。

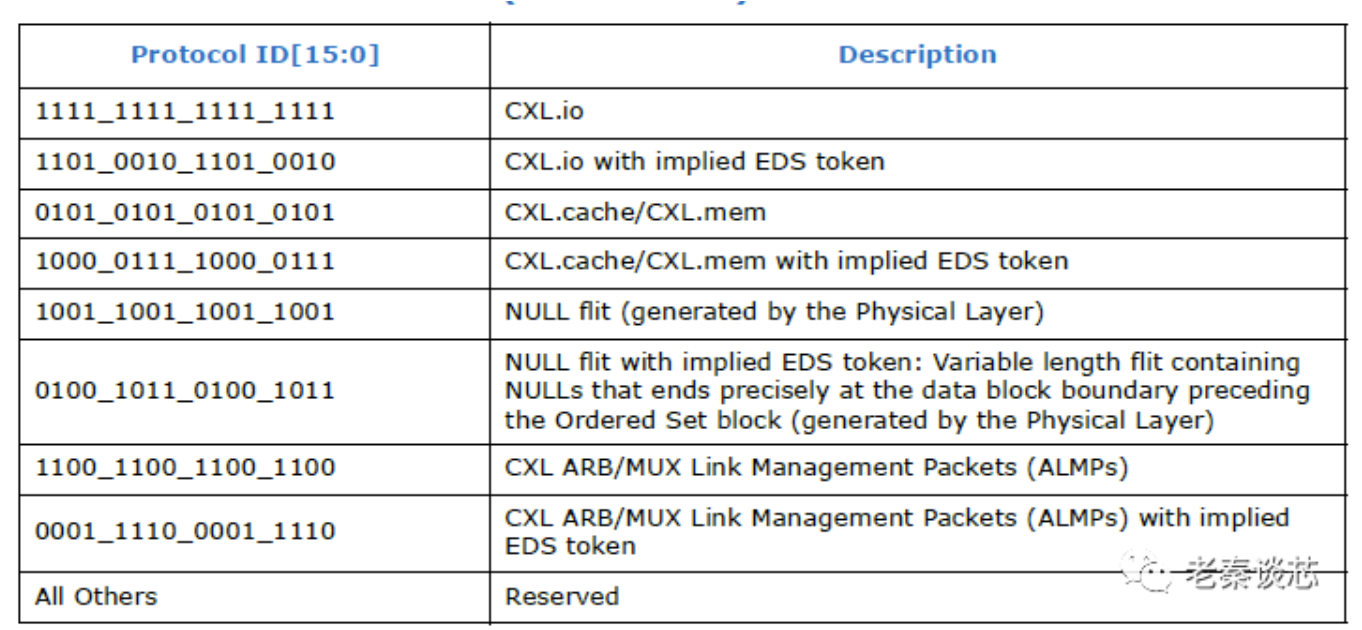

6.2.2 Protocol ID[15:0]

16位协议ID字段指定传输的flit是CXL.io、CXL.cache/CXL.mem还是其他有效负载。

当链路层没有有效flit时,物理层插入NULL flit到数据流中。

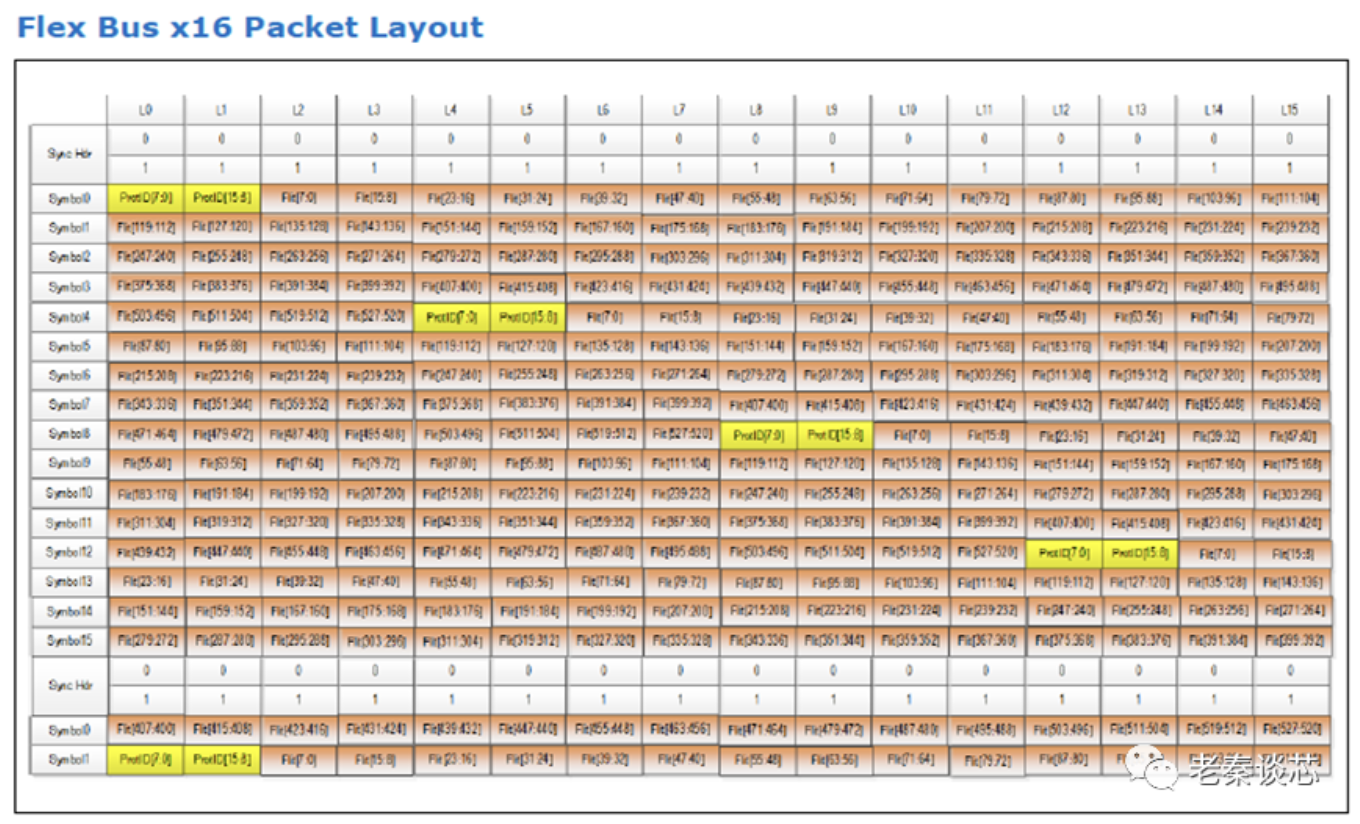

6.2.3 x16数据包

下图显示了x16链接的数据包布局。首先,16-bit传输协议ID被分成两个8-bit,在Lane 0和Lane 1上传输;随后是528-bit flit的传输,同样是按照8-bit粒度拆分。

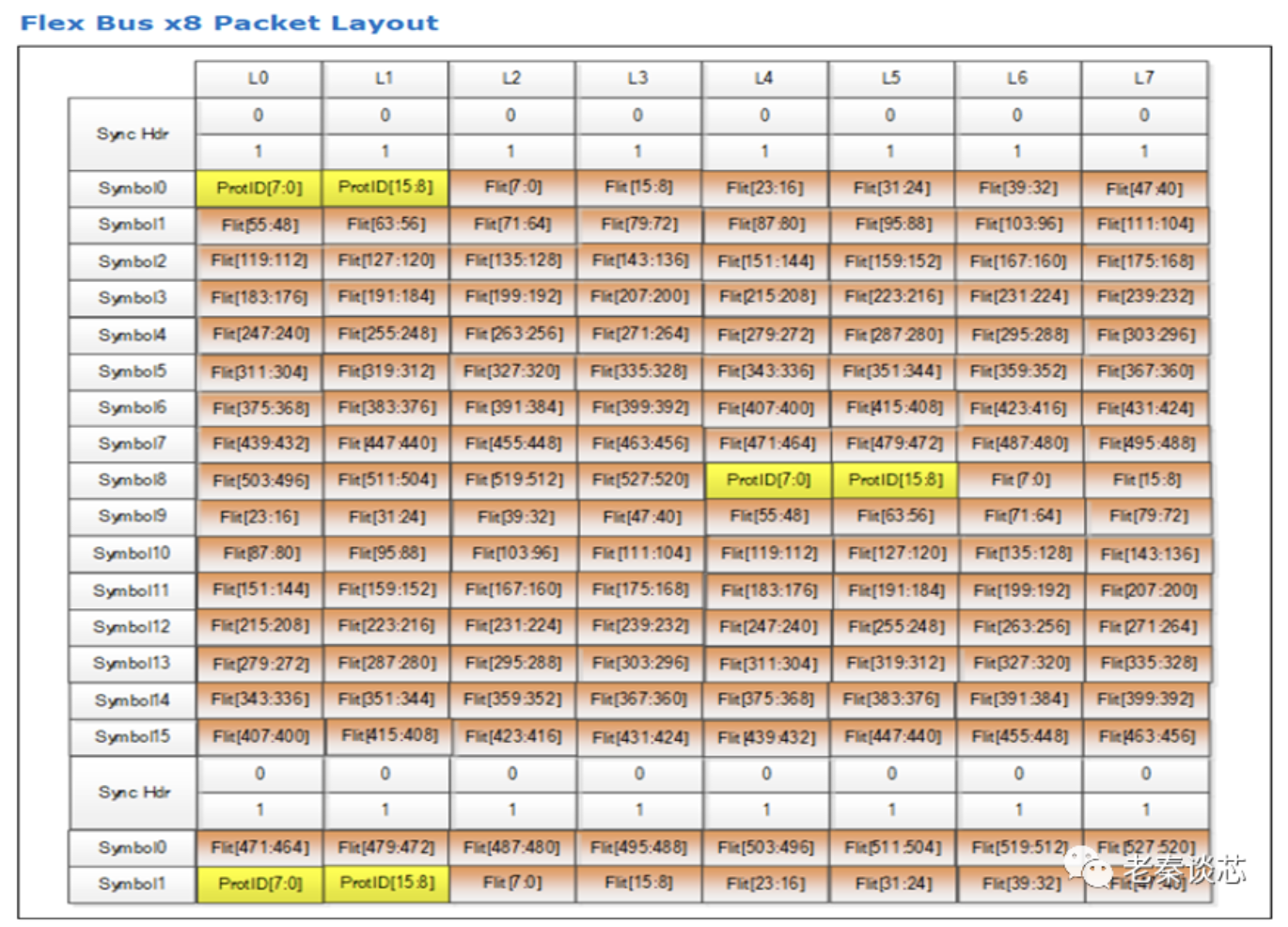

6.2.4 x8数据包

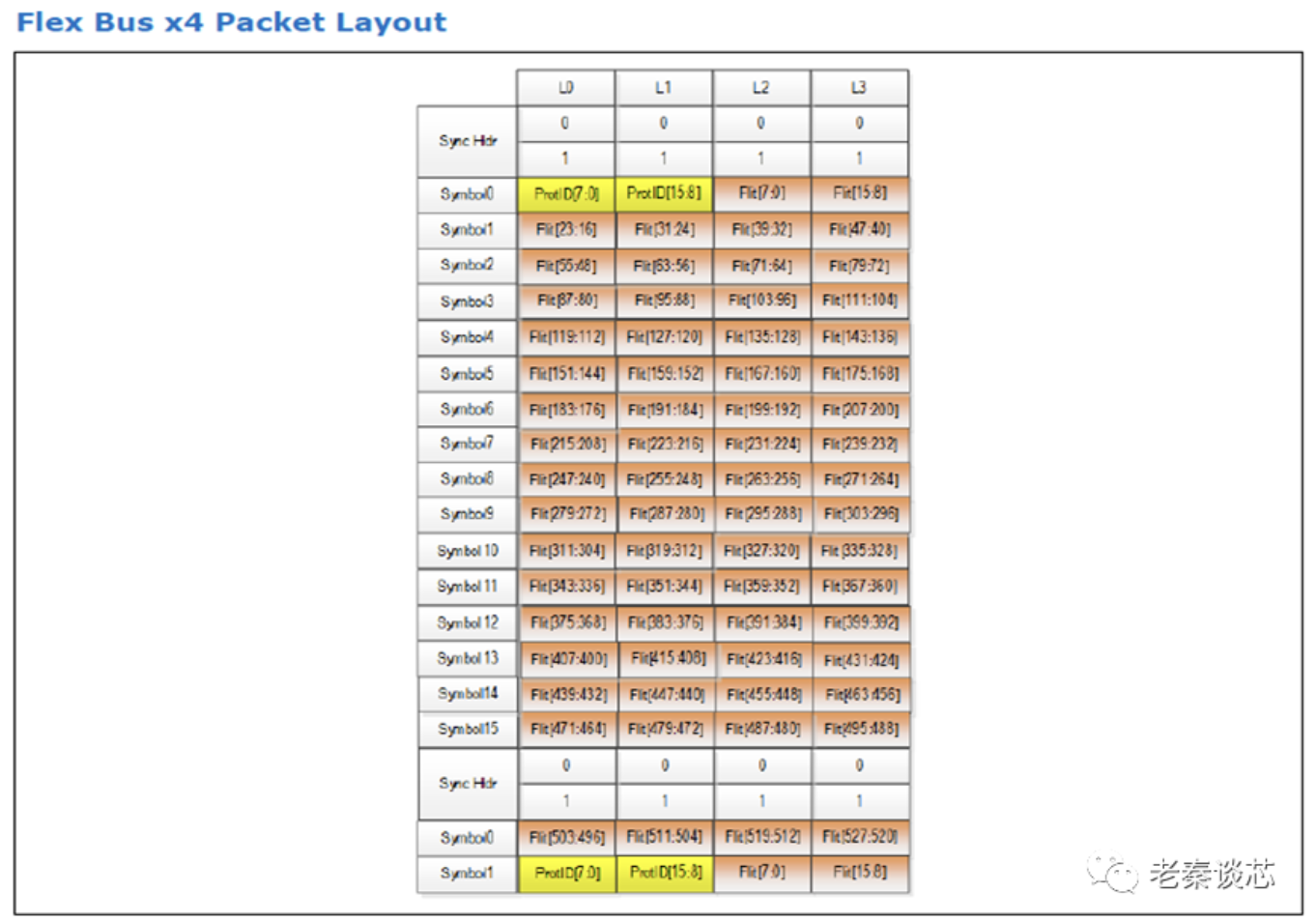

6.2.5 x4数据包

6.2.6 x2数据包

x2数据包布局与x4数据包布局非常相似,协议ID与通道0对齐。16-bit协议ID和528-bit flit以8-bit粒度在两条Lane上传输。

6.2.7 x1数据包

x1数据包布局仅在降级模式下使用。16-bit协议ID后跟528-bit flit在一条Lane上传输。

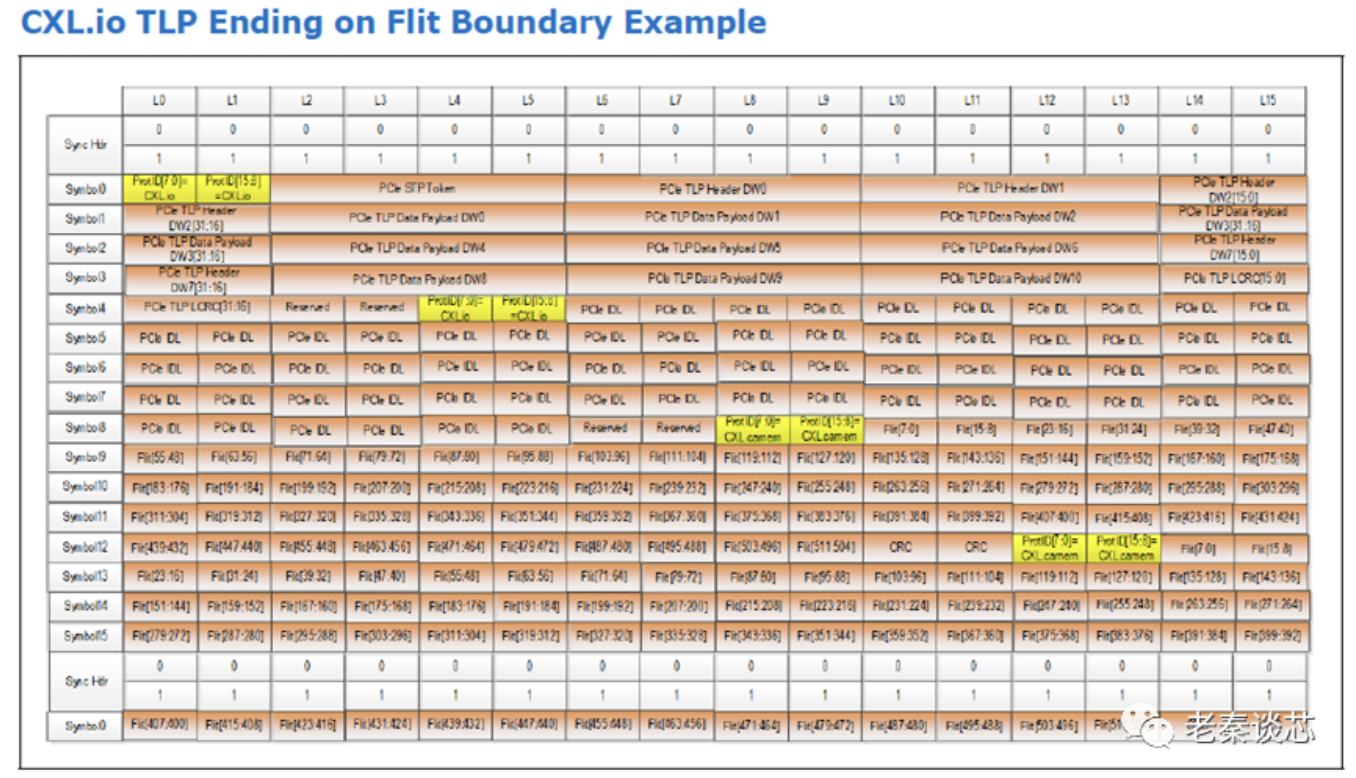

6.2.8 特殊情况:CXL.io – 何时TLP在Flit边界上结束

对于CXL.io,如果TLP在flit边界上结束,且没有额外的CXL.io数据包要发送,但接收端仍然需要随后的EDB(EnD Bad)指示,或IDLE flit,或DLLP,以在处理TLP之前确认此TLP是完好的还是无效的。

下图展示了这种场景,第一个CXL.io flit刚好封装了一个TLP。为保证接收端正确处理,发送端需要在发送一个包含PCIe IDLE令牌的CXL.io flit。

6.2.9 帧错误

物理层负责检测帧错误,并随后启动Recovery以重新训练链路。以下是物理层检测到的帧错误:

- 同步头错误

- 协议ID帧错误

- EDS插入错误

- 528-bit的CXL.io flit中存在PCIe帧错误

6.3 链路训练

6.3.1 PCIe vs Flex Bus.CXL

当LTSSM从Detect状态退出后,Flex Bus链路开始训练,并根据PCIe LTSSM规则完成链路宽度协商和速度协商。在链路训练期间,下游端口通过PCIe备用模式协商机制启动Flex Bus模式协商。在以2.5 GT/s的速度进入L0之前,完成Flex Bus模式协商。

Flex Bus模式的动态硬件协商发生在LTSSM的Configuration状态下的链路训练期间,通过交换PCIe 5.0基本规范定义的Modified TS1和TS2有序集来促进。

6.4 Recovery.Idle和Config.Idle转换到L0

PCIe规范要求从Recovery.Idle切换到L0,或从Config.Idle切换到L0,链路双方需要传输和接收特定数量的连续空闲数据符号。当Flex Bus的逻辑PHY处于CXL模式时,会监测NULL flits而不是空闲字符来启动到L0的转换。当处于CXL模式下Recovery.Idle或Config.Idle时,如果接收到四个连续的NULL flit并且在接收到一个NULL flit之后发送了八个NULL flit时,则下一个状态为L0。

第七章 交换机(Switching)

7.1 概览

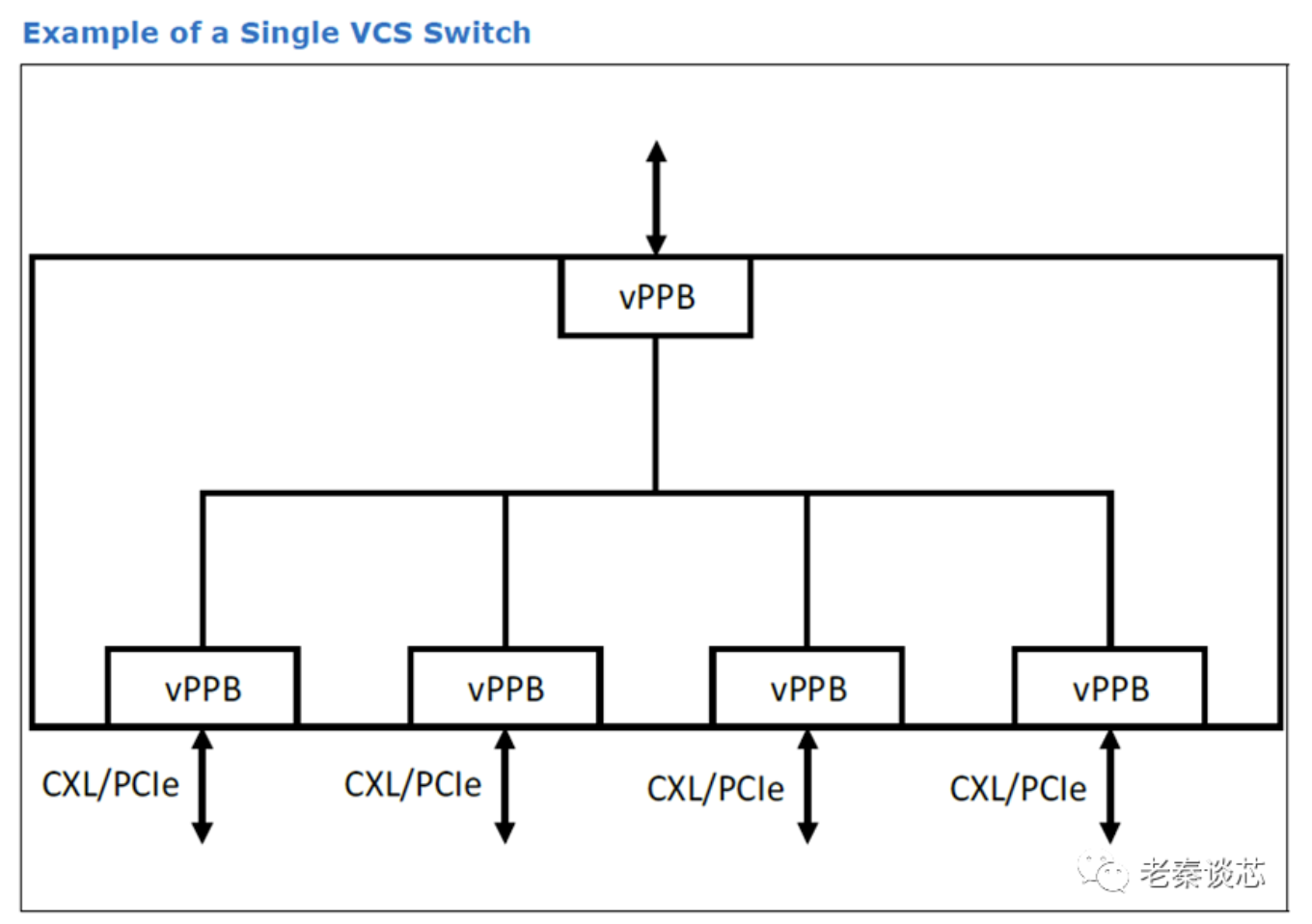

7.1.1 单VCS(Virtual CXL Switch)交换机

图中的vPPB是virtual PCI-to-PCI bridge。单VCS交换机指的是有一个上游端口,若干个下游端口。单VCS交换机须遵守规则:

- 必须有一个上游端口(Upstream Switch Port,USP)

- 必须有一个或多个下游端口(Downstream Switch Port,DSP)

- DSP必须支持PCIe模式和CXL模式

- 所有non-MLD(包括PCIe和SLD)端口都支持vPPB下的单个虚拟层次结构

- DSP必须能够支持CXL 1.1链路

- 必须支持CXL 2.0扩展DVSEC

- DVSEC定义了寄存器,支持CXL.io解码和CXL.mem解码

- Fabric Manager是可选的

解释一下,Fabric Manager是一个独立于交换机或主机固件的实体,它控制与端口和设备的绑定和管理相关的系统方面。

7.1.2 多VCS(Virtual CXL Switch)交换机

多VCS交换机须遵守规则:

- 多于1个USP

- 每个VCS有一个或多个DSP

- 上游vPPB到物理端口的绑定和VCS的结构取决于交换机供应商具体实现

- 每个DSP必须绑定到PPB或vPPB

- Fabric Manager是可选的

- 配置时,每个USP及其关联的DSP形成一个VCS交换机

- DSP必须支持在CXL或PCIe操作模式下运行。

- 所有non-MLD端口都支持下游交换机端口下方的单个虚拟层次结构。

- DSP必须能够支持CXL 1.1链路

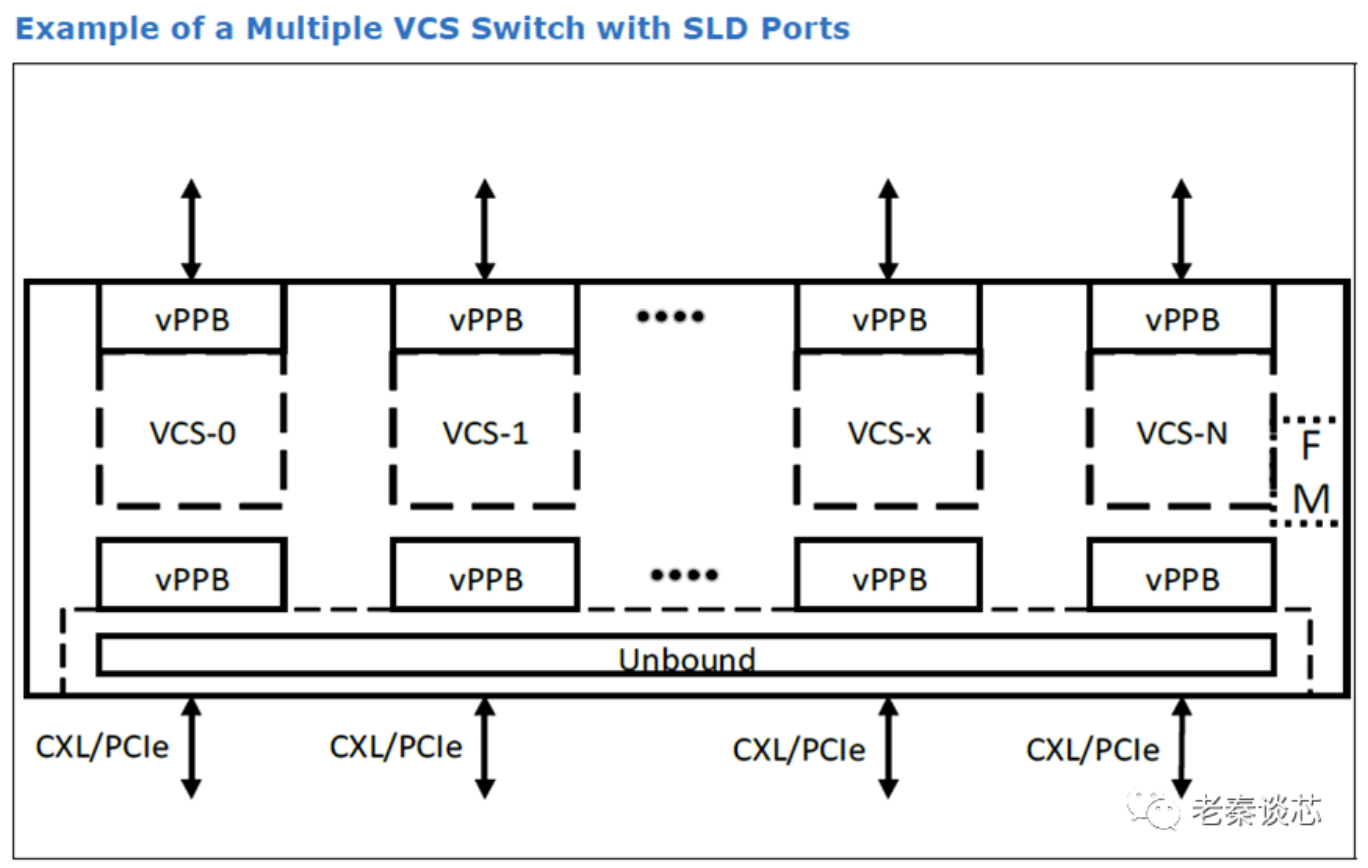

7.1.3 具有MLD端口的多VCS交换机

具有MLD端口的多VCS交换机由多个上游端口交换机和一个或多个下游MLD端口的组合组成。

具体规则不再列出。

7.2 交换机配置和组成

7.2.1 CXL交换机初始化选项

CXL交换机三种初始化方法:

1.静态

2.FM在主机前启动

3.FM和主机同时启动

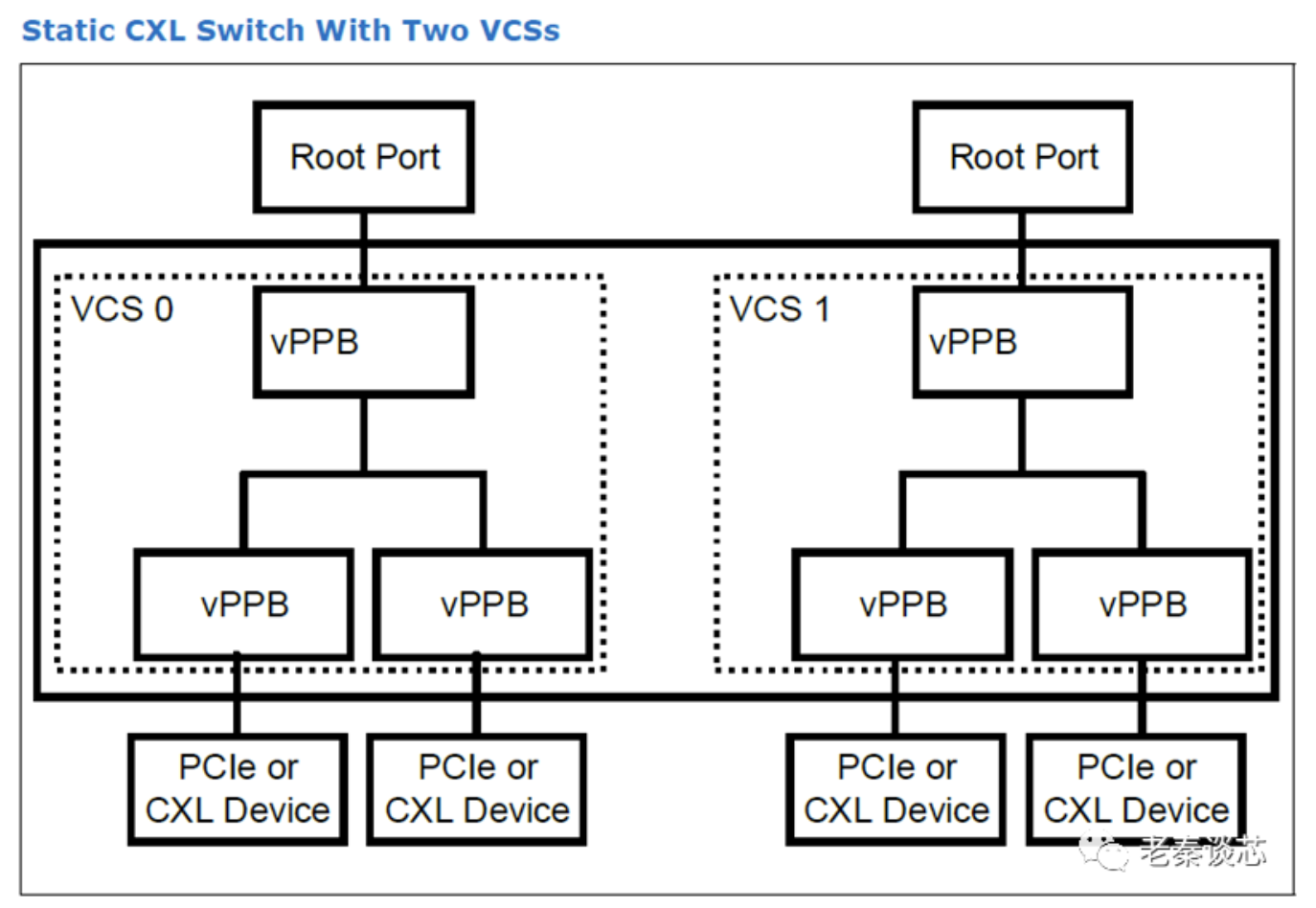

7.2.1.1 静态初始化

下图是静态初始化的例子,下游vPB静态绑定到端口,使用标准的PCIe机制支持设备热插拔。

静态交换机特性:

- 不支持MLD端口

- 不支持将端口重新绑定到不同的VCS

- 不需要FM

- 在交换机启动时,使用特定的机制(例如SPI闪存中的配置文件)静态配置所有VCS和下游端口绑定

- 支持CXL 1.1、CXL 2.0或PCIe下游端口

- VCS(包括vPBs)的行为与PCIe交换机相同,同时添加了对CXL协议的支持

- 当主机启动时,每个VCS都准备好进行枚举

- 支持热插拔

- 不支持异步移除CXL 2.0设备

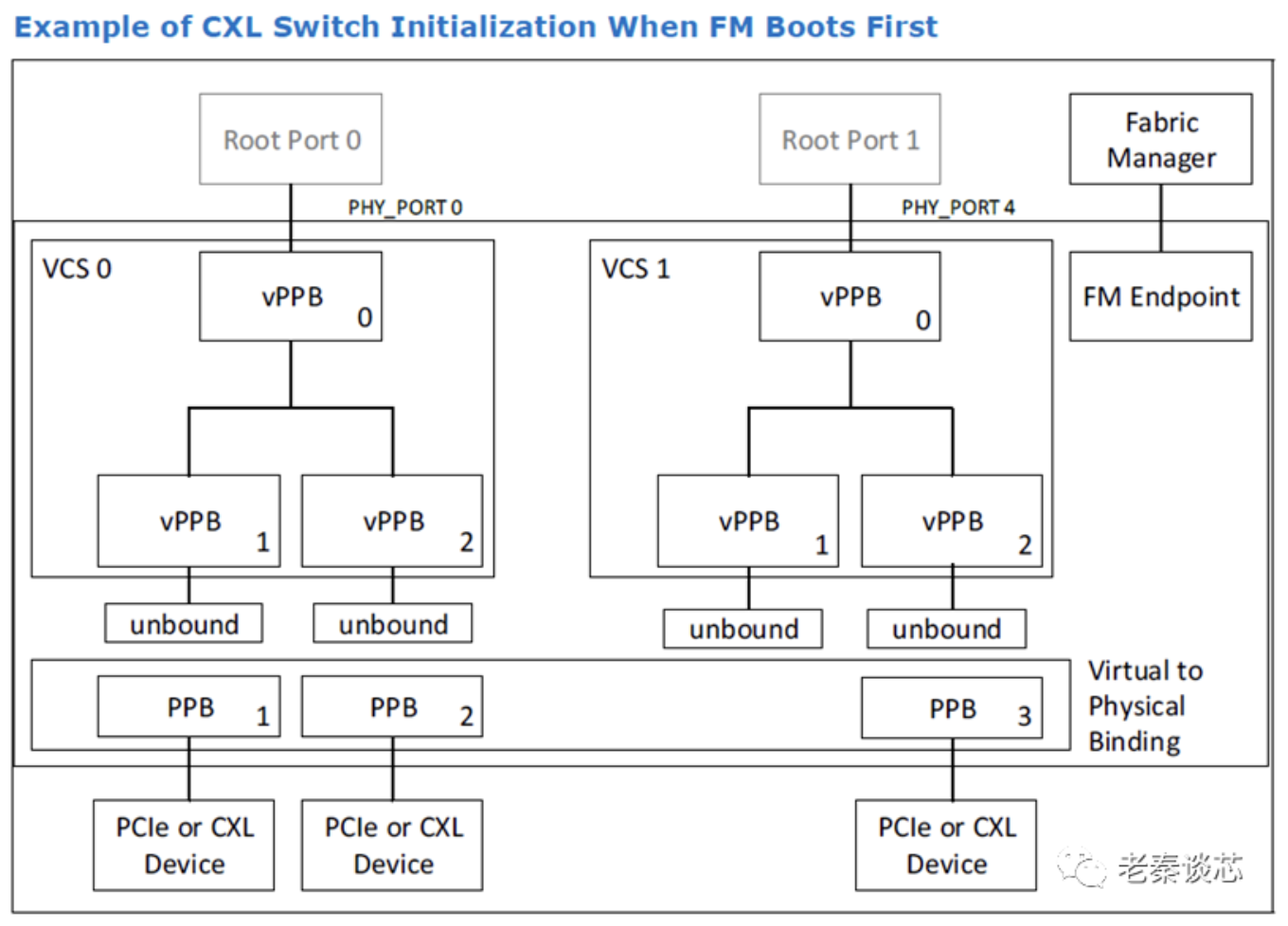

7.2.1.2 FM先启动

在FM先于主机启动的情况下,允许按照以下示例所述初始化交换机。

- Switch和FM启动

- 在本例中,下游vPPB静态绑定到端口,使用标准PCIe机制支持设备的热插拔

- 所有下游端口都没有绑定到VCS,它们归FM所有

- DSP链路建立,交换机通知FM

- FM向交换机发送BIND命令(VCS0、VPPB1、PHY_PORT_ID1)。交换机配置虚拟到物理绑定,如项中所述

- 交换机将vPPB虚拟端口号重新映射为物理端口号

- 交换机将vPPB连接器定义(PERST#、PRSNT#)重新映射到物理连接器

- 交换机禁用链路

- 所有物理的下游PPB功能都直接映射到vPPB

- FM拥有的PPB不再存在于该端口

- 当主机启动时,交换机已准备好进行枚举。

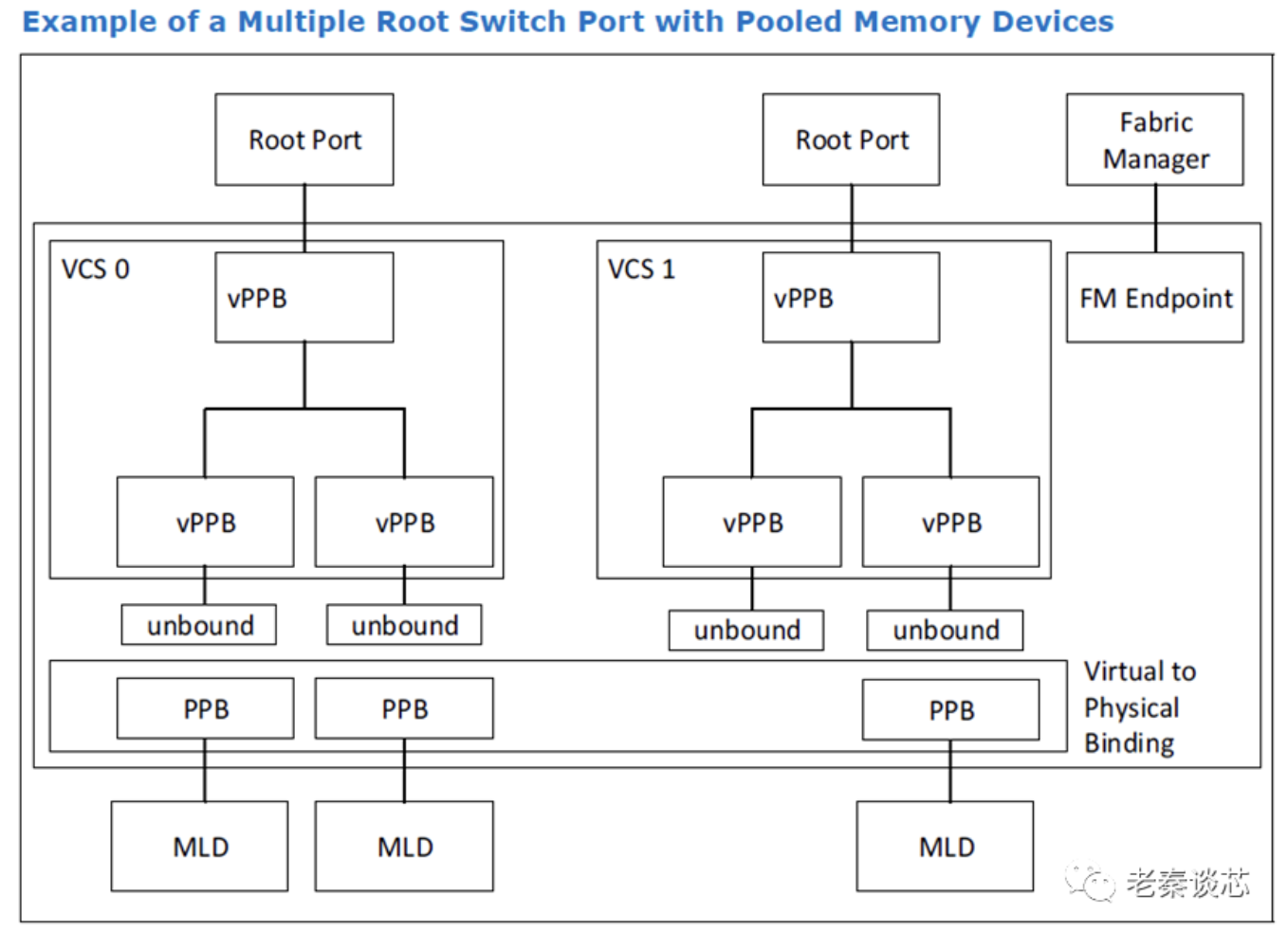

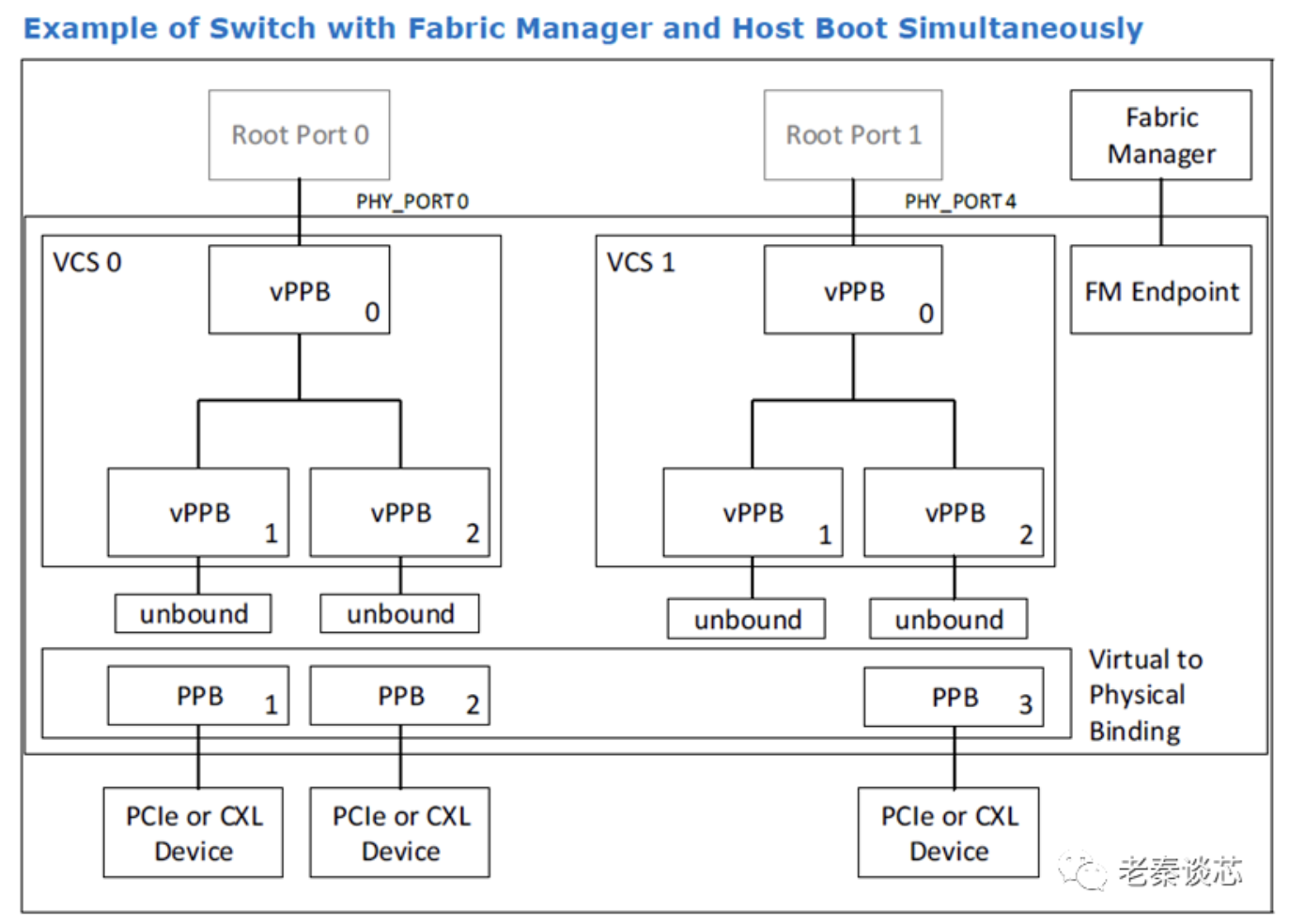

7.2.1.3 FM和主机同时启动

FM和主机同时启动:

1.VCS是静态定义的

2.每个VCS内的vPPB被解除绑定,并作为链路断开呈现给主机

3.交换机发现下游设备并将其呈现给FM

4.主机枚举VH并在上游PPB中配置DVSEC

5.FM执行到vPPB的端口绑定

6.交换机执行虚拟到物理的绑定

7.每个被绑定的端口都产生对主机的热添加指示

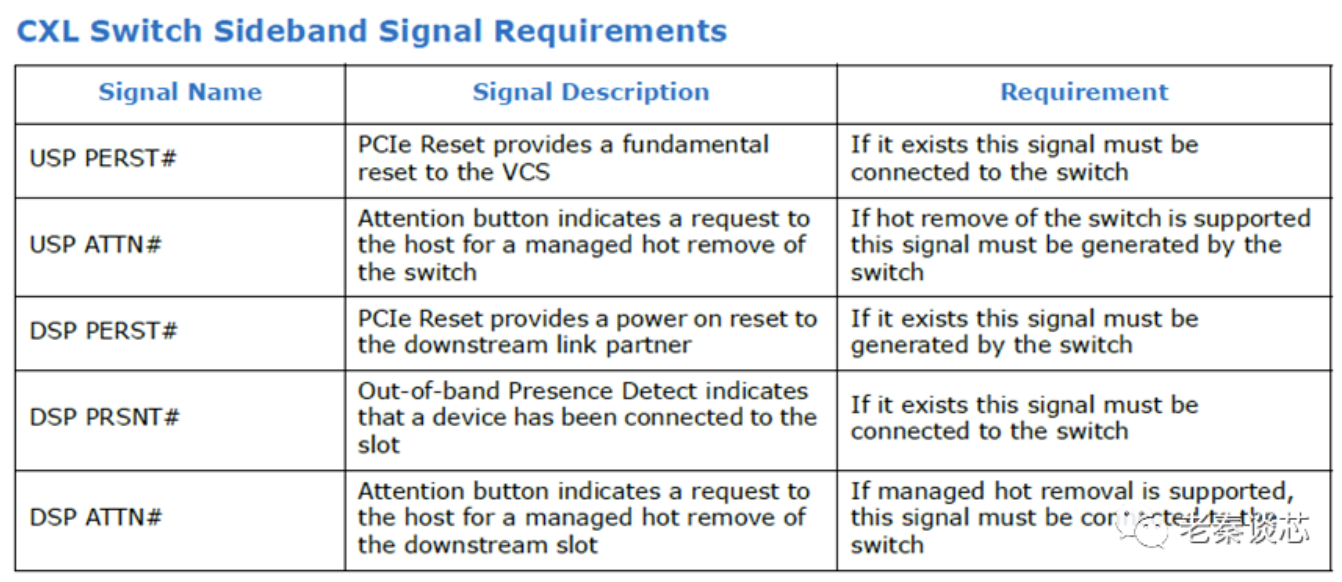

7.2.2 边带信号操作

下表表提供了支持热插拔的最小边带信号集,其它边带信号可选。这些边带信号的行为与PCIe协议中定义的一致。

7.2.3 绑定和解绑

本节是关于CXL设备到vPPB的绑定和解绑。

7.2.4 MLD端口PPB和vPPB行为

MLD端口提供虚拟化接口,以便多个vPPB可以通过共享物理接口访问LDs。因此,绑定到MLD端口的vPPB的特性和行为与绑定到SLD端口的vPPB的特性和行为不同。本节定义了它们之间的区别。

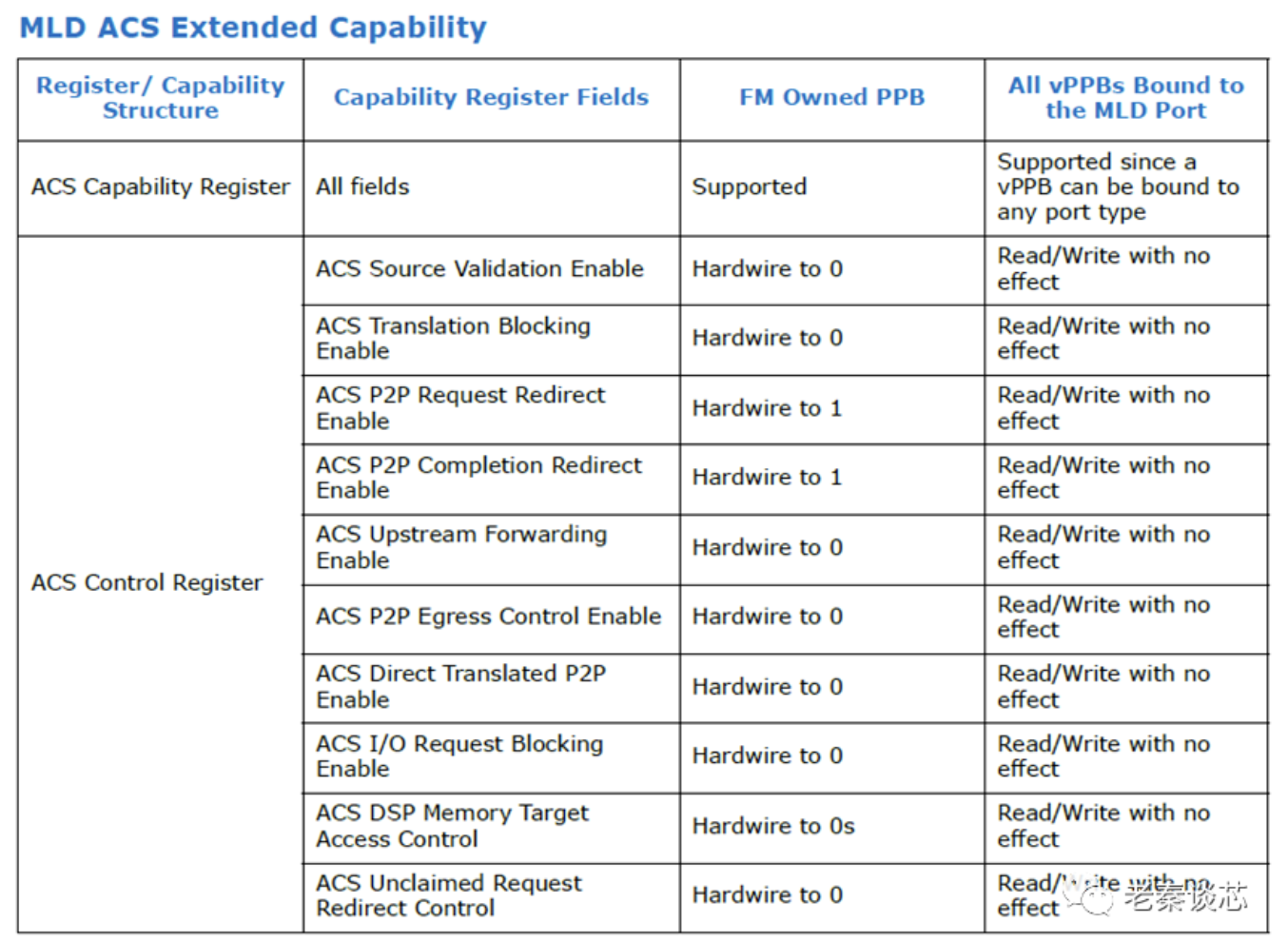

7.2.5 MLD ACS扩展功能

CXL.io的请求事务和完成事务被路由到USP。

7.2.6 MLD PCIe扩展功能

vPPB的PCIe扩展能力结构(Capability Structure)中的所有字段的行为应与PCIe相同,但以下小结中的情况除外。

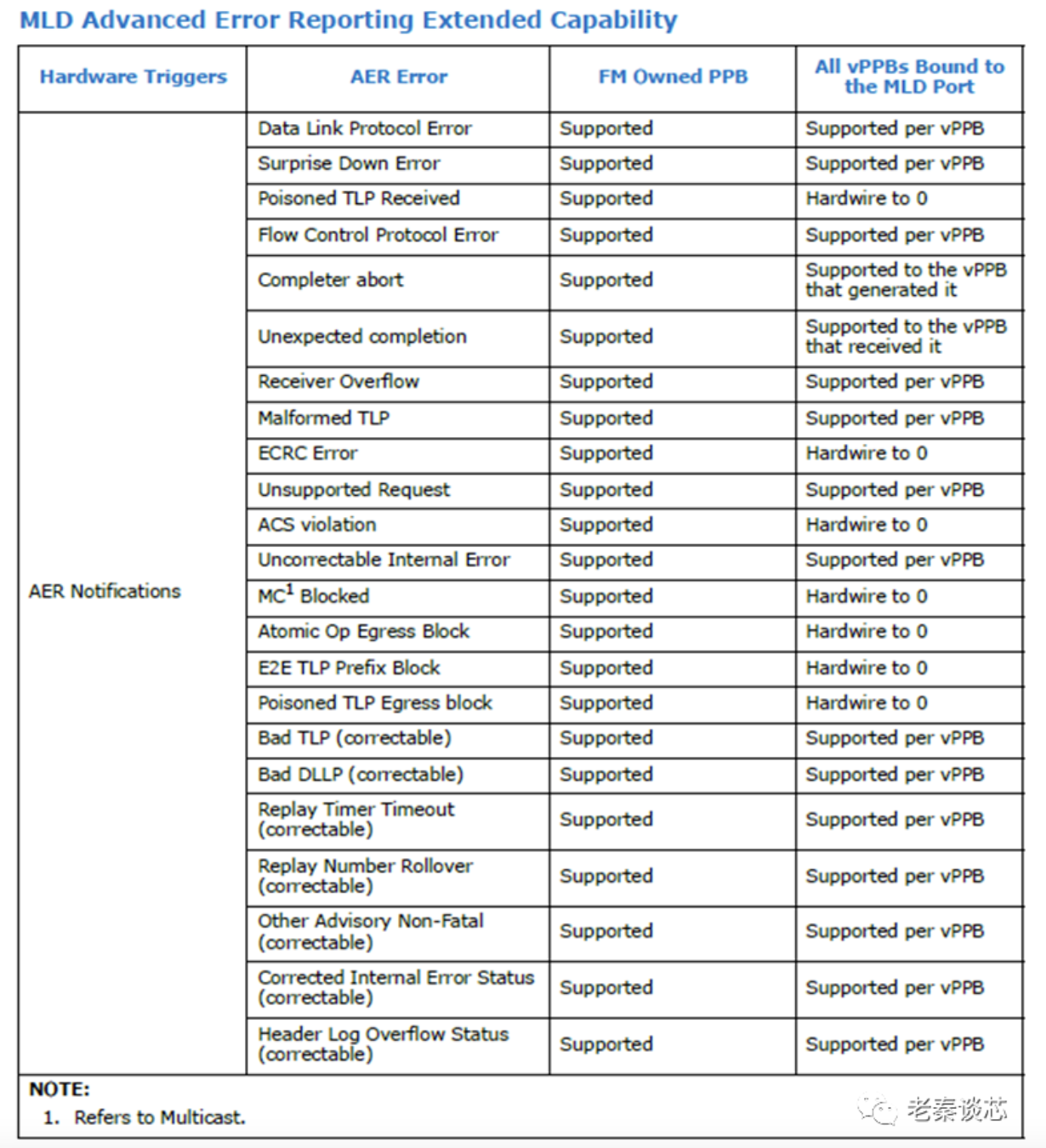

7.2.7 MLD AER(Advanced Error Reporting)扩展功能

MLD端口中的AER分为Triggering、Notification和Reporting。

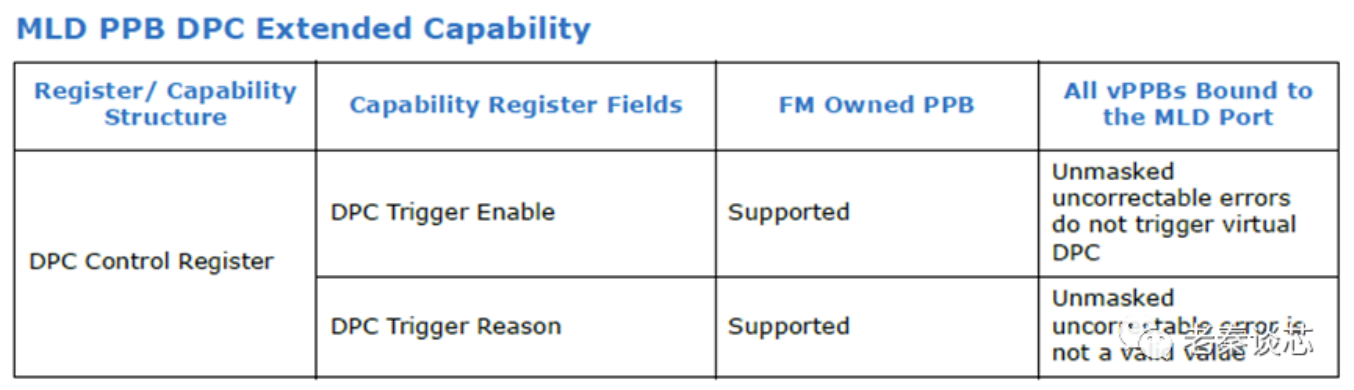

7.2.8 MLD DPC扩展功能

7.3 CXL.io, CXL.cache/CXL.mem解码和转发

7.3.1 CXL.io

在VCS中,CXL.io流量必须遵守PCI Express规范中定义的交换机的相同请求、完成、地址解码和转发规则。

7.3.1.1 CXL.io解码

当TLP由PPB解码时,它根据PCIe基本规范中定义的规则,确定要路由TLP的目标PPB。除非另有规定,PCIe基本规范中定义的所有规则都适用于CXL.io TLP的路由。

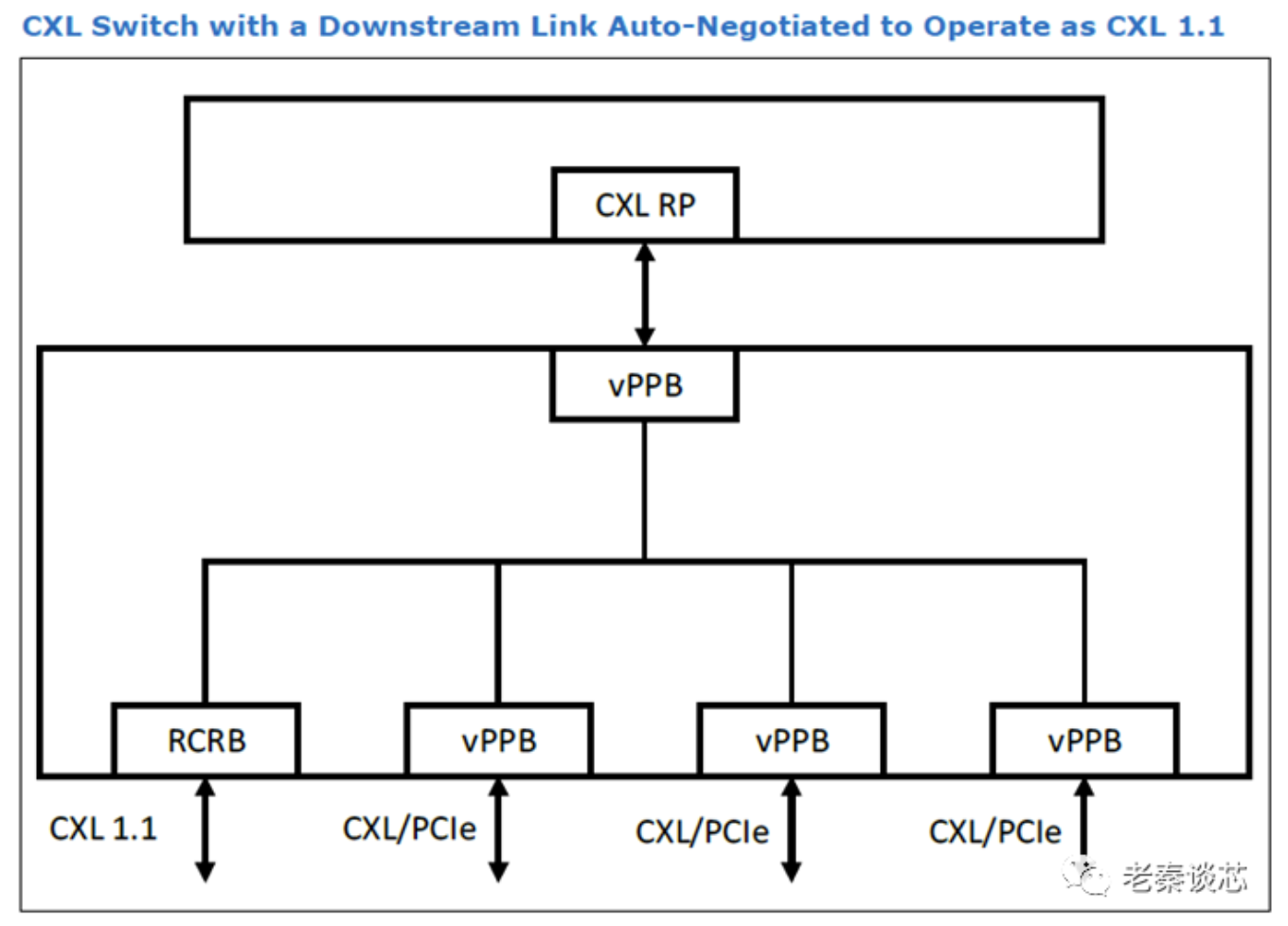

7.3.1.2 CXL 1.1 支持

FM拥有的PPB端口不支持CXL 1.1设备。CXL 1.1设备连接到交换机的话,在软件中必须显示为RCiEP设备。

7.3.2 CXL.cache

仅允许启用VCS中的一个CXL SLD端口来支持Type 1或Type 2设备。USP上接收到的请求和响应被路由到相关的DSP,反之亦然。因此,CXL.cache不需要额外的解码寄存器。

7.3.3 CXL.mem

HDM解码DVSEC功能包含定义内存地址解码范围的寄存器。CXL.mem请求来自主机/RP,并通过交换机向下游流向设备,响应来自设备,并向上游流向RP。

7.3.4 FM Owned PPB CXL Handling

暂时略过。

7.4 CXL交换机电源管理(PM)

7.4.1 CXL Switch ASPM L1

对ASPM L1的支持在第十章中描述。

ASPM(Active State Power Management)是PCIe协议中的一种硬件电源管理机制。

7.4.2 CXL Switch PCI-PM and L2

VCS中的vPPB对PME消息的处理规则与PCIe vPPB相同。

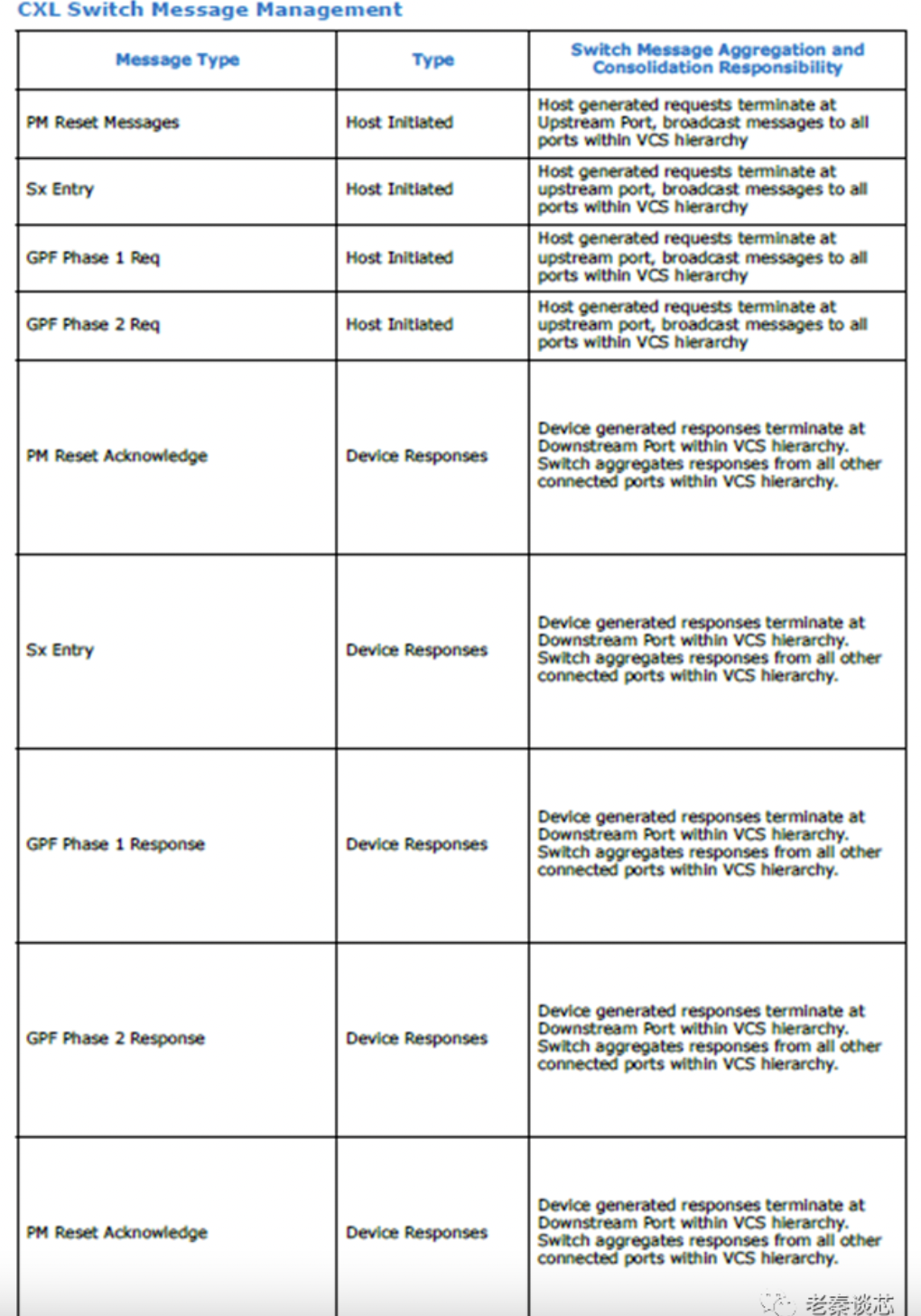

7.4.3 CXL Switch Message Management

CXL VDM属于“Local – Terminate at Receiver”类型。当层次结构中存在交换机时,该交换机实现消息聚合功能。所有主机生成的消息都终止于该交换机,交换机聚合功能负责向下游端口重新生成这些消息。CXL设备生成的所有消息和响应都由交换机聚合和合并,合并后的消息或响应由交换机的上游端口生成,发送给主机。

PM消息信用交换发生在主机和交换机聚合端口之间,并且分别发生在交换机聚合端口和设备之间。

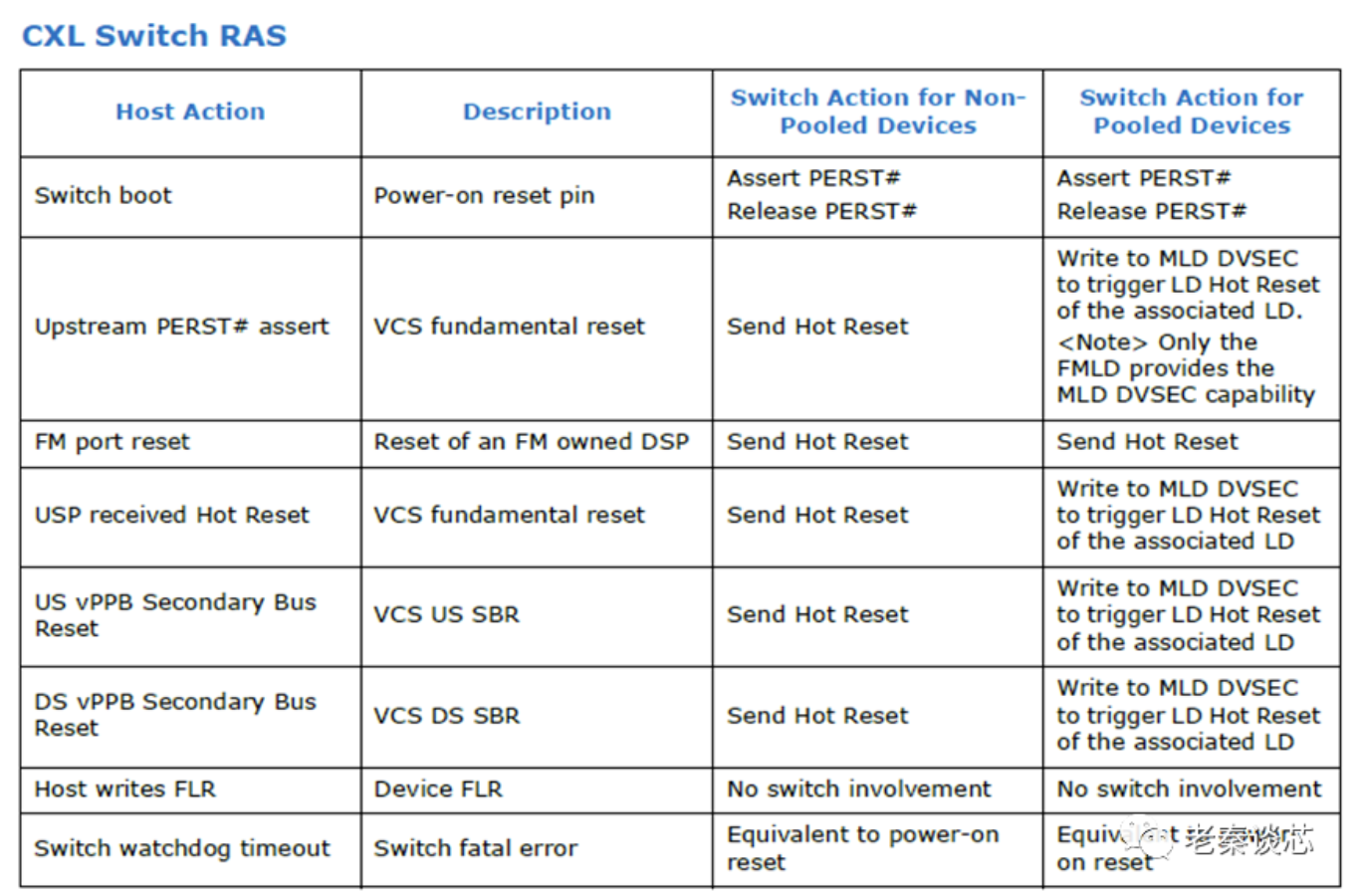

7.5 CXL交换机RAS

7.6 Fabric Manager应用程序编程接口

暂时略过,留给软件开发人员去头疼吧。

总结:本章中的很多概念是基于PCIe基本规范的,不过在PCIe基本规范中并没有专门为Switch设立一章。但是在CXL协议中,Switch承担了很多事情。

-

连接器

+关注

关注

98文章

14476浏览量

136424 -

交换机

+关注

关注

21文章

2637浏览量

99528 -

DSP芯片

+关注

关注

9文章

149浏览量

29958 -

PHY寄存器

+关注

关注

0文章

6浏览量

5326 -

PCIe接口

+关注

关注

0文章

120浏览量

9701

发布评论请先 登录

相关推荐

无线网络物理层借口操作与功能

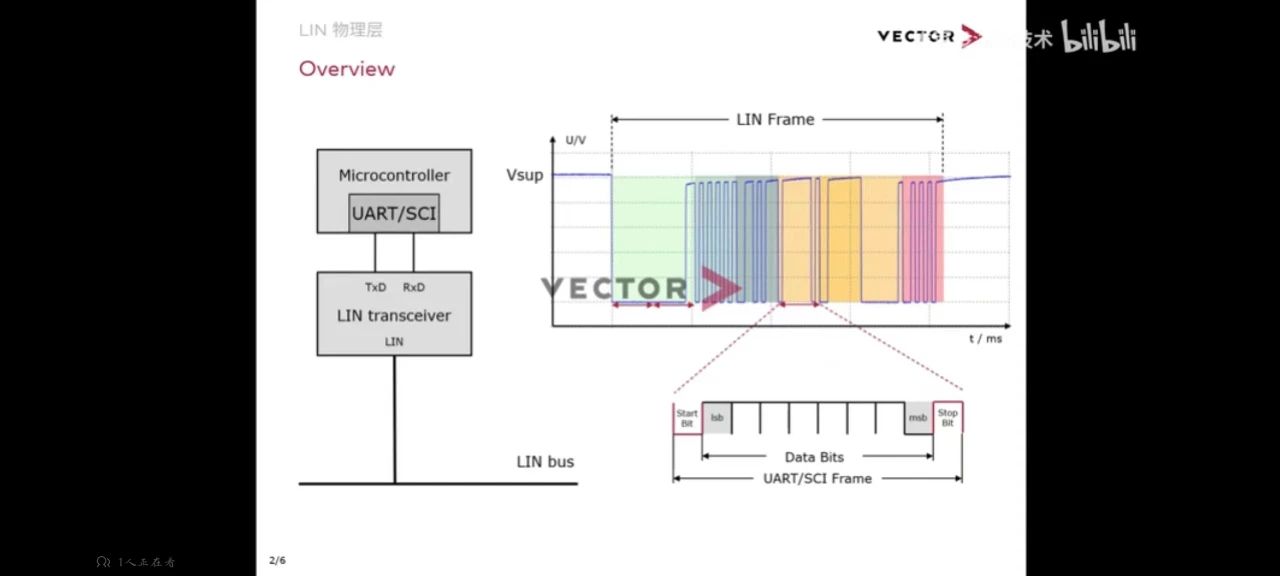

CAN总线不同的物理层

什么是以太网物理层?Ethernet物理层有哪些功能?

一窥CXL协议

物理层 PPT课件

WiMAX(IP-OFDMA)的物理层参数和帧结构

3GPP LTE物理层概述

Flex Bus物理层的CXL帧和数据概述

Flex Bus物理层的CXL帧和数据概述

评论