一看到DDR,联想到的就是高速,一涉及到高速板有些人就比较茫然。高速板主要考虑两个问题点,当然其它3W,2H是基本点。

一是时序,因为有的DDR要跑几百M,所以对应的时钟周期比较短,如果传输线的长度相差较多,会导致数据先到,有的数据后到,数据就不完整。

二是,阻抗,高速信号频率高,波长短,在微波领域是短线传输。如果阻抗不匹配就会产生反射,反射回来的信号与原信号叠加,就改变了原来信号的形状。电磁场与微波相关书籍讲得比较多,涉及到二阶偏微分方程,这里只说结论,我们拿来用就可以了。

总结一下,就两点:

1、等长

2、阻抗要匹配

这两点也是我们做PCBLAYOUT设计时注意的重点,由此也前人也总结出一些相关原则。比如信号分组,同层同组,3W间距等等。

下面我们以DDR3为例,把原理搞清楚,然后根据原理说说实际LAYOUT时要怎么操作。

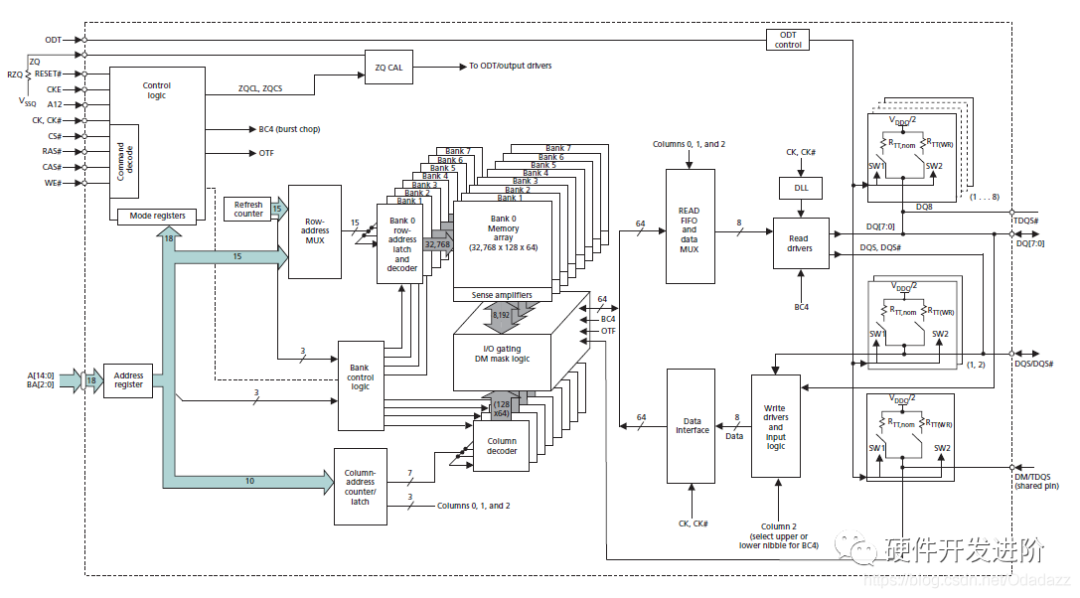

CPU对DDR的访问,也就是读和写的操作,不管是读还是写,你得知道从哪里读,往哪里写吧?所以得知道地址,这个操作叫做寻址。

我觉得我还不能把DDR的原理讲得很清楚,先放下来,好像也不影响我们做DDR的应用设计。

单片DDR3的引脚说明:

我们大概了解了DDR的原理后,就明白,地址线和控制线可以放一组,数据线另外放一组,但因为考虑到设计方面的问题,数据线可以按一个字节进行分组,比如8位放一组,D0-7作为一组,也可以16位放一组,D0-15.一般这两种用得比较多。

以DDR3为例:

数据线1:11根,D0-D7,LDQM(数据掩码),LDQS0.LDQSN0(其中,LDQS0和LDQSN0为差分时钟)

数据线2:11根,D8-D23,UDQM(数据掩码),UDQS0.UDQSN0(其中,UDQS0和UDQSN0为差分时钟)

地址线、控制线和时钟为一组:

A0-A15,BA0-BA2,

CKE,CLK-CLKN ,

CASN,CSN0,xRASN,RESET,WEN,ODT

说明:TI的文档是把地址和数据的时钟放在一组的,但是等长时,地址线与地址的时钟等长,数据线与数据的时钟等长。我这里是把数据和地址的时钟分别放到了数线线和地址线组。

因此次只是单片DDR,不涉及拓扑结构。

此次设计并没有同层同组,而是把数据线放在第一层和第三层,主要做了等长

同层同组的目的主要是为了等长:信号不在不同的层传输速度不一样,另外在不同的层,因为有的有过孔,有的可能没有过孔,过孔的长度和厚板以及过孔穿到哪一层有关,所以过孔的长度也会影响信号的长度,这次是放在第一层和第三层,第一层和第三层中间的PP一般比较薄,如下图,只有3.2mil,所以影响长度有限。另外因为层不一样导致的传输速度不一样,只要把等长误差做到10mil以内就不用考虑了。

| 层名 | 介质 | 厚度(mil/OZ) |

|---|---|---|

| L1 | Copper | 1.4mil/成品铜厚1oz |

| PP | FR4 | 3.2mil |

| L2 | Copper | 1.2mil/1.0oz |

| CORE | 5mil | |

| L3 | Copper | 1.2mil/1.0oz |

| PP | 37.3mil | |

| L4 | Copper | 1.2mil/1.0oz |

| CORE | 5mil | |

| L5 | Copper | 1.2mil/1.0oz |

| PP | 3.2mil | |

| L6 | Copper | 1.4mil/成品铜厚1oz |

总结:

平时都要求DDR走线同层同组,根本原因是等长。

同层的原因:信号在内层和外层传输速度不一样,所以要尽层同层。

同组的原因:是为了设计好设计规则。方便看规则。只要能检查到,不同组也是可以的。

下方D8-D15,有的是走在第一层,有的是走在第三层,实测没有问题!

-

DDR3

+关注

关注

2文章

276浏览量

42239 -

cpu

+关注

关注

68文章

10854浏览量

211567 -

DDR

+关注

关注

11文章

712浏览量

65318 -

高速信号

+关注

关注

1文章

225浏览量

17694

发布评论请先 登录

相关推荐

ddr4和ddr3内存的区别,可以通用吗

基于FPGA的DDR3多端口读写存储管理的设计与实现

基于Digilent介绍DDR3和mig

DDR3内存或退出市场三星等大厂计划停产DDR3内存

Virtex7上DDR3的测试例程

FPGA学习-DDR3

基于AXI总线的DDR3读写测试

DDR3的原理和应用设计

DDR3的原理和应用设计

评论