本文导读

ADC的主要参数指标分为静态参数和动态参数两类,基于这两类指标,本文将对先楫半导体HPM6750 MCU片内16位ADC的精度进行全面测试,一起看看结果怎么样。

ADC参数测试原理

1.1ADC参数

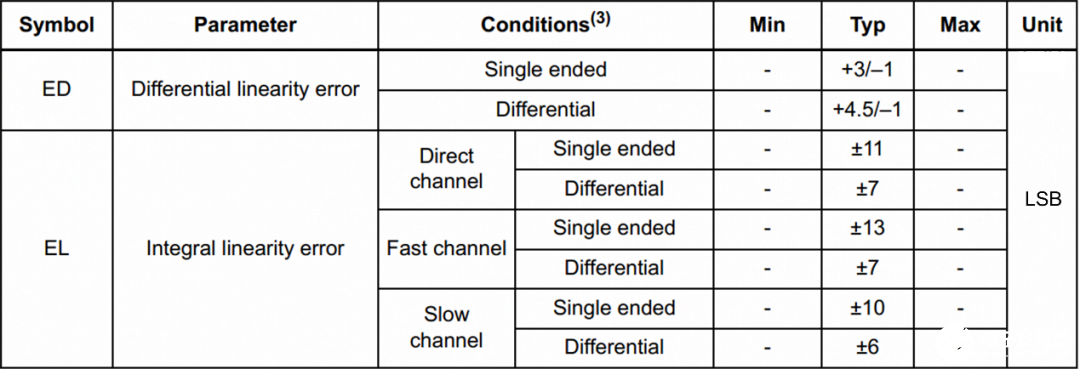

国内16位SAR型ADC芯片目前较少,MCU内置16位SAR型ADC的则更少。如何衡量ADC的性能,参考S*公司带有16位ADC的MCU芯片S**32H750手册,分为静态参数、动态参数两部分,如表 1.1、表 1.2所示。

静态参数主要有差分非线性(DNL)、积分非线性(INL),衡量ADC测量直流及低频信号时的性能。

表 1.1 ADC的静态参数(S**32H750)

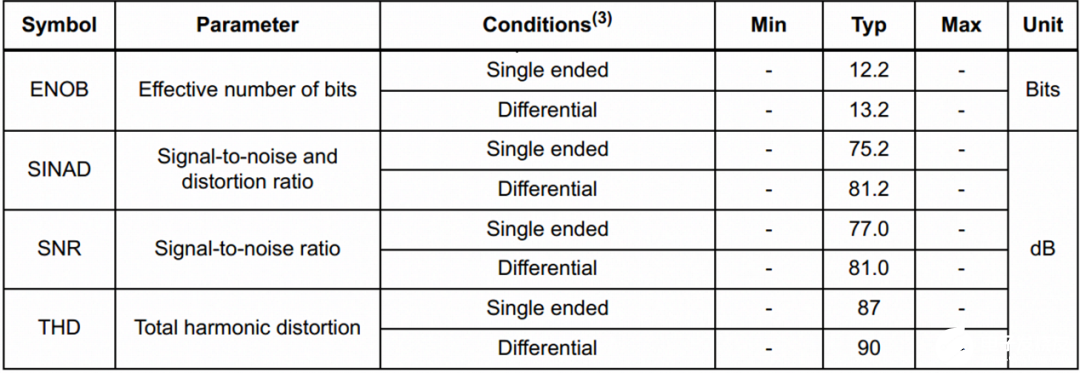

动态参数主要有有效位数(ENOB)、信噪失真比(SINAD)、信噪比(SNR)、总谐波失真(THD),衡量ADC测量交流动态信号时的性能,例如测试1KHz正弦波。

表 1.2 ADC的动态参数(S**32H750)

1.2 IEEE1241标准

IEEE1241对ADC器件的指标参数和测试方法进行定义,是一种为ADC器件厂家制定的标准。ADI和TI等厂家的独立ADC芯片、MCU厂家的片内ADC,均遵循该标准的方法,进行静态参数和动态参数的测试。

IEEE1241于2000年发布,较新的版本为IEEE1241-2010。ADC测试评估的主要任务是确定其电压传输关系,理想情况下输入电压与ADC输出代码中点的传输关系是一条直线,每个输出代码的宽度相同。实际的电压传输关系不同于理想情况,IEEE1241标准给出了几种可选的测试步骤和方法。一种方法是使用斜坡电压信号,通过复杂的伺服环路系统,使用比被测ADC分辨率高得多的DAC,精确步进,得到被测ADC各个LSB的实际跳变电压。

另一种方法是使用正弦波信号,该信号必须具有比被测ADC预期信噪失真比(SINAD)至少高20 dB的总谐波失真和噪声。例如,一个理想16位ADC具有98dB的信噪比(SNR),假设没有失真,那么SINAD就为98dB。要想对该ADC进行测试,要求使用一个-118dB以上THD+N的正弦波信号。该低失真正弦信号,可以通过多阶带通滤波器实现,硬件相对简单。因此使用正弦波信号,是目前主要的ADC测试方法。

EEE1241标准的各章节中,给出了基于正弦波信号和统计直方图,实现静态参数DNL、INL,动态参数ENOB、SINAD、SNR、THD的测试方法和计算公式。

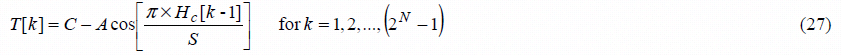

【6.4节】给出ADC电压传输关系的测试方法。使用一个幅度稍微超过ADC测量范围的纯正正弦波,输入到ADC,获取多个连续的采样数据并统计直方图,由公式(27)计算电压传输关系。

其中,T[k]是第k个二进制代码对应的电压值,Hc[k-1]是累计直方图,S是总采样点数。该节还给出了正弦波频率和ADC采样频率的选择,每次采集的数据点数,总的采集数据点数,正弦波幅度过载量要求。

【7.4.1节】给出增益误差G、失调电压Vos的测试方法和计算公式,基于对T[k]的最小二乘法拟合。

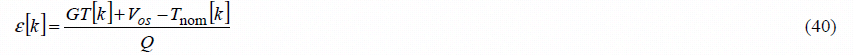

【8.2节】给出积分非线性INL的测试方法。测量值T[k]校正增益和失调误差之后,与理想值Tnom[k]相减,它们的差值代入公式(40),计算输出码k处的积分非线性ε[k]。

由公式(40)将LSB单位的INL,换算成百分比形式。

【8.4节】给出差分非线性DNL的测试方法,由公式(43)计算。当DNL[k]<0.9时,输出码k被定义为缺失码(missing code)。

【8.8节】给出总谐波失真THD的测试方法。ADC 对周期信号进行采样时,动态误差和积分非线性都会导致谐波失真,总谐波失真用于量化此类影响。总谐波是指一组目标谐波分量的均方根值(二次、三次等)与所施加信号均方根值的比值,由公式(50)计算。

该节给出了目标谐波的次数要求,由输入正弦波的最低9个谐波组成,包括第2次到第10次。用于计算的采样数据中,应该包含整数个输入正弦波周期,以最小化频谱泄漏,例如10个整周期。

【9.2~9.4节】给出SINAD、SNR、ENOB的测试方法。将指定频率和幅度的纯正正弦波输入到ADC,首选幅度接近满量程的大信号,但是不能出现削波(例如95%FS信号)。首先计算噪声和失真NAD,通过计算测量数据波形的DFT频谱,从频谱中删除直流和测试频率处的分量后,所有剩余傅立叶分量的和方根是NAD,由公式(67)计算。

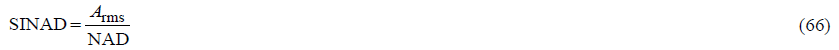

通过将NAD和Arms代入公式(66),计算SINAD。

通过将NAD、Arm、THD代入公式(69)和(68),计算SNR。

通过将NAD代入公式(70),计算ENOB。其中εQ是理想的量化误差rms值,等于LSB/√12。

根据IEEE1241标准的以上计算过程和公式,编写科学计算软件代码,可以实现各参数的测量。

测试环境搭建

2.1 硬件框图

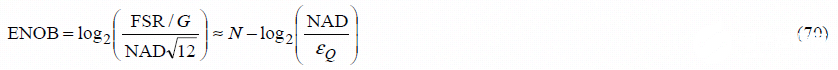

ADC测试的硬件由正弦波信号源、HPM6750测试板、USB转TTL线、U盘等组成,如图 2.1所示。正弦波信号源通过SMA连接线,连到HPM6750测试板。

图 2.1 测试环境硬件框图

静态参数测试时,需要大量采样数据,采样数据先存储在HPM6750测试板的内存中,之后多份采样数据存储到U盘中。动态参数测试时,需要的采样数据较少,采集完成之后直接通过HPM6750的UART打印,由TTL转USB线传输到电脑进行计算。

电脑上需要的软件工具如表 2.1所示。

表 2.1 测试所需的软件工具

2.2 正弦波信号源

用于测试的正弦波信号需要具有比被测ADC预期信噪失真比(SINAD)高20 dB左右的总谐波失真和噪声。一个理想16位ADC具有98dB的信噪比(SNR),如果没有失真,SINAD为98dB。因此,需要一个-118dB以上THD+N的正弦波信号对16位ADC进行测试。

本测试使用TI 的PSIEVM精密信号注入器,板上有8阶带通滤波器生成低失真正弦波,THD参数为-123dB,以符合测试要求。PSIEVM板如图 2.2所示,它的正弦波输出频率固定为2KHz,输出幅度和直流偏移电压可调,配套有PC端的GUI界面进行设置。

图 2.2 正弦波信号源PSIEVM板

需要注意PSIEVM板的输出阻抗,需要手工改成50Ω。

2.3 外围电路要求

HPM6750片内ADC的外围电路设计,对保证ADC的信噪比,至关重要。SAR型ADC可以等效理解为一个多输入端口的比较器,vwin 电源AVDD、基准输入VREFH、接地平面、输入通道上的噪声直接影响ADC输出代码的跳动。

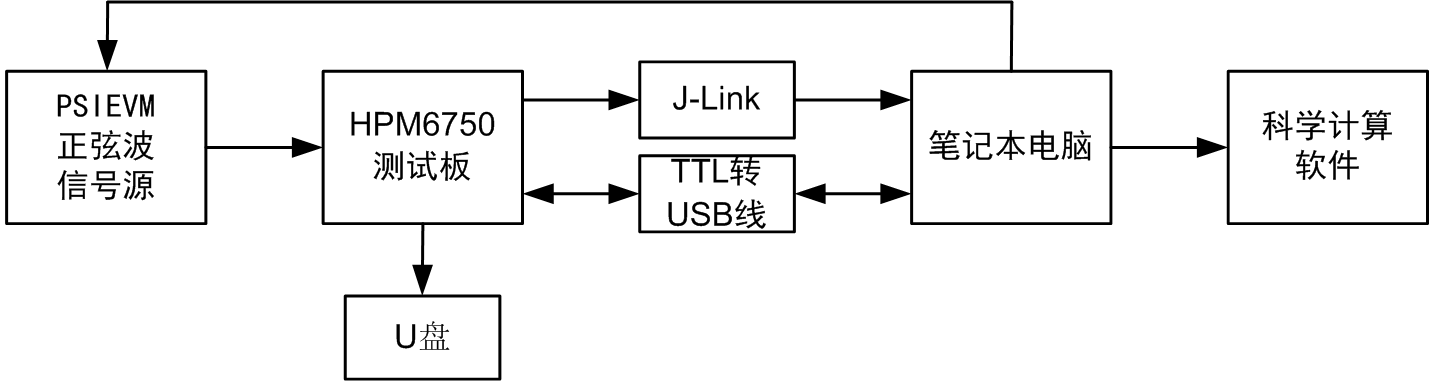

本测试使用专用的HPM6750测试板,如图 2.3。

图 2.3 HPM6750测试板

HPM6750测试板的ADC外围电路处理方式如下文所述,硬件设计时建议参考处理。

【模拟电源AVDD】通过LDO从数字电源5V获得低噪声模拟电源。需要注意LDO的电源抑制比在10kHz及以上频率时下降,导致高频纹波和尖峰噪声仍可以传导至LDO输出。建议在LDO之前加入10Ω左右电阻和磁珠与输入端10uF左右电容,形成低通滤波,滤除高频纹波与尖峰噪声。

【基准VREFH】基准电路设计包括两部分:电容选取、基准噪声。VREFH管脚位置的大电容是片内SAR型ADC的一部分,此类ADC基于开关电容电荷重新分配原理,在确定输出代码LSB过程中,需要从VREFH管脚获得瞬态电荷。例如,使用了两个10uF的X5R材质低ESR陶瓷电容和104电容并联,并且在PCB布局时以尽量短的走线和覆铜连接到VREFH管脚,电容的接地焊盘需要就进放置多个过孔至PCB接地平面,以降低连接阻抗。

基准的噪声需要选择低噪声基准。例如,使用了低成本的AZ432搭建3.1V基准,低频噪声10uVpp,典型温漂20ppm。对温漂有更高要求时,可以选用TPR3525,低频噪声50uVpp,典型温漂10ppm。

【接地平面】AGND和VREHL管脚需要就近放置过孔,连接到接地平面。PCB布局时需要把模拟器件、数字器件分区域放置,引导数字信号的开关电流不流经模拟电路的低平面,以避免串入数字开关噪声。详细地平面设计说明参考资料[6]。

【输入通道】需要注意,本测试中输入通道不能有普通电容,普通电容的容量随输入电压变化,使得低通截止频率变化,会引入明显失真。正常使用时,输入通道需要限制信号带宽,例如加入RC低通滤波,限制宽带噪声。

使用以上处理,HPM6750测试板的测试数据详见5.1节的表5.1。

静态参数测试

3.1 测试条件

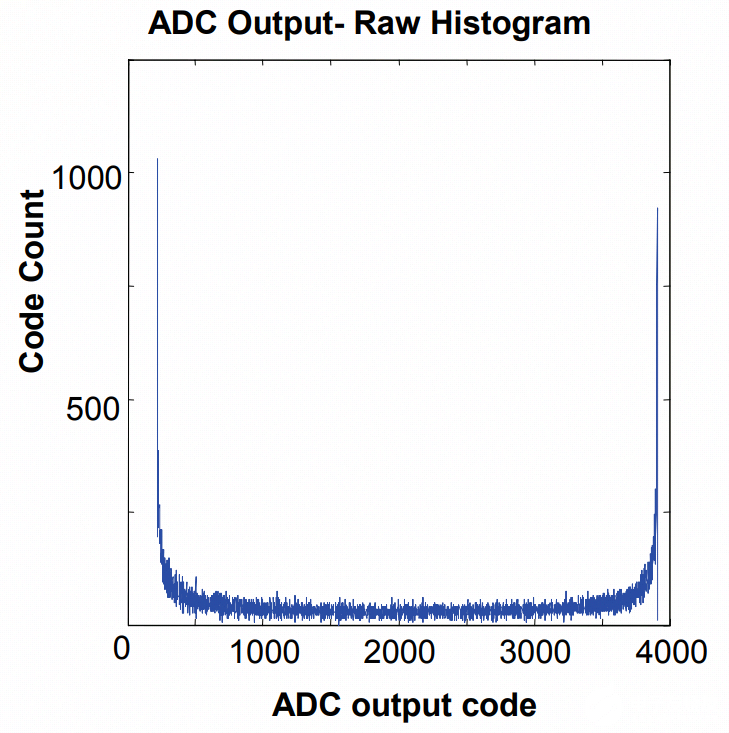

使用正弦波输入信号,基于概率密度原理和累计直方图测试DNL、INL。当输入信号是理想正弦波时,ADC以固定频率采集,所输出数字代码的出现概率,理论上为固定值,如图 3.1所示。出现概率通过某一数字代码的出现次数,除以总采样点数计算。各个输出数字代码的测试出现概率,与理想出现概率之间的差值,是这个代码的宽度误差。统计最大宽度误差,得到差分非线性DNL。得到DNL之后,DNL的累计误差是积分非线性INL。

图 3.1 正弦波输入时的ADC输出代码直方图

图 3.1的直方图高度非线性,不能直接计算,通过累计直方图实现积分计算,可以实现直方图线性化(参考资料[3])。IEEE1241标准6.4、7.4、8.2、8.4节,给出了以上基于正弦波信号和概率密度直方图方法的计算过程、公式、及测试条件。

结合IEEE1241中6.4节要求,本测试实际使用测试条件设置如图 3.1所示。

表 3.1 静态参数测试条件

【输入信号幅度】IEEE1241的6.4节描述,输入信号幅度需要轻微超出ADC测量范围,过载量根据输入噪声而定。因为在输入正弦波的波峰、波谷位置,ADC两个临近输出代码对应的输入电压差小,容易受噪声影响。本测试中,选用10%过载量,根据ADC输入范围0~3.1V,PSIEVM输出正弦波幅度设置为-0.3~3.4V,offset设置为1.55V。

【ADC采样速率】IEEE1241的6.4.1节描述,采样速率和输入信号频率必须互为质数,实现均匀遍历到所有的ADC输出代码。本测试中,输入正弦波频率2KHz,采样速率664Ksps,每个周期获得332个采样点,具有332个不同输出代码,通过小数位频率和大量采样点,实现均匀遍历所有的输出代码。

【采样点数】IEEE1241的6.4.1节描述,每一次采集的连续采样点数,包含整数个输入信号周期。这样保证每次的采样点在0~2π的相位上均匀分布。因为会使得多次采集的数据进行拼接时,输出代码的出现概率均匀分布。本测试中,每次采样点数约120K。

IEEE1241的6.4.3节描述,根据概率密度进行测试时,样本数量与测试精度、置信度的计算公式。本测试中使用大约30M采样点进行计算,存储在U盘中。

3.2 测试步骤

静态参数测试时,单次的连续采样数据,MCU先存储在HPM6750测试板的内存中,然后顺序存到U盘中,将多份采样数据拼接成几十兆采样点的数据记录文件,用于参数计算。测试的步骤如下。

(1) PC上位机设定正弦波信号源PSIEVM的频率频率、幅度、失调,使能输出;

(2) Segger Embedded Studio环境中启动ADC采集数据,并存储到U盘;

(3) U盘中的数据记录文件复制到电脑,数据文件的路径写入科学计算软件;

(4) 运行科学计算软件代码计算DNL、INL;

(5) 查看科学计算软件输出的图表和数据。

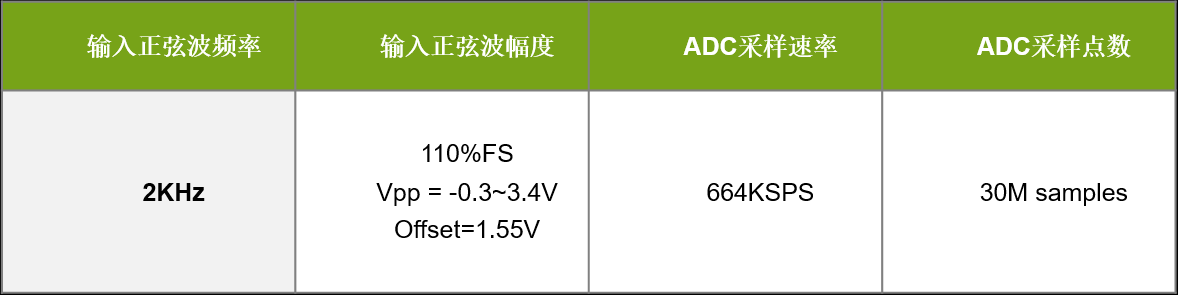

3.3 测试数据

本测试中从U盘读取的33M采样数据文件大小为128MB,导入科学计算软件获得的输出代码直方图如图 3.2所示,其中横轴X为ADC的输出代码值,纵轴Y为该代码的出现次数,以对数坐标显示。可以看到图 3.2包含了0~65535个输出代码,符合16位ADC的输出代码个数。

图 3.2 采样数据直方图

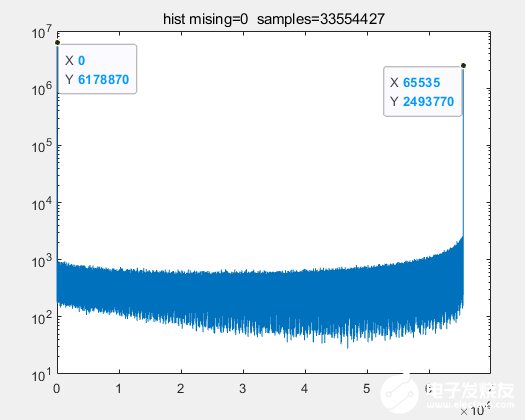

3.3.1 DNL

采样数据通过科学计算软件计算得到的DNL,如图 3.3所示,DNL最大值为+1.1~-0.92LSB。

图 3.3 DNL测试数据

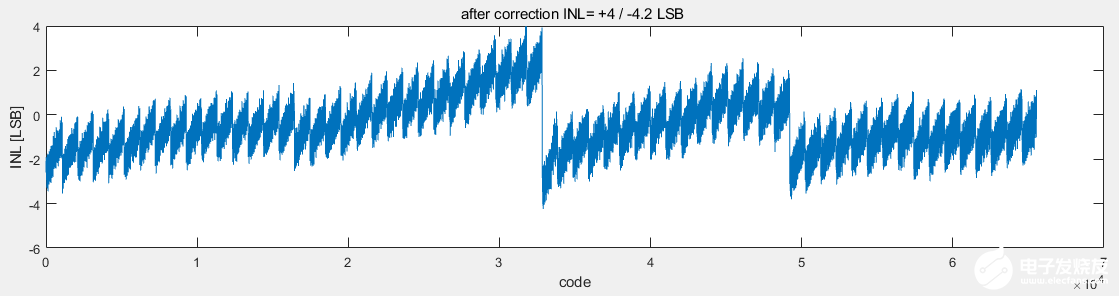

3.3.2 INL

采样数据通过科学计算软件计算得到的INL,如图 3.4所示,INL最大值为+4~-4.2LSB。

图 3.4 INL测试数据

3.3.3 小结

根据以上测试数据,HPM6750片内16位ADC测得DNL为+1.1/-0.92LSB,INL为+4/-4.2LSB。

动态参数测试

4.1 测试条件

使用正弦波输入信号,基于FFT频谱分析,从频谱成分计算出SINAD、ENOB、SNR、THD参数。将噪声和谐波成分等效到ADC输入端,根据理想ADC的信噪比公式,可以得到有效位数ENOB。IEEE1241的9.2~9.4节,描述基于FFT方法的ENOB等参数计算过程、公式、及测试条件。

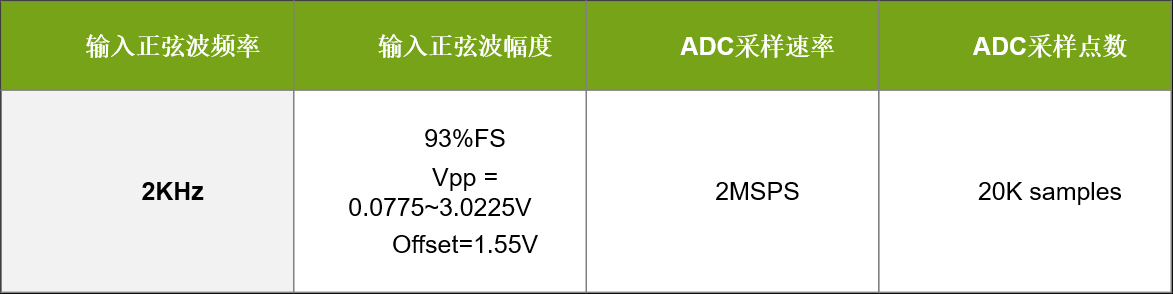

结合IEEE1241要求,本测试实际使用测试条件设置如表 1.1所示。

表 4.1 动态参数测试条件

【输入信号幅度】IEEE1241的9.2.3节描述,输入信号幅度接近ADC的满量程,但是不能出现削波。因为信噪比SNR和失真THD直接和输入信号幅值相关,但是幅度过大,接近削波时,将出现明显失真。本测试中选用93%FS,根据ADC输入范围0~3.1V,PSIEVM输出正弦波幅度设置为0.0775~3.0225V,offset设置为1.55V。

【采样速率】IEEE1241的9.3节描述,可选相干采样,或非相干采样加窗。本测试中选用后者,为了衡量ADC性能,采样速率选用最高值2MSPS。

【采样点数】IEEE1241的9.4.3节描述,采样点数增加时,随机噪声对正弦波测试结果的影响降低,可重复性更好。采样点数不应过多,以免正弦波信号源或ADC时钟信号中的频率漂移或相位噪声影响结果。本测试中选用20个整周波采样点数,即20K samples。

4.2 测试步骤

动态参数测试时,采样数据需要较少,ADC采集20个输入信号周期的连续数据,采集完成之后通过HPM6750的UART打印,通过TTL转USB线传输到电脑进行计算。

(1) PC上位机设定正弦波信号源PSIEVM的频率频率、幅度、失调,使能输出;

(2) Segger Embedded Studio环境中启动ADC采集数据,并通过UART打印;

(3) 采样数据文件的路径写入科学计算软件;

(4) 运行科学计算软件代码计算ENOB等参数;

(5) 查看科学计算软件输出的图表和数据。

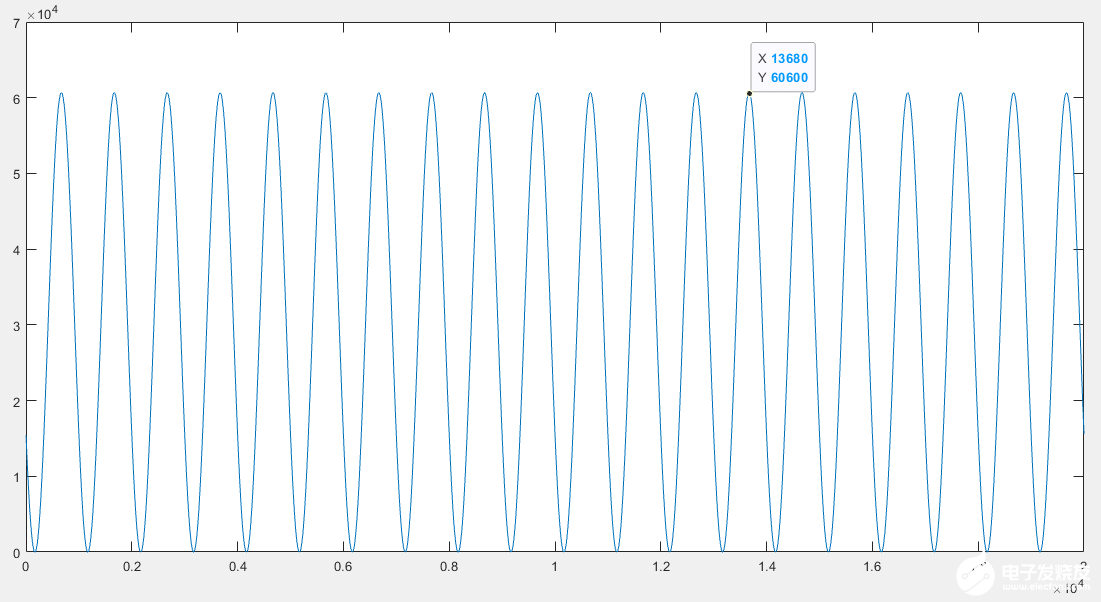

4.3 测试数据

本测试中从UART打印20K点数据,导入科学计算软件看到的原始数据波形如图 4.1所示,可以看到波形幅值接近满量程。

图 4.1 动态参数测试数据的原始波形

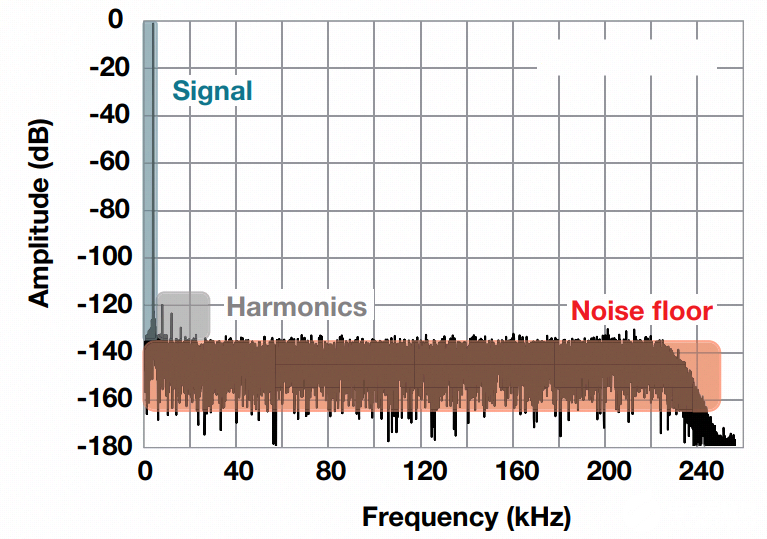

4.4 ENOB、SINAD、SNR、THD

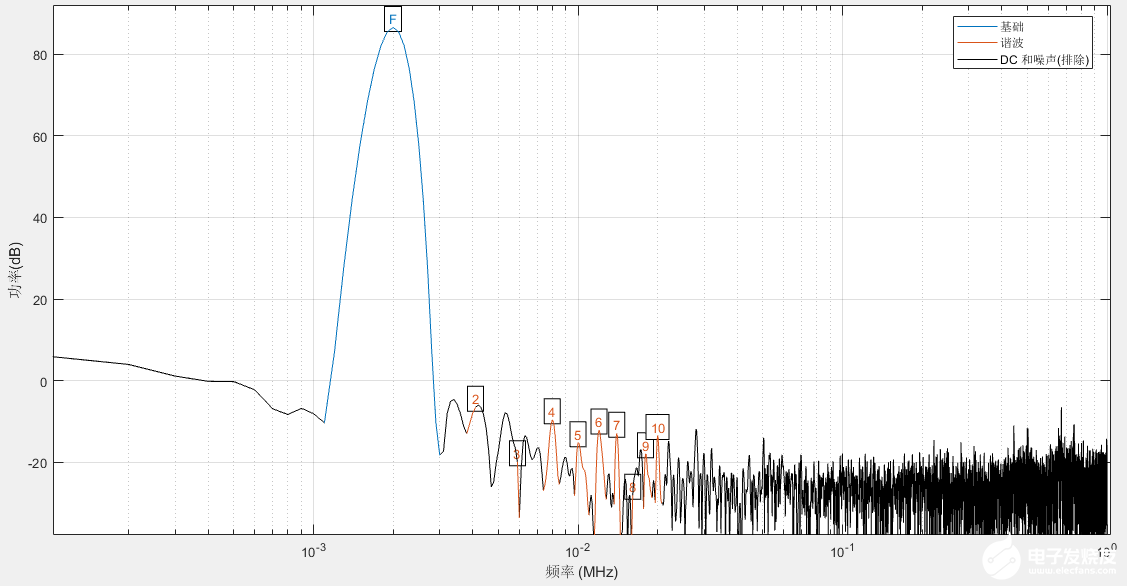

通过科学计算软件计算输出的频谱如图 4.2,蓝色是输入信号,红色是谐波,黑色是噪声。

图 4.2 动态参数测试数据的频谱

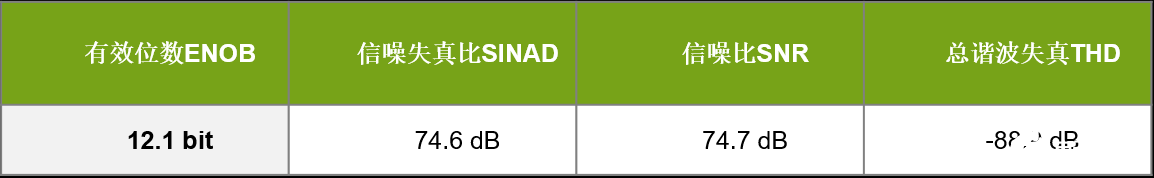

通过科学计算软件计算输出的动态参数值如表 4.2。需要注意动态参数测试与噪声相关,容易受干扰,需参考2.3节的描述仔细设计ADC外围电路。

表 4.2 动态参数测试数据

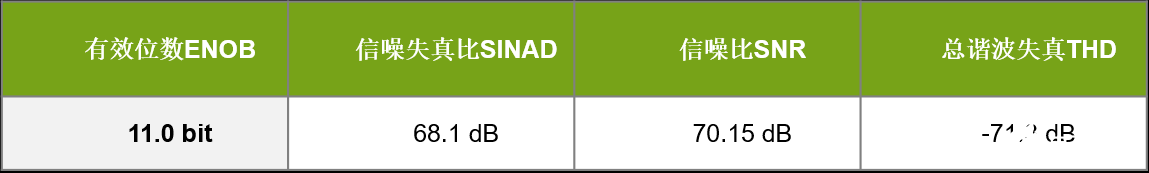

HPM6750片内16位ADC的采样速率最高可以设置至4MSPS,这种情况下的动态参数测试值如表 4.3。可以看到,ENOB等参数有一定幅度下降,需要更高采样速率而不是更高精度时,可以选择使用该设置。

表 4.3 动态参数测试数据(4MSPS)

4.5 小结

根据以上测试数据,HPM6750片内16位ADC在2MSPS最高采样速率下,测得ENOB为12.1位,SINAD为74.6dB,SNR为74.7dB,THD为-88.9dB。

采样速率最高可支持至4MSPS,测得ENOB为11位。

测试总结

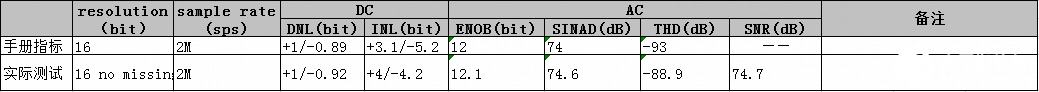

5.1 实测参数与手册参数对比

汇总以上测试数据,HPM6750片内16位ADC的静态参数和动态参数如表 5.1所示。表中与HPM6750手册中的参数进行了对比,可以看到实测参数基本与手册符合。

表 5.1 实测参数与手册参数

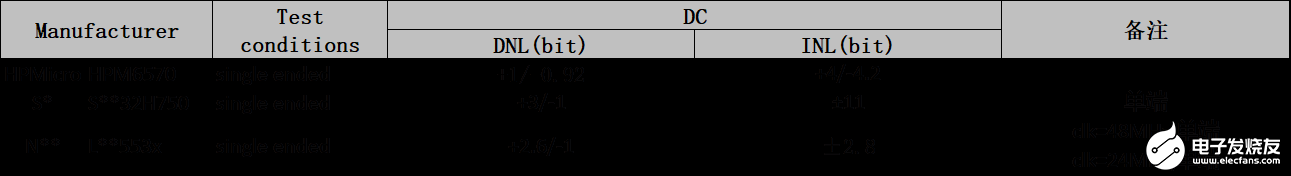

如下表,静态参数部分与国外领先厂家的同类型SOC片内16位ADC参数进行对比。HPM6750的静态参数较好,DNL优于对比型号。INL约为±4LSB,优于S**32H750,与Lxx553x接近。

表 5.2 与国外厂家的静态参数对比

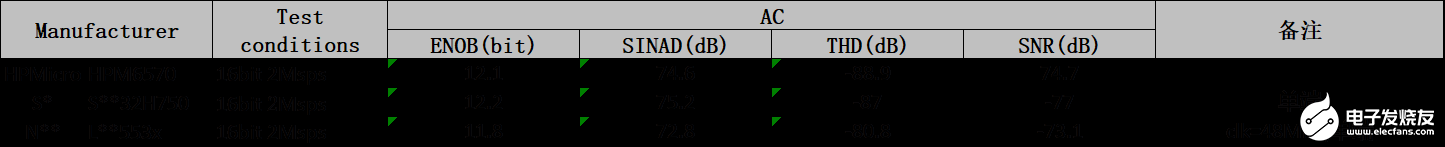

如下表,动态参数部分与国外领先厂家的同类型SOC片内16位ADC参数进行对比。HPM6750的动态参数与对比型号基本在同一水平,ENOB为12.1位,S**32H750为12.2位,Lxx553x为11.8位。

表 5.3 与国外厂家的动态参数对比

通过以上对比,HPM6750片内16位ADC的实测数据具有与同类型号S**32H750、Lxx553x几乎等同的性能,ENOB有效位数为12位,INL较好约±4LSB。

5.2 有效位数的区别

对于高分辨率ADC,关注实际能做到多少位,但是大部分情况下不具备搭建IEEE1421中正弦波测试环境的条件,测试有效位数ENOB。通常使用测量DC电压的方式,统计输出数据不跳动的位数,检查ADC的无噪声分辨率NFR。需要区分无噪声分辨率NFR,不等同于手册中的有效位数ENOB。NFR是测量直流或低频信号时,所关注的不跳动位数,而ENOB是测量交流动态信号关注的有效位数。NFR测量的是噪声的峰峰值,但没有包括ADC的非线性,ENOB测量的是噪声的均方值,还包括了ADC的非线性。高速ADC的手册中通常只标注动态参数ENOB,没有标注NFR,但是在ADC的非线性远小于噪声的峰峰值的情况下,可以从动态参数ENOB,估算能够获得的NFR。

【无噪声分辨率NFR的测试方法及计算】无噪声分辨率衡量ADC能够测量到最小直流信号,测试方法:输入端接地,或连接到一个通过大电容深度去耦低噪声的直流电压,然后采集大量采样点,并将其表示为直方图。外围电路设计良好时,等效到ADC输入端的噪声为白噪声,直方图呈正态分布。直方图的代码分布个数,表示峰峰值噪声,对应无噪声分辨率。

【有效位数ENOB的测试方法及计算】有效位数衡量ADC能够测量到的最小交流信号。测试方法:输入正弦信号,对采样数据进行FFT分析,计算所有噪声(包括量化噪声)和失真项的和方根值SINAD,并等效为ADC输入噪声,代替SNR,根据理想N位ADC的理论SNR公式,换算位数N。

SNR = 6.02N + 1.76dB

【通过ENOB估算NFR】根据参考资料[5],针对交流输入信号的ENOB,与直流低频信号的无噪声分辨率NFR,有如下的换算关系:

ENOB = NFR+0.92

对于直流低频信号,ADC的ENOB约比NFR大1位(0.92位)。但是以上计算过程,没有考虑ADC非线性,外围电路噪声、以及输入信号噪声影响,是理想情况下能获得的无噪声分辨率NFR。实际电路中,NFR与外围电路直接相关,ADC外围AVDD管脚、VFEFH管脚、接地平面,以及直流输入信号自身的噪声,均会直接影响ADC输出代码跳动,需要仔细设计外围电路和PCB(参考资料[6]),才能获得预期的无噪声分辨率。

测量直流低频信号时,除了硬件措施,对高速ADC输出代码做数字平均滤波,是提高无噪声分辨率的有效方法。HPM6750片内16位ADC,做数字平均之后的无噪声分辨率如表 5.4所示。被测的信号是一节1.5V干电池,可以看到平均4次之后,NFR为11位以上;平均32次之后,NFR为12位以上。

表 5.4 HPM6750数字平均之后的无噪声分辨率

来源:立功科技

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50711浏览量

423102 -

mcu

+关注

关注

146文章

17123浏览量

350956 -

半导体

+关注

关注

334文章

27286浏览量

218023 -

adc

+关注

关注

98文章

6495浏览量

544441

发布评论请先 登录

相关推荐

HPM6750 MCU片内16位ADC的精度进行全面测试

如何使用CodeViser调试先楫HPM6750开发板?

HPM6750开发环境搭建及快速上手

大神测评 | 结果出乎意料! 先楫HPM6750 CoreMark 跑分测试

HPM6750 LVGL刷屏性能再提升?大神网友开辟片内新天地

HPM6750测评|体验极致的运行速度和开发速度

测评分享 | 150fps !HPM6750 LCDC 刷屏毫无压力

双剑合璧 !看HPM6750 如何赋能 ADS1263 实现32位高精度数据处理

测评分享 | HPM6750 能跑 openmv 啦!

测评分享 | 首尝HPM6750运行边缘AI框架(含TFLM基准测试)

【深度测评】HPM6750 MCU片内16位ADC精度测试

【深度测评】HPM6750 MCU片内16位ADC精度测试

评论