有客户开发LPC54608做产品,已经到量产阶段,最后想把固件配置为禁止ISP boot功能,禁止SWD功能。

客户看了手册(UM10912)中有关配置加密的章节: Chapter 43: LPC546xx Enhanced Code Read Protection(ECRP),看完之后还是有一些疑问。现场工程师让我帮忙看看,感觉手册里确实写的有点雾里看花,不容易参透。

LPC546xx出了好多年了,网上一搜竟然没有把ECRP写的特别细,特别明白的文章。

好在有大神同事的指点和PPT支持,今天这篇文章就将ECRP扒个底朝天!

ECRP是啥?

ECRP全称为Enhanced Code Read Protection。 直译过来就是”高级代码保护机制”。

这个高级对应之前的CRP(用在LPC546xx之前的LPC产品上)。 所以ECRP就算是CRP的升级,功能更强大。作用嘛:就是给代码提供保护啦,比如设置为Flash不可读,禁止ROM bootloader、禁止调试口之类的。

每个厂家的MCU都会有类似的配置,大同小异。没啥新鲜的,相信大家都接触过类似的机制。

ECRP可以实现:

Protect FLASH from ISP Erase/Write(禁止/使能ISP擦写Flash)

Protect FLASH from IAP Erase/Write(禁止/使能IAP擦写Flash)

ISP Entry from bootloader(禁止/使能 进入ROM bootloader)

ISP Entry from IAP call(禁止/使能 在程序中调用ROM API )

SWD Enable/Disable(禁止/使能 调试接口)

ECRP本身在手册中的描述还好,比较清晰,但主要是ECRP的这些功能还和OTP模块耦合。两者共同作用来决定最终的芯片保护行为,这块内容手册写的不多,总有一种”我似乎懂了但是有些地方好像又没有懂”的尴尬。

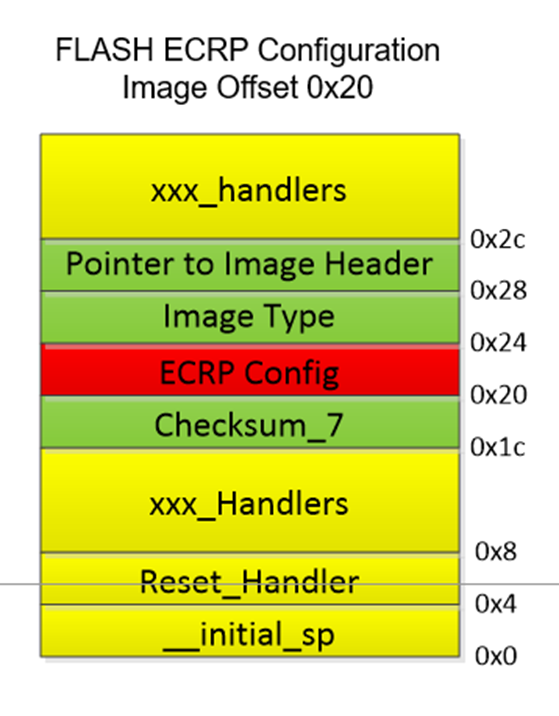

FLASH ECRP的位置

ECRP的位置在中断向量表的0x20位置,就是一个uint32_t,类似一个特殊寄存器,往里面写不同值来决定保护行为(直接修改.s文件中的中断向量表0x20位置数据就可以)。

FLASH_ECRP有定义的部分只占0-17位,其他位保留。默认出厂时,其值为0xFFFF_FFFF(Flash全擦就是1嘛)。

具体的位段定义请参考手册。这块手册写的挺清楚的。

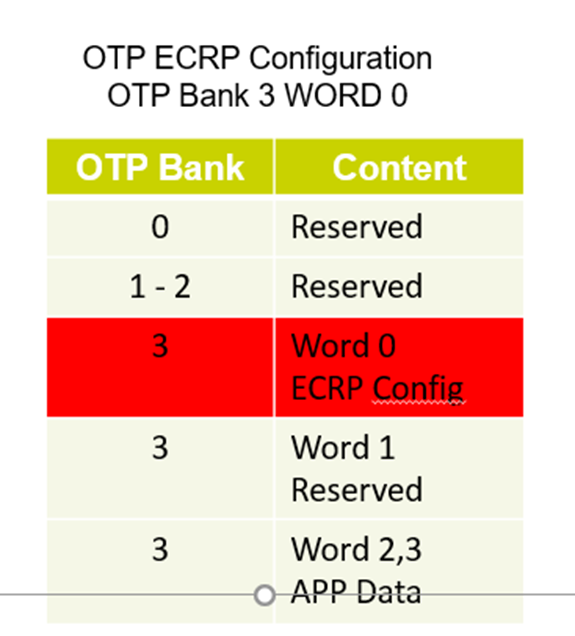

OTP ECRP的位置

OTP是一段特殊的非易失存储器,只能被编程1次。默认为全0.位置如下图:

OTP不是Flash,也不和Flash统一编址,只能由IAP函数来写入,且只能写一次。

可以看到它由3个Bank组成,我们只关心Bank3。Bank3又由3个word组成,word0也叫做ECRP。

我们姑且叫他OTP_ECRP。于是,我们把Flash地址0x20那个ECRP重命名叫做FLASH_ECRP。

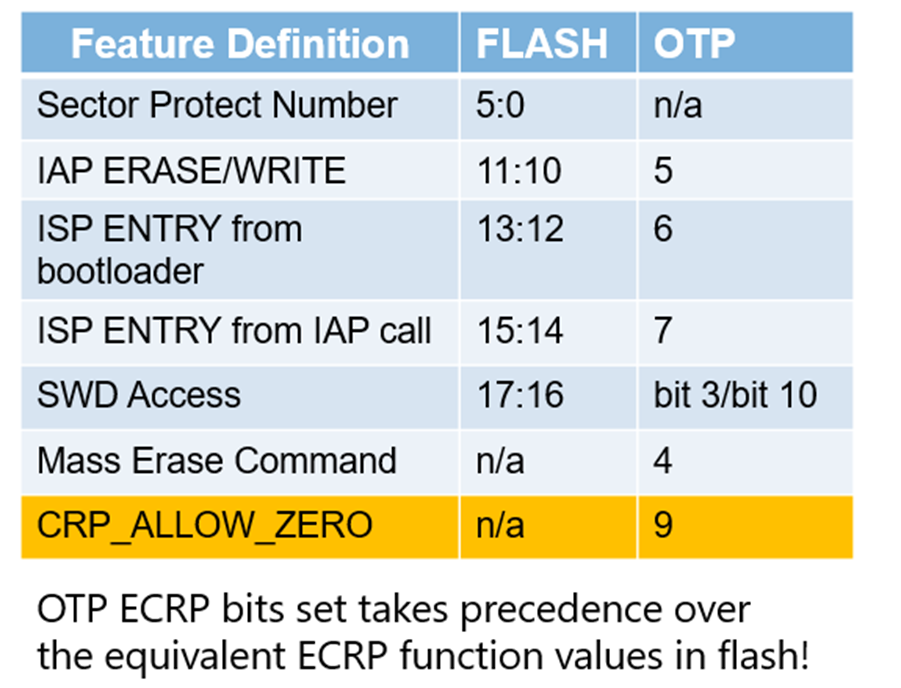

OTP_ECRP和FLASH_ECRP的值,共同决定芯片代码保护行为

FLASH_ECRP 和OTP_ECRP都具有一些相同的行为控制功能,但是!但是!他们的位定义却不一样(需要特别留意),如下表所示:

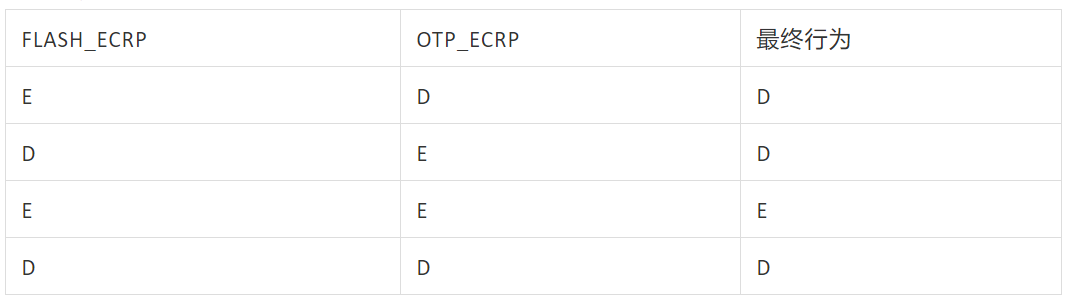

另外,芯片最终的代码保护行为是到底是听OTP_ECRP还是FLASH_ECRP呢? 答案是优先OTP_ECRP的设定,并且优先采取更严格的设定,举个例子:比如ISP ENTRY from bootloader这个功能,结果如下表:

(E代表使能功能,D代表禁止功能)

最后,FLASH_ECRP还有2个特殊值,被定义如下:

所以FLASH_ECRP默认的值0xFFFF_FFFF才能被识别为最低限制(使能所有功能,不进行任何保护)。

来源:恩智浦MCU加油站

审核编辑:汤梓红

-

mcu

+关注

关注

146文章

17123浏览量

350980 -

寄存器

+关注

关注

31文章

5336浏览量

120230 -

ISP

+关注

关注

6文章

476浏览量

51800

发布评论请先 登录

相关推荐

LPC546xx加密配置-ECRP详解

LPC546xx加密配置-ECRP详解

评论