随着科技的飞速发展,芯片已经成为现代社会不可或缺的组成部分。无论是手机、电脑、平板,还是智能家居、物联网设备,芯片都是这些产品的核心。而在这个过程中,芯片制程技术的发展起到了举足轻重的作用。从最初的毫米级制程,到现在的纳米级制程,芯片制程技术的每一次进步都推动了半导体产业的飞跃。

在 20 世纪 60 年代,芯片制程技术还处于起步阶段,当时的制程尺寸达到了 10 微米。这种毫米级的制程技术虽然较为粗糙,但已经为计算机和通信设备的小型化奠定了基础。随着半导体技术的发展,科学家们开始研究如何减小制程尺寸,以提高芯片的性能和集成度。

到了 70 年代,芯片制程技术进入了微米级时代。这时的制程尺寸缩小到了 5 微米,甚至 3 微米。微米级制程技术的出现,使得芯片性能得到了显著提升,功耗也得到了有效控制。在此期间,***技术也得到了发展,从最初的接触式曝光发展到了投影式曝光,为芯片制程的进一步缩小提供了可能。

进入 80 年代,芯片制程技术继续向更高精度发展。1987 年,IBM 公司成功研发出了 1 微米制程技术,这标志着芯片制程进入了亚微米级时代。亚微米级制程技术的应用,使得芯片性能大幅提升,同时功耗也进一步降低。在这一时期,芯片制程技术的发展主要集中在缩短曝光时间和提高产率等方面。

90 年代,芯片制程技术迎来了又一重要突破——深亚微米级制程。此时期的制程尺寸缩小到了 0.5 微米,甚至 0.35 微米。深亚微米级制程技术的应用,使得芯片性能得到了更大的提升,同时功耗也进一步降低。此外,这一时期的芯片制程技术还开始采用低 K 材料和铜互连技术,以降低信号传输损耗,提高芯片性能。

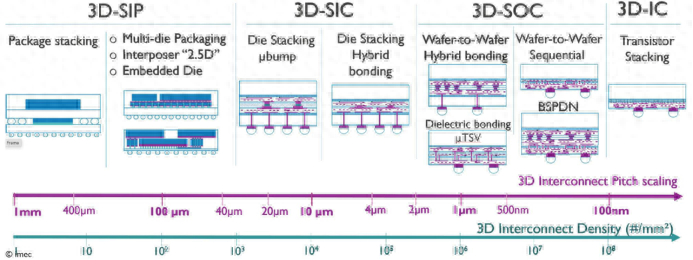

进入 21 世纪,芯片制程技术再次实现了重大突破,迎来了纳米级制程时代。2007 年,Intel 公司宣布成功研发出 45 纳米制程技术。此后,芯片制程技术不断缩小,从 45 纳米到 32 纳米,再到 22 纳米、14 纳米、7 纳米,甚至 5 纳米。纳米级制程技术的应用,使得芯片性能得到了空前的提升,功耗也大幅降低。在这一过程中,***技术也取得了重要进展,从传统的光刻技术发展到了极紫外(EUV)光刻技术,为更高精度的芯片制程提供了可能。

芯片制程技术的发展,是半导体产业不断追求更高性能、更低功耗和更高集成度的结果。从毫米级到微米级,再到亚微米级和纳米级,每一次制程技术的进步都为科技发展注入了新的活力。在未来,随着科技的不断创新,我们有理由相信,芯片制程技术将继续向更高精度、更高效率和更低成本的方向发展,为人类社会的科技进步贡献更多的力量。

-

纳米

+关注

关注

2文章

696浏览量

36976 -

通信设备

+关注

关注

3文章

337浏览量

32046 -

芯片制程

+关注

关注

0文章

51浏览量

4688

原文标题:芯片制程的发展:从毫米到纳米,人类智慧的结晶

文章出处:【微信号:快乐的芯片工程师,微信公众号:快乐的芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

人类智慧水平AI即将到来,AI芯片已提前布局

台积电2纳米制程技术细节公布:性能功耗双提升

台积电2纳米制程技术细节公布

EBSD与TEM在再结晶研究中的应用

SOC芯片的未来发展方向

纳米级材料尺寸测量:从微观到宏观,纳米精度,中图智造

释放前所未有的能效:瑞萨先进的110纳米制程技术

芯片制程的发展:从毫米到纳米,人类智慧的结晶

芯片制程的发展:从毫米到纳米,人类智慧的结晶

评论