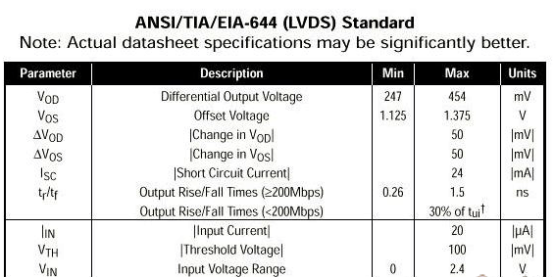

LVDS电平是根据ANSI/EIA/TIA-644定义的一种电平标准,其标准定义的相关参数如下:

图1 LVDS电平标准

标准参数的制定一方面取决于器件的制造工艺水平,另一方面取决于该标准面向的应用场景的性能要求。这意味着在不同的参数里,思考参数的取值的方法可能大相径庭。

- LVDS电平基本原理

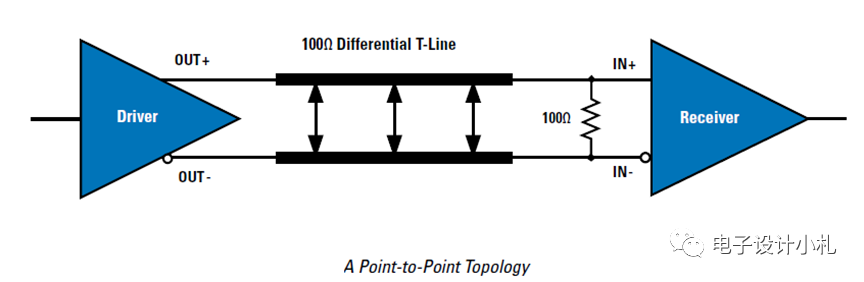

图2 LVDS发送和接收电路的结构

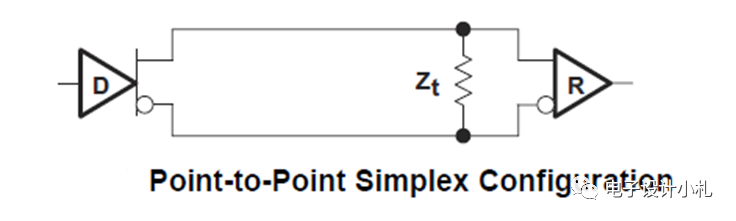

LVDS的发送电路一般为图2所示的全桥结构,当T1和T4导通时,发送侧输出的电流通过末端100欧姆的匹配电阻形成回路,此时电压上正下负;当T2和T3导通时,末端电阻的电流流向逆转,此时电压下负上正,LVDS即通过此来传输高低电平。另外,发送电路内部一般都会有直流偏置来提供共模电压。

2. 共模电压

LVDS电平标准对共模电压做了具体的要求,并且根据实际的芯片手册来看,输入输出对共模电压的要求并不一致,那么,共模电压有什么作用,为什么共模电压的要求会不一致呢。

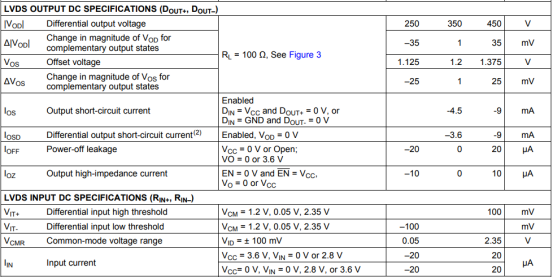

图3 SN65LVDS049 的输入输出参数

图3截取了SN65LVDS049 的相关参数,可以看到其输出共模电压是1.125V ~ 1.375V,输入共模电压为0.05~2.35V,两者相差较大,原因在于输出参数为性能要求决定,通过内部偏置电压,可以满足参数的要求,而输入参数则更多的由器件本身特性决定,它表示该器件可正常工作的一个范围。至于为什么是这么一个范围,则需要进一步分析。

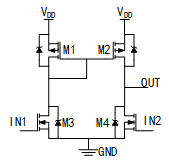

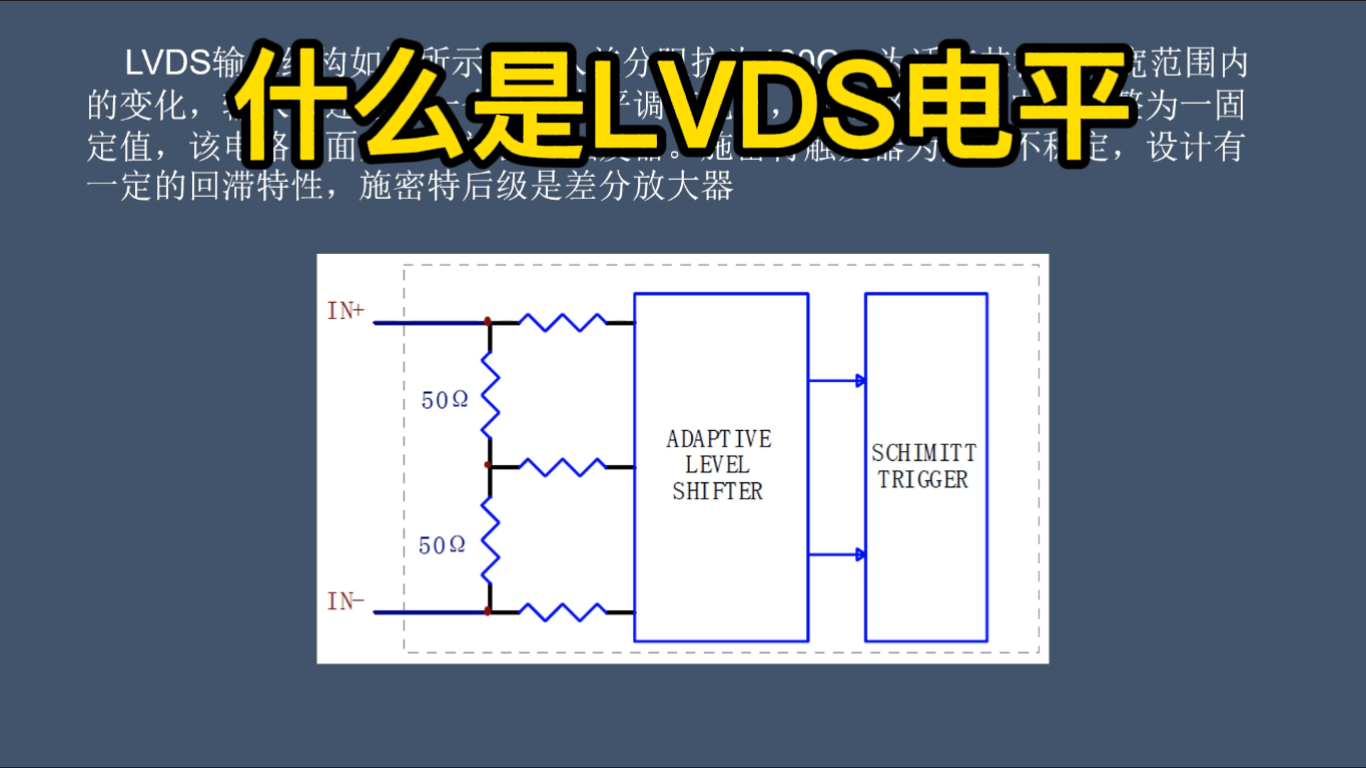

LVDS的接收器是一个运放,运放的输入级如图4所示。

图4 运放输入级的结构

M1和M2组成电流镜,为M3和M4组成的差分输入对提供有源负载。使用电流镜的原因是因为电流源的阻抗非常大,根据A v =gmR D ,理论上可以提供很大电压增益,并且电流源也可提供稳定的偏置电流,减小温度的影响。MOS管的跨导gm在饱和区较大且较为稳定,所以在放大电路中,MOS管一般工作在饱和区。为了满足这个要求,我们需要对MOS管的工作点进行设置,这也是共模电压的任务。

为了简化分析,假设MOS的开启电压为0,如若要使MOS管工作在饱和区,要满足V gd

Vcm -VDD -Von(sat)

即:

Vcm

显然,Vcm应大于Vth ,故有:

Vth

可见,输入共模电压的取值是比较宽泛的,所以,当输入电压的值较大,输入共模电压的值自然会升高。而输出共模电压的值是内部偏置电压决定的,两者存在差异是正常的。

- 终端电阻、偏置电流源以及输入门限电压

终端匹配电阻取值100ohm主要是为了阻抗匹配。从标准上看,偏置电流源的大小也是可以调节的,摆幅低时传输距离短,但是可以达到更高的频率,反之则传输距离可以变长但频率上限会降低。门限电压则可由器件工艺控制,是一个硬性指标。

-

运放

+关注

关注

47文章

1163浏览量

53062 -

lvds

+关注

关注

2文章

1043浏览量

65791 -

接收电路

+关注

关注

13文章

86浏览量

25142 -

电平标准

+关注

关注

0文章

4浏览量

6589 -

LVDS电平

+关注

关注

0文章

3浏览量

1632

发布评论请先 登录

相关推荐

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连

电平标准M-LVDS接口学习笔记

电平标准LVDS接口学习笔记

如何进行CAN与LVDS信号的电平检测

求助LVDS电平转HCSL的转换电路

LVDS信号电平特性

LVDS和CML与LVPECL的同种差分逻辑电平之间的互连教程

LVDS电平以及LVDS25电平能否约束到这个BANK上呢?

CML电平学习笔记

LVDS电平学习笔记

LVDS电平学习笔记

评论