1.什么是可控阻抗?

可控阻抗是由PCB迹线及其相关参考平面形成的传输线的特性阻抗。当高频信号在PCB传输线上传播时,它是相关的。控制阻抗对于解决信号完整性问题,即无失真的信号传播。

电路的阻抗由PCB的物理尺寸和介电材料决定。测量单位为欧姆(Ω)。类型PCB传输线需要控制阻抗的是单端微带、单端带状线、微带差分对、带状线差分对、嵌入式微带和共面(单端和差分)。

1.1为什么需要控制阻抗?

通常,在高速数字应用中,如射频通信、电信、使用100MHz以上的信号频率进行计算、高速信号处理和高质量vwin 视频(如DDR、HDMI、千兆位以太网等)中,您需要受控阻抗。

在高频下,PCB上的信号轨迹就像传输线一样,在信号轨迹上的每个点都有阻抗。如果这个阻抗从一个点到另一个点变化,就会有一个信号反射,其大小取决于两个阻抗之间的差。差别越大,反射越大。这种反射将沿信号的相反方向传播,这意味着反射信号将叠加在主信号上。

结果,原始信号将失真:原本打算从发射机侧发送的信号一旦到达接收机端,就会发生变化。失真可能如此之大,以致信号可能无法执行期望的功能。因此,为了获得无失真的信号传输,PCB信号轨迹必须具有统一的受控阻抗,以最小化反射引起的信号失真。这是改善PCB线路上信号完整性的第一步。为了更好地理解,请阅读高速信号在PCB设计中的作用 .

PCB上的均匀传输线具有一定的迹线宽度和高度,并且与返回路径导体(通常是距离信号迹线一定距离的平面)保持一致的距离。

1.2影响控制阻抗的因素

影响PCB阻抗公差的因素包括材料的树脂含量百分比、树脂的Dk值和所用玻璃布的类型,以及其他物理PCB公差,如迹线顶部和底部的迹线高度和宽度. 当你把你的PCB设计–铜板图案、孔图案和最终材料厚度–我们将铜板层层压成一个电路板。我们制造您的印刷电路板与正确的图案尺寸和位置在一定的公差内。您必须确保制造商为您提供正确的尺寸、位置和蚀刻特征的公差。否则,您的电路板将彼此不同,这使得调试与性能相关的问题非常困难。

1.3为什么最好指定电路板的电介质而不是控制阻抗?

走线的阻抗也由电路板上使用的PCB材料定义。材料的介电常数和基于某些参数的预期阻抗称为受控电介质。如果你喜欢数学,你可以采用可控电介质的方法来控制你需要的阻抗。进行计算后,可以指定晶圆厂中铜层之间所需的介电空间。然后,用正确的轨迹和空间布局轨迹。

在这种情况下,请求控制阻抗板而不是控制电介质板可能更好。对于受控电介质,您是否指定要使用的玻璃布类型?材料的树脂百分比是多少?如果没有,那么您无法确定您的制造商正在使用什么。此外,您是否确保迹线宽度在公差范围内?如果您要求控制电介质板,则负担将落在您身上。

我们为您计算阻抗并不难。请让我们知道必须控制哪些走线以及所需的阻抗是什么。Sierra提供两种类型的阻抗控制:受控电介质和阻抗控制。

2.如何设计阻抗可控的电路板?

在设计PCB时,应遵循以下提到的受控阻抗布线策略:

2.1确定哪些信号需要阻抗控制

大多数时候,电气工程师会指定哪些信号网络需要特定的受控阻抗。然而,如果没有,设计者应该检查集成电路的数据表,以确定哪些信号需要控制阻抗。数据表通常为每组信号及其阻抗值提供详细的指南。数据表或应用注释中也可能会出现间隔规则和在哪个层上布置特定信号的信息。DDR跟踪、HDMI跟踪、千兆以太网跟踪、射频信号都是一些控制阻抗跟踪的例子。

2.2在原理图上注明阻抗要求

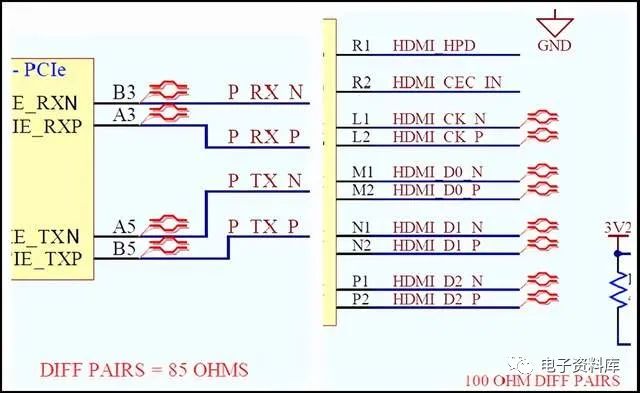

带差分对的高度示意图以及网络名称。

电路板的设计首先由设计工程师设计电路原理图。工程师必须在原理图中指定受控阻抗信号,并将特定网络分为差分对(100Ω、90Ω或85Ω)或单端网络(40Ω、50Ω、55Ω、60Ω或75Ω)。这是一个很好的设计实践N或P在示意图中差分对信号的网络名称后的极性指示。工程师还应在原理图或单独的“自述”文件中规定布局设计师应遵循的特定控制阻抗布局设计指南(如有)。

2.3确定受控CI的跟踪参数

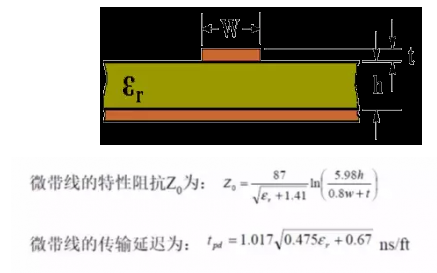

PCB轨迹由其厚度、高度、宽度和PCB材料的介电常数(Er)定义蚀刻的. 在设计控制阻抗印刷电路板时,必须考虑这些参数。您可以向制造商提供层数、特定层上的阻抗迹线值(50Ω,第3层100Ω),以及PCB设计所需的材料。

制造商给您的堆栈,其中提到每层的迹线宽度、层数、堆叠中每个电介质的厚度、迹线厚度和PCB材料。他还通过计算需要阻抗控制的迹线的可行厚度、宽度和高度来处理受控阻抗要求。请遵循以下关系,以了解阻抗如何取决于尺寸:

- 阻抗与迹线宽度和迹线厚度成反比。

- 阻抗与层压板高度成正比,与层压板介电常数(Er)的平方根成反比。

3.在设计受控阻抗时避免这些布线错误

3.1区分CI跟踪与其他跟踪

受控阻抗迹线宽度必须与线路板上的剩余迹线区分开来。它允许PCB制造商快速识别它们,并在必要时对迹线宽度进行适当的更改,以达到特定的阻抗。例如,如果您需要一个5mil的跟踪以获得50Ω的阻抗,并且您还路由了具有5mils宽度的其他信号,那么PCB制造商将无法确定哪些信号是受控阻抗跟踪。因此,您应该使50Ω阻抗轨迹宽度为5.1mil或4.9mil。

下表显示了不同层上控制阻抗的迹线宽度和间距。非阻抗信号记录道的布线宽度不应为3.5、3.6、4.2、4.25和4.3mil。

可控阻抗层的迹线宽度和间距。

3.2保持差分对路由中的对称性

对称地布置差分对,并保持信号始终平行。

高速差分对信号迹线需要以恒定间距相互平行布线。计算特定的微分阻抗需要特定的迹线宽度和间距。差分对需要对称布线。您应该尽量减少因衬垫或端部而增大指定间距的区域。

3.3足够间距的b/w受控阻抗记录道、其他记录道和元件(3W和2W规则)

为了减少串扰,b/w记录道的间距应为3W或至少为2W。注意t他的规则不适用于间距b/w差分对。

3.4元件、通孔和耦合电容器的放置

组件或 通孔不应放置在差分对之间,即使信号是围绕它们对称地布线的。元件和过孔会造成阻抗的不连续性,并可能导致信号完整性问题。对于高速信号,一个差分对和一个相邻差分对之间的间距不应小于记录道宽度(5W)的五倍。你也应该保持与其他信号机保持30英里的距离。对于时钟或周期性信号,应将“保持距离”增加到50毫秒,以确保适当的隔离。

避免差分对之间的元件和过孔。

如果高速差分对需要串联耦合电容器,则需要对称放置,如下图所示。电容器会产生阻抗不连续,因此对称放置会减少信号中的不连续量。欲了解更多信息,请阅读如何限制PCB传输线的阻抗不连续性和信号反射 .

对称放置耦合电容器以避免不连续。

对于差分对,应尽量减少过孔的使用,如果要放置它们,它们需要对称,以尽量减少不连续性。

不要在平面和PCB边界上发送高速信号。

3.5长度匹配

长度匹配将实现传播延迟匹配,前提是不同记录道上的信号速度相同。当一组高速信号一起传输并且预期同时到达目的地(在指定的失配公差内)时,可能需要长度匹配。

传输延迟匹配的长度匹配。

形成差分对的记录道长度需要非常紧密地匹配;否则,这将导致不可接受的延迟偏差(正负信号之间的不匹配)。长度不匹配需要通过在较短的记录道中使用蛇纹石来补偿。为了减少阻抗不连续性,需要仔细选择蛇形迹线的几何形状。下图显示了理想蛇形痕迹的要求。阅读我们的帖子如何制造可控阻抗印刷电路板 .

蛇形痕迹应尽可能靠近不匹配源。它保证了失配的尽快修正。在下图中,您可以看到不匹配发生在左侧的一组过孔上,因此需要将蛇形线添加到左侧而不是右侧。

不匹配点的长度校正

同样,弯板会导致不匹配,使内部弯板上的轨迹比外部轨迹小。因此,我们需要在靠近弯曲区域的地方添加蛇纹石。如果一对有两个弯曲小于15毫米,它们会互相补偿。因此不需要添加蛇纹石。

靠近弯板的长度补偿

当差分对信号使用通孔从一层变到另一层,并且有一个弯折,则该对的每一段都需要单独匹配。蛇纹石应放置在弯曲附近较短的痕迹上。您需要手动检查此冲突,因为它不会在设计规则检查中捕获,因为总信号的长度将密切匹配。由于不同层上记录道的信号速度可能不同,如果差分对信号需要长度匹配,则建议在同一层上路由差分对信号。还有,看看我们的帖子如何在KiCad中路由差分对 .

每段的长度差需要补偿。

3.6受控阻抗信号返回路径的参考层

所有高速信号需要一个连续的参考平面作为信号的返回路径。不正确的信号返回路径是噪声耦合和EMI问题. 高速信号的返回电流紧随信号路径,而低速信号的返回电流采用可用的最短路径。通常,高速信号的返回路径在最靠近信号层的基准面中提供。

高速信号不应在分割平面上进行路由,因为返回路径将无法跟踪跟踪。为了更好的信号完整性,您应该围绕分割平面布线。另外,确保每侧的地平面至少是迹线宽度的三倍(3W规则)。

避免在拆分平面上布线。

如果信号需要在两个不同的基准面上布线,则需要在两个基准面之间安装缝合电容器。电容器需要连接到两个基准面上,并且应该放置在靠近信号路径的地方,以保持信号和返回路径之间的距离很小。电容器允许回流电流从一个基准面传输到另一个基准面,并将阻抗不连续性最小化。缝合电容器的一个好值是在10nF和100nF之间。

应避免分割平面障碍物和参考平面中信号迹线正下方的槽。如果槽是不可避免的,应使用缝合过孔,以尽量减少由分离的返回路径造成的问题。电容器的两个管脚应连接到接地层,并应放置在信号附近。

在平面障碍物上布线时需要缝合电容器。

当过孔放置在一起时,它们会在参照平面中创建空心。为了尽量减少这些大的空隙,你应该错开过孔,以便在过孔之间提供足够的平面进给。交错的过孔允许信号有一个连续的返回路径。

最好使用地平面作为参考。但是,如果电源平面用作参考平面,则需要添加缝合电容器,以允许信号将参考从地面更改为电源平面,然后再更改回地面。你应该把一个电容器放在靠近信号入口和出口的地方,一端接地,另一端接电网。

当使用电源平面作为参考时,添加缝合电容器。

3.7在图层更改过孔附近添加缝合过孔.

如果高速差分对或单端信号交换层,则应在层更改过孔附近添加缝合过孔。这种做法也允许回流改变接地层。

如果一个高速信号跟踪切换到一个以不同网络为基准的层,则需要缝合电容器来允许回流电流从接地平面通过缝合电容器流向电源平面。对于差分对,电容器的布置应对称。

改变信号基准面时放置缝合电容器。

4.控制阻抗设计检查表

- 控制阻抗线应在PCB原理图中标记。

- 差分对记录道长度应与20%的信号上升/下降时间相匹配。

- 应使用高数据频率连接器。

- 对于微带结构,请在微带线下使用未破裂的地面。

- 在地面上,或在地面上使用的,或不间断的。地面和电力飞机提供回流路径。它还可以减少电磁干扰问题。

5.Sierra在控制阻抗方面的能力

Sierra电路用于阻抗测量的设备:

- Polar CIT

- Tektronix 8300

如果阻抗试片不起作用或未通过阻抗测试,Sierra将在电路板上进行阻抗测试,以验证产品是否在规范范围内,或者需要重新制作,并进行必要的调整。

然而,由于记录道的长度取决于电路板的尺寸,因此测试电路板的阻抗至关重要。成品上内层阻抗迹线的位置也非常关键。

6.如何使用电路阻抗计算器?

电路阻抗计算器

我们的阻抗计算器采用麦克斯韦方程组的二维解来计算不同阻抗模型的单端阻抗和微分阻抗。

除特性阻抗外,该工具还可估计以下轨迹参数:

- 电感

- 电容

- 单位长度传播延迟

- 模型的有效介电常数

- 耦合系数

- 奇偶模特性参数

大多数免费的在线阻抗计算器都不是很精确。这是因为他们是基于经验公式,没有考虑到梯形形状的痕迹和许多电介质材料的影响。

6.1阻抗计算器的特点

您可以从下拉列表中选择所需的阻抗模型,如无涂层微带、涂层微带、嵌入式微带和带状线。在每个型号中,您可以选择单端、差分对、共面单端、共面差分对、共面单端无接地和共面差分对不带接地组合。

在这个演示中,我们将选择无涂层微带单端阻抗计算器。

无涂层微带单端阻抗计算器

此计算器计算指定目标单端阻抗的迹线宽度,反之亦然。例如,如果迹线宽度需要计算,输入参数为电介质高度 ,介电常数 ,迹线宽度的顶部和底部之间的差异或δw ,迹线厚度,和单端目标阻抗. 同样,为了计算单端阻抗,应输入迹线宽度和前面提到的输入参数。

输入参数可能因计算器类型而异。无涂层微带差分对阻抗计算器的输入和输出参数如下图所示。

无涂层微带线差分对阻抗计算器

“选择单位”下拉菜单可用于更改输入参数的单位。介电常数指南帮助用户识别所用板材料的介电常数。本指南根据厚度、树脂含量以及材料是否为预浸料或芯材,提供了各种可用材料的介电常数。

内置介电常数导板

我们的阻抗工具提供82种不同的阻抗计算器,这些计算器是根据不同的轨迹几何形状设计和分类的。

要记住的要点

除了通常的PCB规格外,电路板设计者还应指定:

- 哪些层包含受控阻抗走线?

- 由于每层阻抗迹线可以有多个值,所以记录道的阻抗。

- 控制阻抗轨迹的单独孔径代码,例如4mil非受控阻抗轨迹和4mil受控阻抗轨迹。

记住,跟踪阻抗是控制反射的一个关键因素。阻抗必须与驱动器和负载匹配。

-

以太网

+关注

关注

40文章

5419浏览量

171588 -

阻抗

+关注

关注

17文章

957浏览量

45912 -

DDR

+关注

关注

11文章

712浏览量

65317 -

耦合电容器

+关注

关注

0文章

16浏览量

10364 -

PCB走线

+关注

关注

3文章

135浏览量

13917 -

射频通信电路

+关注

关注

0文章

7浏览量

2472

发布评论请先 登录

相关推荐

如何解决高速PCB设计中的可控阻抗板和线路特性阻抗问题

什么是阻抗控制如何对PCB进行阻抗控制

什么是可控阻抗?为什么控制阻抗很重要?

什么是可控阻抗?为什么控制阻抗很重要?

评论