电子发烧友网报道(文/李宁远)在半导体生产流程中,半导体封装是制造工艺的重要后道工序,是指将通过测试的晶圆加工得到独立芯片的过程。封装可以提供电气连接,防止物理损伤,降低环境腐蚀,并有助于散热。

从传统封装到先进封装

在典型的半导体封装流程中,传统封装技术以引线框架型封装作为载体,芯片与引线框架通过焊线连接,引线框架的接脚采用引线键合互联的形式。这里面主要包括了DIP、SOP、QFP、QFN等封装形式,传统封装的功能主要在于芯片保护、尺度放大、电气连接这些功能。

DIP双列直插形式封装技术是最早模集成电路采用的第一代封装技术,是通孔插入型封装里代表技术。此后发展到以SOP为代表的表面贴装型封装第二代封装技术,这一阶段的封装技术提高了管脚数和组装密度,是封装技术的一次革命,这阶段也是金属引线塑料封装的黄金时代。

随后,以球栅阵列封装BGA和芯片级封装CSP为代表的第三阶段封装技术成为主流。其中,BGA封装主要是将I/O端与基板通过球柱形焊点阵列进行封装,通常做表面固定使用,促进了安装技术的进步和芯片生产效率的提高。

这前面三个阶段的封装阶段被称为传统封装。传统封装技术的主要特点就是简单、成本低。这些封装类型大多数是通过引脚进行电气连接,这种连接方式在某些应用中可能会限制信号传输的速度和效率。同时这些传统封装的封装效率(裸芯面积/基板面积)也偏低,在电子器件的快速发展中渐渐不能跟上需求。

算速与算力上的需求推动着高端芯片的发展,高端芯片又不离不开先进封装。根据Yole统计数据,2021年先进封装市场规模约375亿美元,占整体封装市场规模的44%,预计到2027 年占比将提升至53%。

为了解决传统封装的技术短板,先进封装技术逐渐被开发出来,这些先进封装技术采用先进的设计和工艺对芯片进行封装级重构,并有效提升系统性能。相较于传统封装,先进封装的封装效率大大提高,能显著提升芯片的集成密度与互联速度,增强芯片整体的性能,并且改善散热和可靠性。

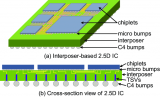

尤其是随着高性能计算需求的爆发,算速与算力上的需求推动了先进封装的进一步发展。目前,带有倒装芯片(FC)结构的封装、晶圆级封装(WLP)、扇出型封装(Fan-out)、系统级封装(SiP)、2.5D 封装、3D 封装等均被认为属于先进封装范畴。并行的先进封装技术很多,不过从技术角度细分来看,先进封装有着四大要素,Bumping、RDL、Wafer和TSV,具备四要素中任意一种技术即可被认为是先进封装。

从四要素看先进封装发展

Bumping工艺和倒装芯片(FC)封装关系紧密,是FC的前道基础工艺,是倒装芯片(FC)与PCB电连接的唯一通道。Bumping指在晶圆的I/O端口的Pad上形成焊料凸点的过程。可以理解为通过小型球状导体材料实现芯片与基板电气互连。其优势在于高端口密度、短传输路径、短信号延迟、优良热传导。其发展趋势是焊料凸点越来越小,电介质表面越来越光滑,集成密度越来越高。

RDL重布线层技术,用于2D平面电气延伸和互联,适用于为I/O端口进行宽松排布,广泛应用于晶圆级封装技术和2.5D/3D技术中,但不适用于倒装芯片技术。RDL为先进封装中的异质集成提供了操作上的基础。

RDL带来了更多的引脚数量,也能够替代一部分芯片内部线路的设计,最主要的采用RDL让触点间距更加灵活,凸点面积更大,增加元件的可靠性。在先进封装的FIWLP、FOWLP中RDL是最为关键的工艺技术。

Wafer技术,可以用作芯片的基底和WLP封装的载体,也可以与硅基板一同实现2.5D集成,技术发展趋势是使Wafer面积逐渐增大。

TSV,硅通孔技术,是先进封装中极为关键的垂直互连技术。TSV通过导电物质的填充,实现硅通孔的垂直电气互联,这项技术是目前唯一的垂直电互联技术,是实现半导体裸片和晶圆高密度互连的核心技术。

TSV和平面互连相比优势非常明显,不论在减小信号延迟、降低电容、电感,降低芯片功耗、提高通信、增加带宽还是提高集成度上都是明显的提升。随着摩尔定律逼近极限,半导体芯片的微型化也越来越依赖于集成TSV技术的先进封装。

先进封装范畴有着不少大量使用RDL、Bumping、TSV 等基础工艺技术的封装路线,需求侧中的不同也延伸出了多种不同形式的先进封装,如FOWLP、INFO、FOPLP、CoWoS、HBM、HMC等等。

Chiplet概念进一步推动2.5D/3D先进封装发展

根据Yole统计数据,2021年到2027年先进封装占比不断攀升,而其中,2.5D/3D先进封装市场收入规模年复合增长率高达14%,在先进封装多个细分领域中位列第一,这和Chiplet概念有着密切关系。

目前Chiplet概念愈发火热,Chiplet的核心是实现芯片间的高速互联,同时兼顾多芯片互联后的重新布线。先进封装技术和Chiplet发展密不可分,先进封装技术目前主要由台积电、日月光、Intel等产业龙头公司来主导,包含从2D MCM(Multi-Chip Module)到2.5D CoWoS、EMIB和3D Hybrid Bonding,这些先进封装技术均为Chiplet的关键封装技术。

在UCle联盟发布的Chiplet白皮书中,现阶段主流的Chiplet封装方式就提到了Intel的EMIB方案(硅桥连接)、台积电的CoWoS方案(硅中介层连接)以及日月光的FOCoS-B方案(扇出型中介层)。

台积电的2.5D封装CoWoS目前非常火,英伟达的多款GPU就是基于此先进封装,目前CoWoS产能仍然吃紧,而且台积电也在稳步推进3D封装技术。英特尔也在Foveros、Foveros Omni、Foveros Direct下一代3D先进封装上不断推进。

传统的封测厂也都有自己的先进封装发展布局,尤其是在2.5D和3D上,如日月光的FORB封装技术、长电科技的XDFOI封装技术、安靠的SLIM封装技术等等。

基于RDL、Bumping、TSV 等多项核心基础工艺技术的先进封装技术已经成为高端芯片不可或缺的重要环节。

小结

半导体芯片不断突破更高密度和更高性能的背后,晶圆制造和封装技术缺一不可。随着制程节点不断逼近摩尔定律极限,摩尔定律的迭代放缓,先进封装成为提高芯片性能,延续摩尔定律的重要技术手段。

从传统封装到先进封装

在典型的半导体封装流程中,传统封装技术以引线框架型封装作为载体,芯片与引线框架通过焊线连接,引线框架的接脚采用引线键合互联的形式。这里面主要包括了DIP、SOP、QFP、QFN等封装形式,传统封装的功能主要在于芯片保护、尺度放大、电气连接这些功能。

DIP双列直插形式封装技术是最早模集成电路采用的第一代封装技术,是通孔插入型封装里代表技术。此后发展到以SOP为代表的表面贴装型封装第二代封装技术,这一阶段的封装技术提高了管脚数和组装密度,是封装技术的一次革命,这阶段也是金属引线塑料封装的黄金时代。

随后,以球栅阵列封装BGA和芯片级封装CSP为代表的第三阶段封装技术成为主流。其中,BGA封装主要是将I/O端与基板通过球柱形焊点阵列进行封装,通常做表面固定使用,促进了安装技术的进步和芯片生产效率的提高。

这前面三个阶段的封装阶段被称为传统封装。传统封装技术的主要特点就是简单、成本低。这些封装类型大多数是通过引脚进行电气连接,这种连接方式在某些应用中可能会限制信号传输的速度和效率。同时这些传统封装的封装效率(裸芯面积/基板面积)也偏低,在电子器件的快速发展中渐渐不能跟上需求。

算速与算力上的需求推动着高端芯片的发展,高端芯片又不离不开先进封装。根据Yole统计数据,2021年先进封装市场规模约375亿美元,占整体封装市场规模的44%,预计到2027 年占比将提升至53%。

为了解决传统封装的技术短板,先进封装技术逐渐被开发出来,这些先进封装技术采用先进的设计和工艺对芯片进行封装级重构,并有效提升系统性能。相较于传统封装,先进封装的封装效率大大提高,能显著提升芯片的集成密度与互联速度,增强芯片整体的性能,并且改善散热和可靠性。

尤其是随着高性能计算需求的爆发,算速与算力上的需求推动了先进封装的进一步发展。目前,带有倒装芯片(FC)结构的封装、晶圆级封装(WLP)、扇出型封装(Fan-out)、系统级封装(SiP)、2.5D 封装、3D 封装等均被认为属于先进封装范畴。并行的先进封装技术很多,不过从技术角度细分来看,先进封装有着四大要素,Bumping、RDL、Wafer和TSV,具备四要素中任意一种技术即可被认为是先进封装。

从四要素看先进封装发展

Bumping工艺和倒装芯片(FC)封装关系紧密,是FC的前道基础工艺,是倒装芯片(FC)与PCB电连接的唯一通道。Bumping指在晶圆的I/O端口的Pad上形成焊料凸点的过程。可以理解为通过小型球状导体材料实现芯片与基板电气互连。其优势在于高端口密度、短传输路径、短信号延迟、优良热传导。其发展趋势是焊料凸点越来越小,电介质表面越来越光滑,集成密度越来越高。

RDL重布线层技术,用于2D平面电气延伸和互联,适用于为I/O端口进行宽松排布,广泛应用于晶圆级封装技术和2.5D/3D技术中,但不适用于倒装芯片技术。RDL为先进封装中的异质集成提供了操作上的基础。

RDL带来了更多的引脚数量,也能够替代一部分芯片内部线路的设计,最主要的采用RDL让触点间距更加灵活,凸点面积更大,增加元件的可靠性。在先进封装的FIWLP、FOWLP中RDL是最为关键的工艺技术。

Wafer技术,可以用作芯片的基底和WLP封装的载体,也可以与硅基板一同实现2.5D集成,技术发展趋势是使Wafer面积逐渐增大。

TSV,硅通孔技术,是先进封装中极为关键的垂直互连技术。TSV通过导电物质的填充,实现硅通孔的垂直电气互联,这项技术是目前唯一的垂直电互联技术,是实现半导体裸片和晶圆高密度互连的核心技术。

TSV和平面互连相比优势非常明显,不论在减小信号延迟、降低电容、电感,降低芯片功耗、提高通信、增加带宽还是提高集成度上都是明显的提升。随着摩尔定律逼近极限,半导体芯片的微型化也越来越依赖于集成TSV技术的先进封装。

先进封装范畴有着不少大量使用RDL、Bumping、TSV 等基础工艺技术的封装路线,需求侧中的不同也延伸出了多种不同形式的先进封装,如FOWLP、INFO、FOPLP、CoWoS、HBM、HMC等等。

Chiplet概念进一步推动2.5D/3D先进封装发展

根据Yole统计数据,2021年到2027年先进封装占比不断攀升,而其中,2.5D/3D先进封装市场收入规模年复合增长率高达14%,在先进封装多个细分领域中位列第一,这和Chiplet概念有着密切关系。

目前Chiplet概念愈发火热,Chiplet的核心是实现芯片间的高速互联,同时兼顾多芯片互联后的重新布线。先进封装技术和Chiplet发展密不可分,先进封装技术目前主要由台积电、日月光、Intel等产业龙头公司来主导,包含从2D MCM(Multi-Chip Module)到2.5D CoWoS、EMIB和3D Hybrid Bonding,这些先进封装技术均为Chiplet的关键封装技术。

在UCle联盟发布的Chiplet白皮书中,现阶段主流的Chiplet封装方式就提到了Intel的EMIB方案(硅桥连接)、台积电的CoWoS方案(硅中介层连接)以及日月光的FOCoS-B方案(扇出型中介层)。

台积电的2.5D封装CoWoS目前非常火,英伟达的多款GPU就是基于此先进封装,目前CoWoS产能仍然吃紧,而且台积电也在稳步推进3D封装技术。英特尔也在Foveros、Foveros Omni、Foveros Direct下一代3D先进封装上不断推进。

传统的封测厂也都有自己的先进封装发展布局,尤其是在2.5D和3D上,如日月光的FORB封装技术、长电科技的XDFOI封装技术、安靠的SLIM封装技术等等。

基于RDL、Bumping、TSV 等多项核心基础工艺技术的先进封装技术已经成为高端芯片不可或缺的重要环节。

小结

半导体芯片不断突破更高密度和更高性能的背后,晶圆制造和封装技术缺一不可。随着制程节点不断逼近摩尔定律极限,摩尔定律的迭代放缓,先进封装成为提高芯片性能,延续摩尔定律的重要技术手段。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

封装

+关注

关注

126文章

7873浏览量

142893 -

TSV

+关注

关注

4文章

111浏览量

81463 -

chiplet

+关注

关注

6文章

431浏览量

12584 -

先进封装

+关注

关注

2文章

400浏览量

241

发布评论请先 登录

相关推荐

2.5D/3D封装技术升级,拉高AI芯片性能天花板

2.5D/3D封装和Chiplet等得到了广泛应用。 根据研究机构的调研,到2028年,2.5D及3

显示体验升级:2.5D GPU技术逐渐成为标配,3D GPU加码可穿戴

德赢Vwin官网

网报道(文/莫婷婷)近日,芯原宣布与开源图形库LVGL达成战略合作,在LVGL库中支持芯原的低功耗3D和VGLite 2.5D GPU技术,芯原将助力进一步提升LVGL图形库的3D

先进封装占比不断攀升,Chiplet持续推动2.5D/3D技术发展

先进封装占比不断攀升,Chiplet持续推动2.5D/3D技术发展

评论