高频特性下的寄生参数

在生活中静电是广泛存在的,特别是在干燥的冬季,人们尤其能够感知。

不过相比于他的存在,我们更关心的是它对我们生活的影响:

1、对人的健康有一定的影响。

2、易燃、易爆环境由静电引起的火灾爆炸。

3、对电子产品的干扰、损坏。

如何最大化去避免静电放电对电子产品产生干扰和损坏,这需要对静电放电的特点和干扰形式了解清楚,才能在产品设计时保证产品的ESD可靠性。这也是我们讨论的重点。

静电放电的特点:

1、ESD是一种高频现象。

2、高电场容性耦合,初始的电场可以容性耦合到表面积较大的网络上,一般在离ESD电弧10CM处可以产生几KV/m的高电场。

3、强磁场感性耦合,电弧会产生一个1至几百兆的强磁场,一般在离ESD电弧10CM处可以产生几十A/m的强磁场。

4、破坏性脉冲大电流、高电压。

5、共模干扰为主。

高频特性下的寄生参数

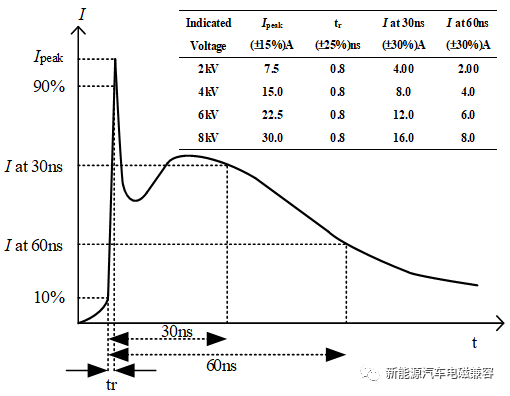

根据ESD的电流波形,可以看出ESD是一种高频现象,所以产品的寄生参数是改变放电路径的重要因素。

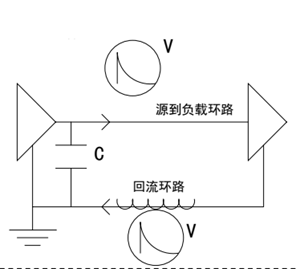

如图,当回流环路上流过ESD电流时,由于回路的寄生参数(如寄生电感,在高频下必定存在寄生参数,无法做到两点间的阻抗为零),回路上将产生脉冲电压:

U(V)=L(H)*dI(A)/dt(S)

L:寄生电感,1cm的缝隙大概为10nH

dI:ESD峰值电流(参考:6KV---22.5A,8KV---30A可参考ESD测试标准中的电流波形验证参数)

dt:ESD电流波形的上升时间(1ns)

I(A)=C(F)*dv(V)/dt(S)

C:寄生电容(印制线与参考地的寄生电容估算C(pF)≈0.1*S(c㎡)/H(cm);S为等效面积,H为距离)

dv:脉冲电压U

dt:ESD电流波形上升时间(1ns)

这个脉冲电流流过信号线产生的电压即为干扰电压。

总结: 根据干扰机理,减小回路阻抗是减小脉冲电压的根本,其中减小寄生电感很重要,保证回路的完整性以及缩短回路距离都会有利于减小寄生电感。寄生电容是导致干扰路径形成的主因,所以避免形成大的寄生电容是产品优良的ESD抗扰度的保证。

扩展:

如何减小寄生参数?

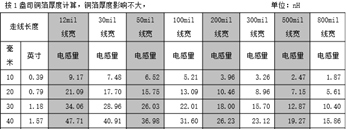

1、印制线间寄生电容(为容性串扰提供了条件)

相邻层上下平行布置印制线之间的寄生电容C主要取决于线宽W、线间距h和长度。C(pF/cm)与W/h成函数关系。h一定时,W越大单位电容越大。W一定时,h越大单位电容越小。所以减小线宽和增加间距已及相邻层上的布线要相互垂直,避免电容耦合。

同层相邻没有地平面的印制线主要取决于线间距,线距越大单位电容越小。相邻带地平面的印制线取决于线间距d、线宽W、与地平面的距离h。h一定时,d越大或W越小单位电容越小。所以布线时,遵循3W原则很重要。根据测算,带地平面的印制线间电容要小的多。

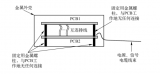

2、金属外壳与内部印制板之间的电容

增加外部金属壳与内部PCB板的距离可以减小相互的电容。屏蔽以及将敏感线布在中间层可以减小外部干扰对内部的影响。

3、回路寄生电感和感性串扰

回路“地”尽量要保持完整。

线连接要使用频蔽线缆,并且两端良好搭接。避免“猪尾巴”出现。

板与板之间的连接器一般不能提供很好的低阻抗路径,应考虑导电泡棉等进行地连接。

避免大环路布线,这是导致感性窜扰的重要原因。

有必要时,可制作人工“地”,如铜箔等。并与金属端口连接。

-

ESD

+关注

关注

48文章

2029浏览量

172927 -

PCB板

+关注

关注

27文章

1447浏览量

51610 -

连接器

+关注

关注

98文章

14476浏览量

136424 -

寄生电感

+关注

关注

1文章

155浏览量

14595 -

脉冲电压

+关注

关注

1文章

31浏览量

11213

发布评论请先 登录

相关推荐

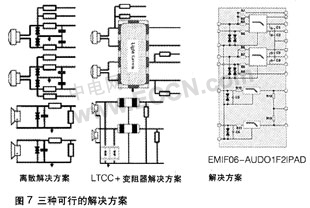

手机中ESD和EMI干扰

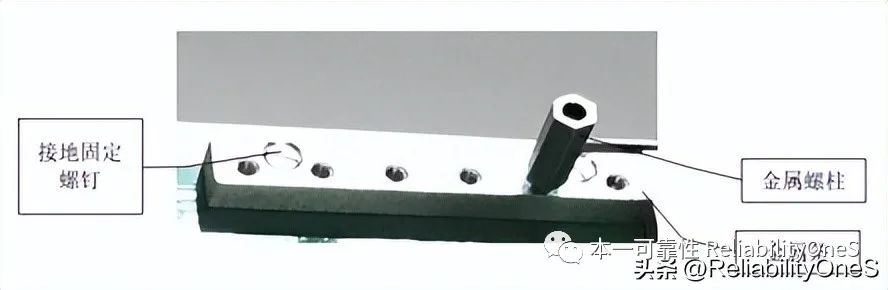

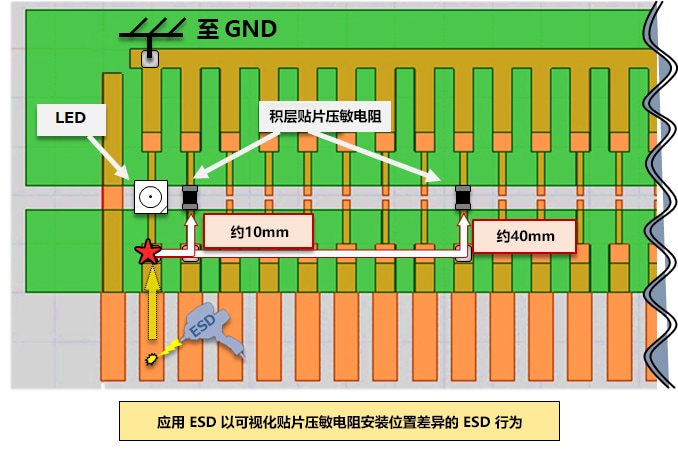

PCB工作地与金属外壳连接对ESD干扰影响的实例分析

ESD干扰路径介绍

ESD干扰路径介绍

评论