PG143中文文档简介

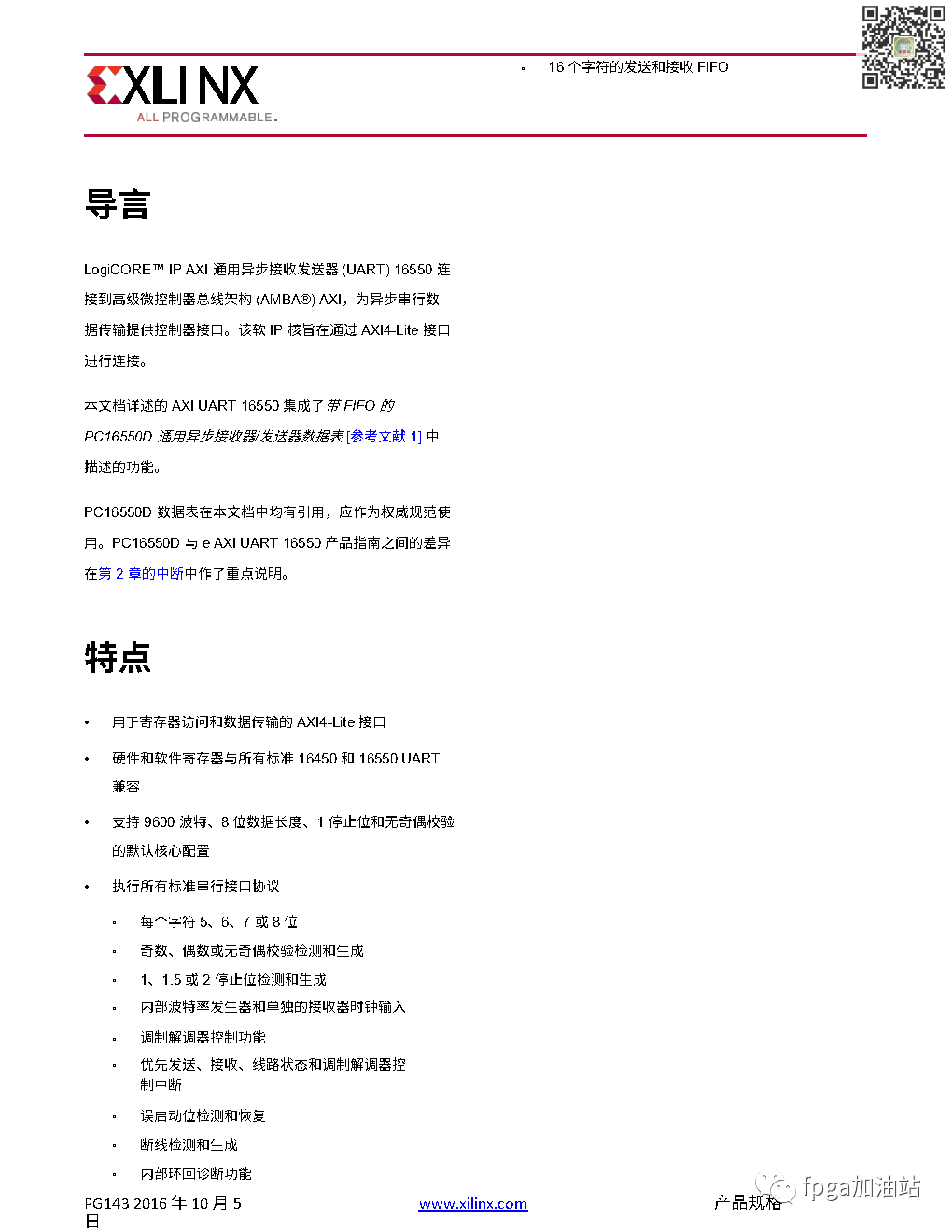

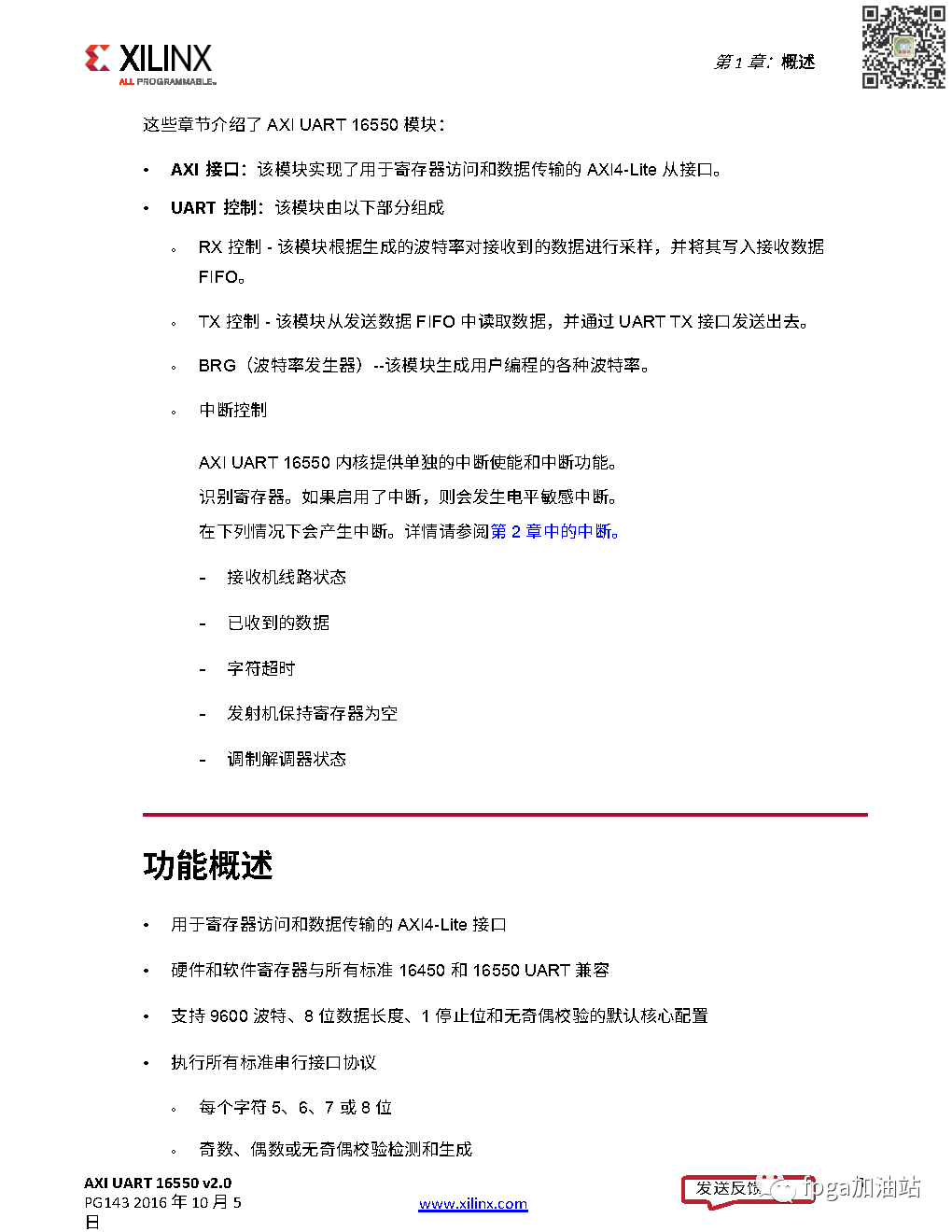

LogiCORE IP AXI 通用异步接收发送器 (UART) 16550 连接到高级微控制器总线架构 (AMBA) AXI,为异步串行数据传输提供控制器接口。该软 IP 核旨在通过 AXI4-Lite 接口进行连接。

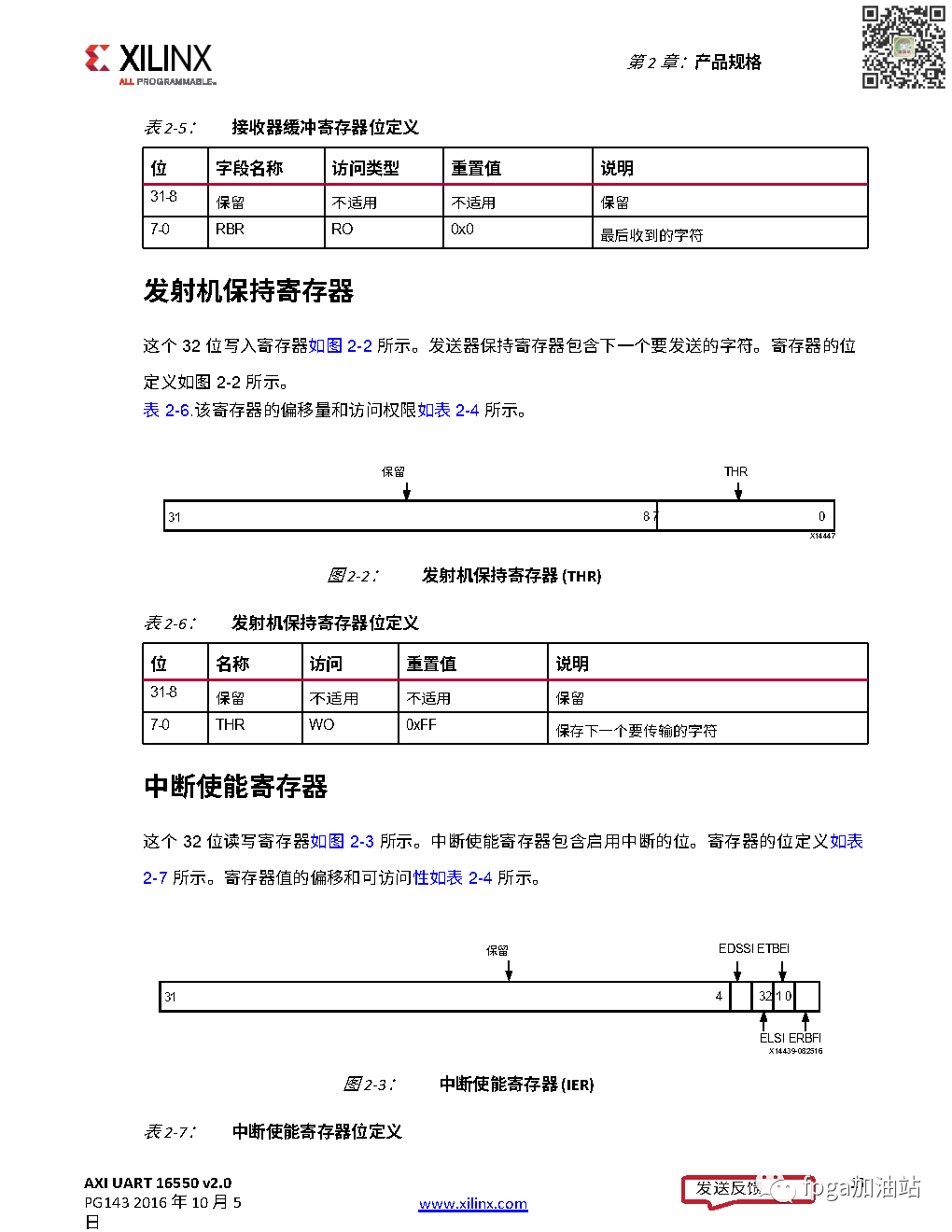

本文档详述的 AXI UART 16550 集成了带 FIFO 的PC16550D 通用异步接收器/发送器数据表 [参考文献 1] 中描述的功能。

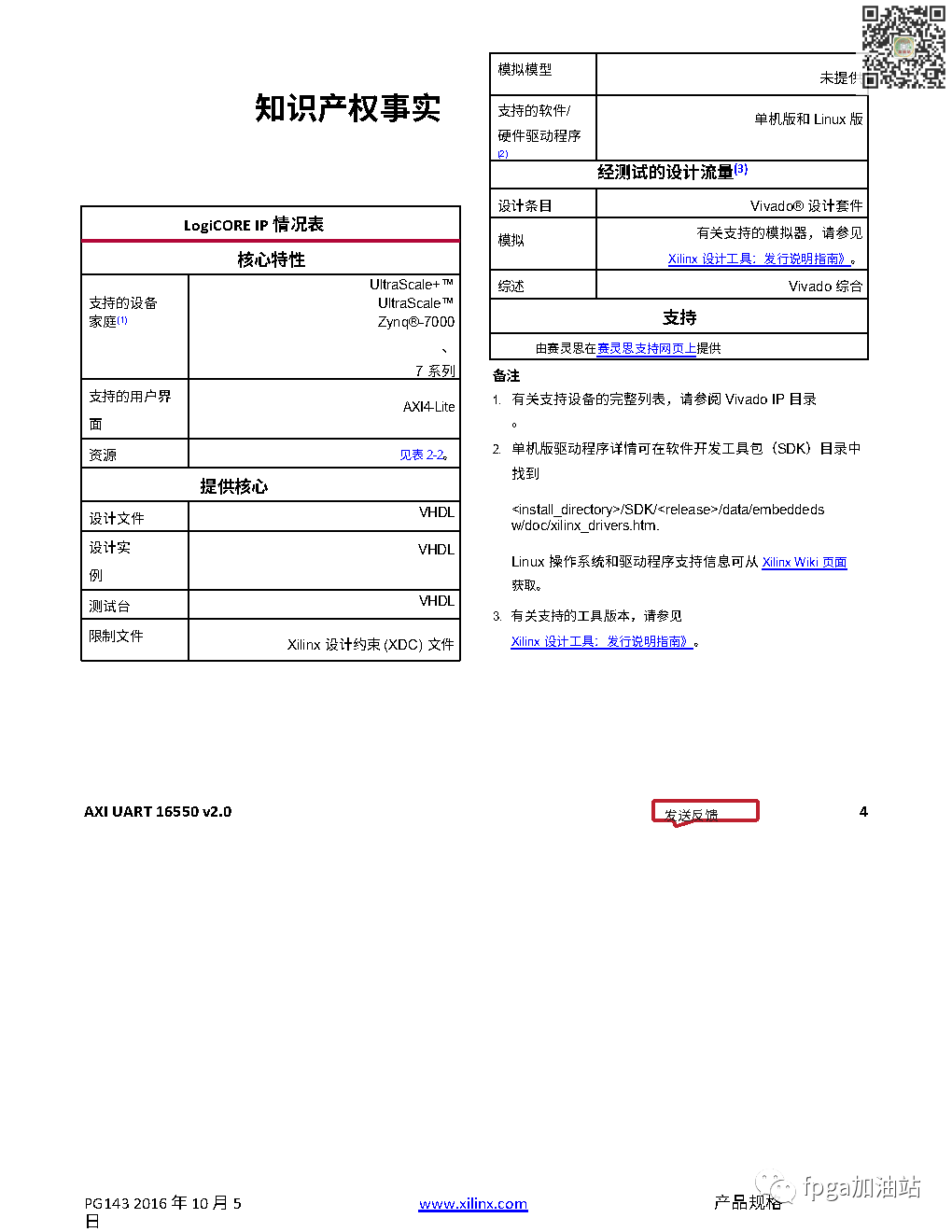

AXI UART 16550 IP 核实现了 PC16550D UART 的硬件和软件功能,可在 16450 和 16550UART 模式下工作。有关完整的详细信息,请参阅带 FIFO 的 PC16550D 通用异步接收器/发送器数据表 [参考文献 1]。

AXI UART 16550 内核对接收到的字符进行并行到串行转换。AXI UART 16550 能够发送和接收 8、 7、 6 或 5 位字符, 2、 1.5 或 1 个停止位,奇 偶 校 验 或无奇偶校验。AXI UART 16550 能够发送和接收 8 位、 7 位、 6 位或 5 位字符, 2 位、 1.5 位或 1位停止位,奇数、偶数或无奇偶校验。AXI UART 16550 可以独立发送和接收。

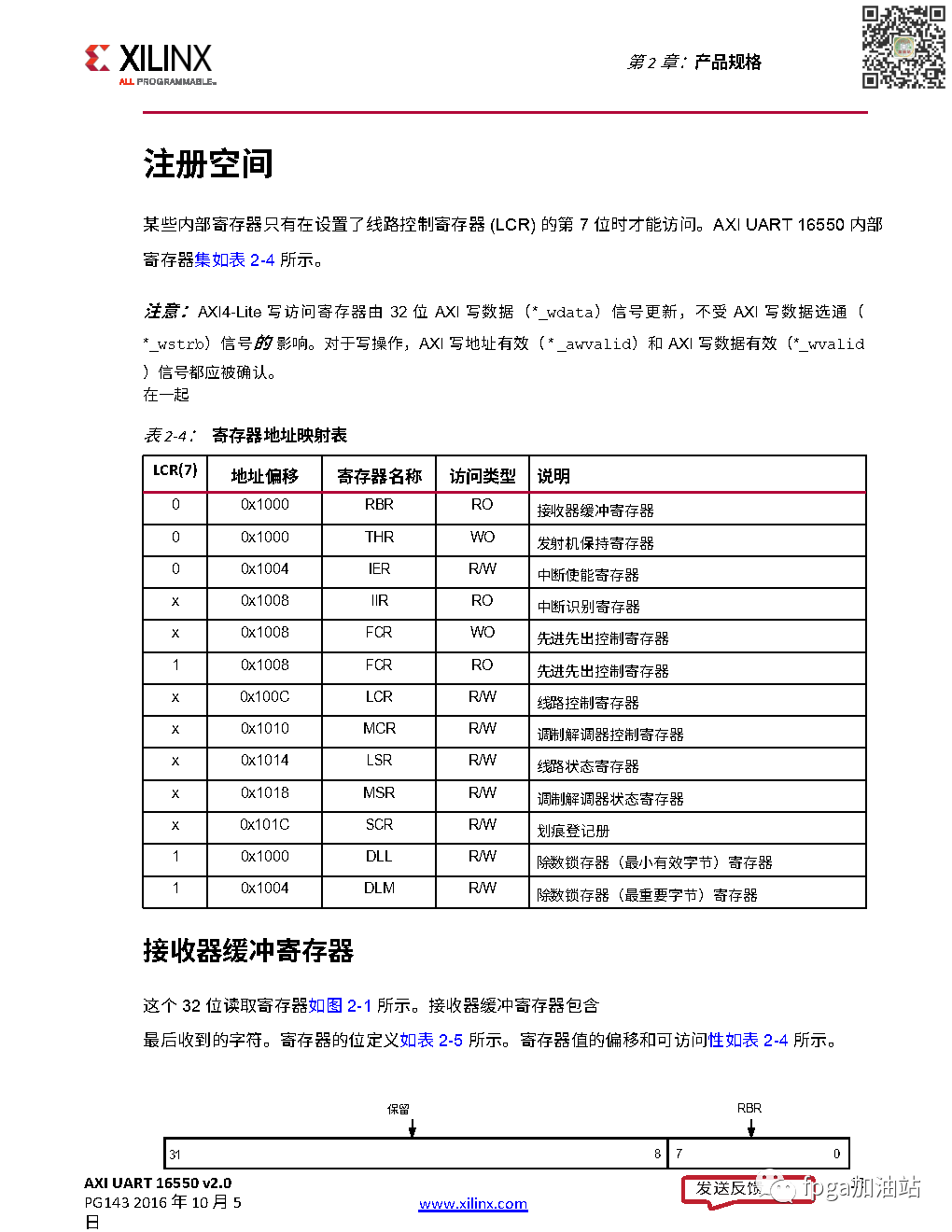

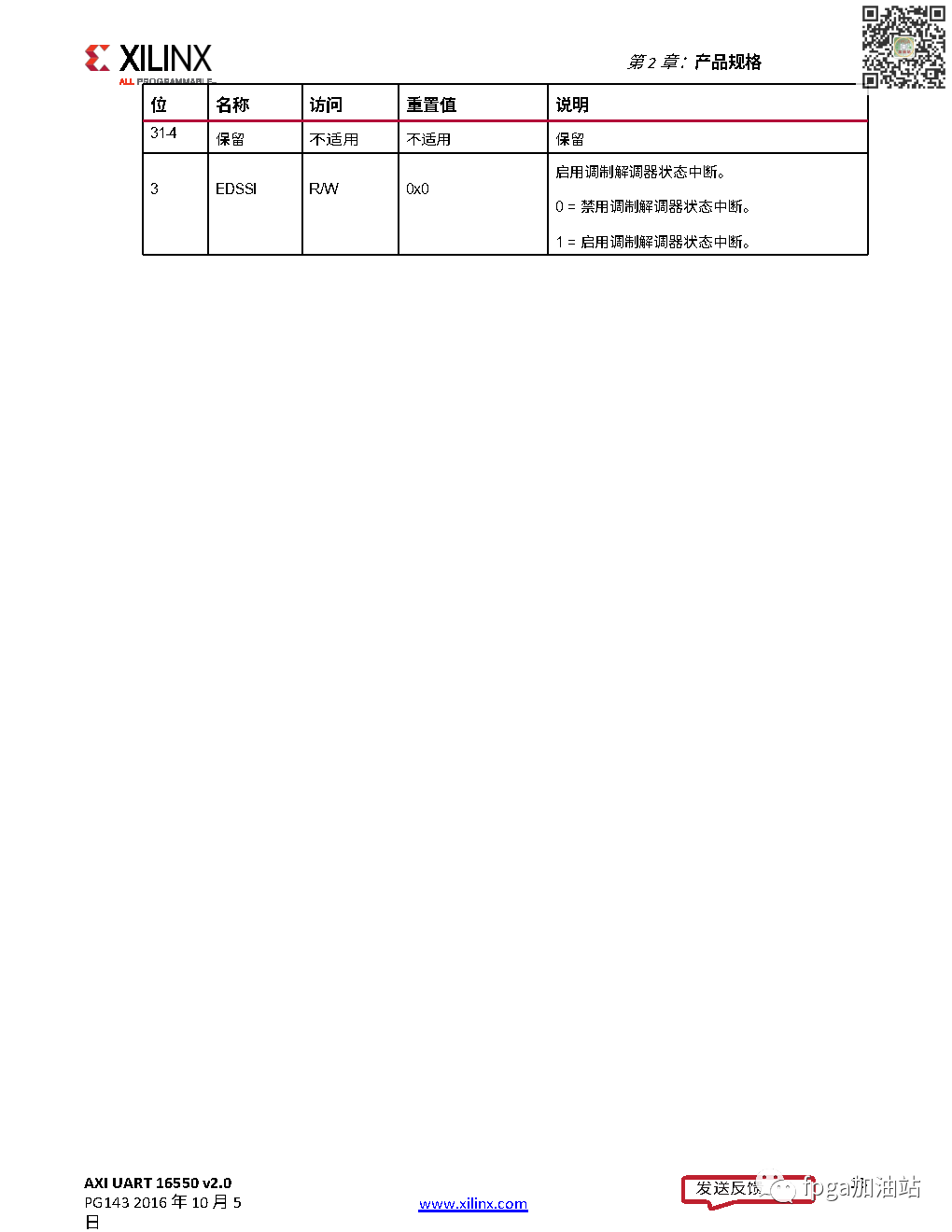

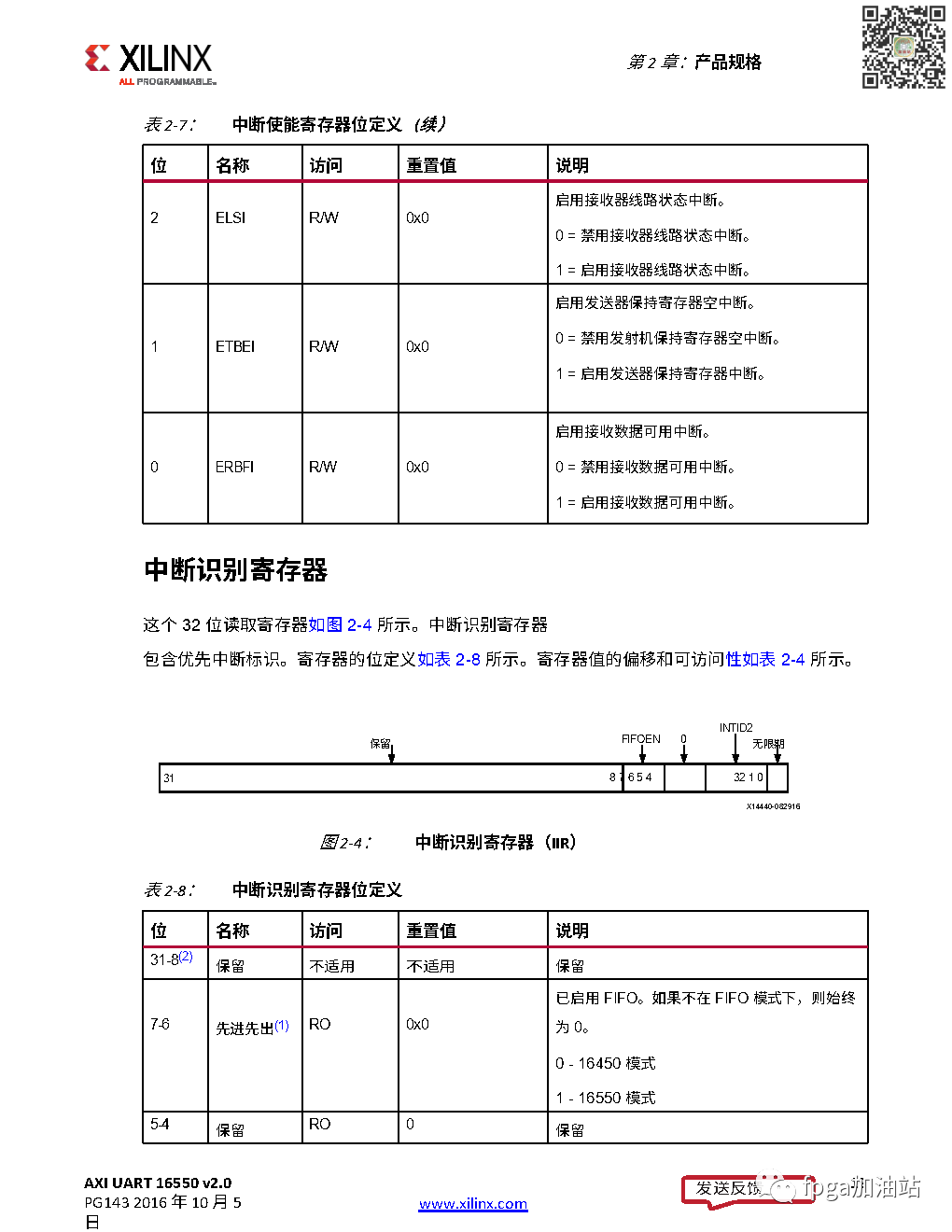

AXI UART 16550 内核具有内部寄存器,用于监控其在配置状态下的状态。该内核可发出接收器、发送器和调制解调器控制中断信号。这些中断可进行屏蔽和优先级排序,并可通过读取内部寄存器来识别。该内核包含一个 16 位可编程波特率发生器和独立的波特率发生器、16 个字符长度的发送和接收 FIFO。可以通过软件启用或禁用 FIFO。

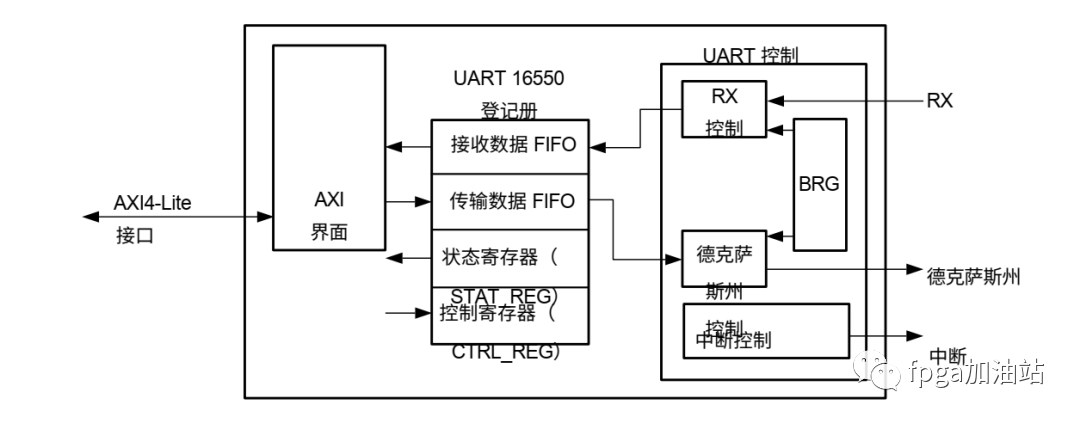

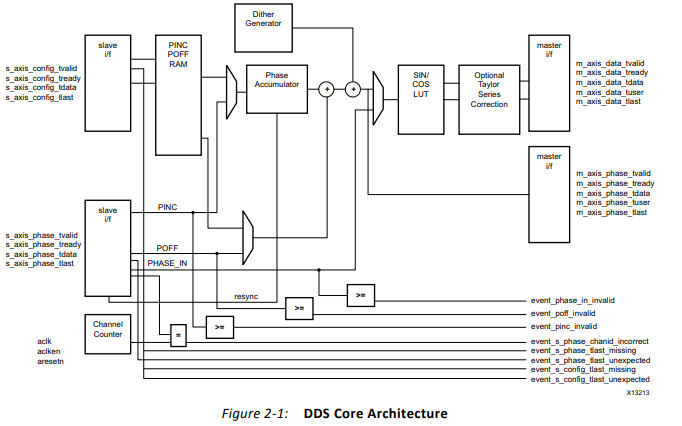

AXI UART 16550 内核的顶层框图如图 1-1 所示

PG143中文文档前20页预览

审核编辑:汤梓红

-

寄存器

+关注

关注

31文章

5224浏览量

118946 -

接口

+关注

关注

33文章

8136浏览量

149635 -

总线

+关注

关注

10文章

2794浏览量

87580 -

uart

+关注

关注

22文章

1180浏览量

100683 -

AXI

+关注

关注

1文章

127浏览量

16450

原文标题:PG143| AXI UART 16550 v2.0中文文档

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AXI UART 16550上的rx和tx端口在哪里?

Logicore IP CAN过滤问题

请问AXI UART16550无法接地额外的控制信号的原因是什么?

如何获得UART16550的额外端口?

UG157 LogiCORE IP Initiator/Ta

Xilinx的LogiCORE IP Video In to AXI4

Xilinx Logicore IP直接数字合成器DDS的用户手册免费下载

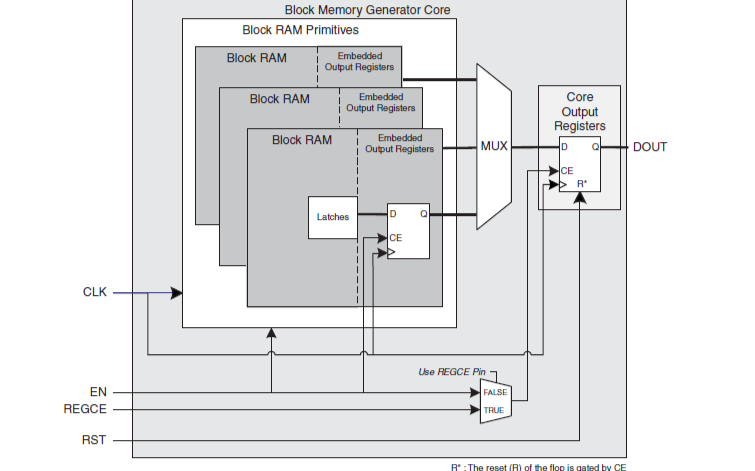

Xilinx LogiCORE IP块内存生成器的产品指南

LogiCORE JTAG至AXI Master IP核简介

LogiCORE IP JESD204内核概述

Xilinx LogiCORE IP视频定时控制器内核简介

LogiCORE IP AXI UART 16550内核简介

LogiCORE IP AXI UART 16550内核简介

评论