上一篇推文,小P学习了集成串扰噪声(ICN)的相关公式及概念,文末提到了一个ccICN的概念。那么这个又是什么呢。ccICN,全称component contribution integrated crosstalk noise,部件贡献集成串扰噪声,这里的component小P觉着翻译成“部件”会更恰当。

作为独立部件(连接器、线缆、芯片封装等)的设计厂商,无法获得详细的完整的全链路S参数模型。 ccICN的提出,主要是解耦链路中独立部件的ICN串扰评估分析与全链路完整S参数模型。注意,这里只是解耦了ICN串扰和完全链路S参数,全链路的损耗场景这个还是需要的。

这个概念,2018年DesignCon的一篇paper里面有给出解释,小P觉得讲的十分简单明了了。

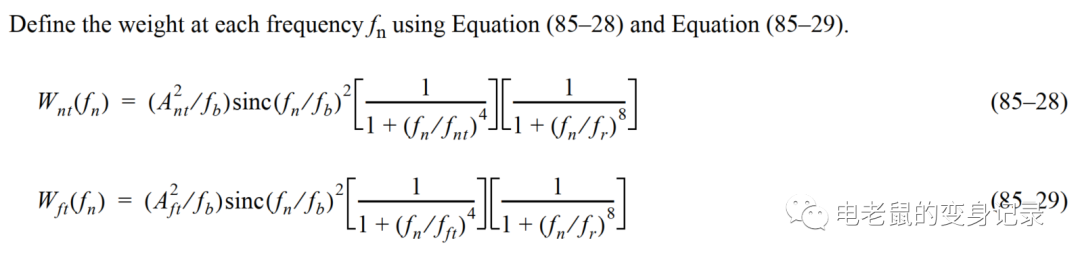

Component contribution ICN (ccICN) builds on the ICN calculation methodology byadding a secondary weighting function toaccount forthe channel attenuation external to the component (orsub-channel) under test.

Chien-Ping Kao, Brent Rothermel, Jeremy Stephens

对,就还是这三位intel的大佬,他们对ccICN的解释是,ccICN是建立在ICN噪声的基础上,加上了一个二次权重函数用于解释部件以外的衰减。

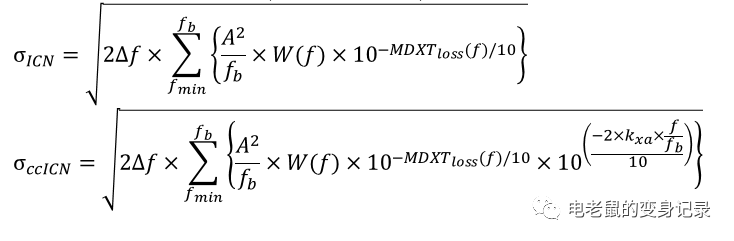

我们来看一下ccICN的计算公式:

可以看到ccICN就比ICN多了一个函数

这就是前面提到的二次权重函数。其他的部分ccICN与ICN是完全一致的。

那么这个权重函数中,也就只有一个kxa是生面孔。kxa是一个常数,用于表征除了待测部件(Component Under Test, CUT)以外产生的损耗,单位是dB。值得注意的是,CUT以外链路产生的串扰不在ccICN中进行计算表征。kxa,就是整个串扰链路减去CUT本身损耗以外,在奈奎斯特率下的损耗值。

如下图,红色曲线是一个5inch长度的有损传输线的插损曲线,假定波特率fb是32Gbps,因此奈奎斯特率是16GHz。可以看到插损在16GHz时是-4.117dB,因此kxa取值为4.117。蓝色曲线代表二次权重函数,在奈奎斯特率时与插损是相交的。

上图说明了kxa值代表的是插损,那么放到具体的链路场景中的kxa应该怎么取值呢。

如下图是小P瞎画的一个端到端链路场景,全链路的插损是28.4dB@Nyquist,并且每个分段部件(也就是咱们所说的component)的插损也在图上有所表现。假定VICTIM的数据流方向是从右向左,也就是左侧才是VICTIM的Receiver,也就是我们关注左侧VICTIM的串扰噪声。

下表中就是各个部件的kxa值,值得注意的是,FEXT和NEXT的kxa值是不一样的(因为他们的串扰路径有所区别),左侧TX对左侧VICTIM的串扰为NEXT,右侧TX对左侧VICTIM的串扰为FEXT。

| kxa_NEXT/dB | kxa_FEXT/dB | |

|---|---|---|

| PKG0 | 0 | 24.2 |

| PCB0 | 8.4 | 22.9 |

| Connector0 | 19.4 | 27.2 |

| Cable | 21.8 | 18.4 |

| Connector1 | 41.8 | 27.2 |

| PCB1 | 44.2 | 24.9 |

| PKG1 | 51.2 | 25.6 |

| Full Channel | 0 | 0 |

上表表示的是aggressors链路与victim链路的每个component损耗是相等的情况下。我们选取Connector1的kxa计算来详细解释。注意,kxa值计算时,不计算串扰部件自身的损耗。

上图是NEXT的串扰信号传输路径

kxa_NEXT=4.2(PKG0)+5.5(PCB0)+1.2(Connector0)+10(Cable)+10(Cable)+1.2(Connector0)+5.5(PCB0)+4.2(PKG0)=41.8dB

上图是FEXT的串扰信号传输路径

kxa_FEXT=2.8(PKG1)+3.5(PCB1)+10(Cable)+1.2(Connector0)+5.5(PCB0)+4.2(PKG0)=27.2dB

从以上NEXT和FEXT串扰链路的kxa计算可以看出,在串扰部件之前的损耗,是信号在aggressor链路上的传输损耗,在串扰部件之后的损耗则是信号在victim链路上的传输损耗。

若是出现aggressor与victim全链路损耗不一致的情况,同样按照上述规则进行计算。

kxa的计算弄清楚了以后,ccICN也就不是什么让人迷惑的东西了。从kxa值的变化可以看出,ccICN_FEXT与部件所在位置无关,ccICN_NEXT与部件所在位置有关。

协议规范的制定者可以通过定义ccICN的要求,以提供部件供应商进行设计评估。部件供应商则不需要完整的具体链路场景,而是基于协议规范给出的要求,得到相应的kxa则可以计算出自己部件的ccICN。

- 连接器

+关注

关注

98文章

13651浏览量

134707 - 芯片封装

+关注

关注

11文章

443浏览量

30349 - 串扰

+关注

关注

4文章

184浏览量

26863 - 线缆

+关注

关注

4文章

480浏览量

28875

发布评论请先登录

相关推荐

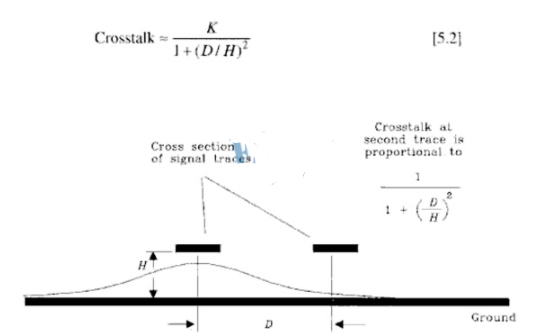

PCB设计与串扰-真实世界的串扰(上)

如何解决PCB串扰问题

串扰是怎么引起的 降低串扰有哪些方法

理解串扰Crosstalk

串扰学习笔记(2)

串扰学习笔记(2)

评论