Perface

coresight的寄存器

coresight对于每个coresight组件,规定了一些寄存器,这些寄存器的偏移是固定的,这些寄存器,是必须存在的。但是有的,可以不实现该寄存器功能。

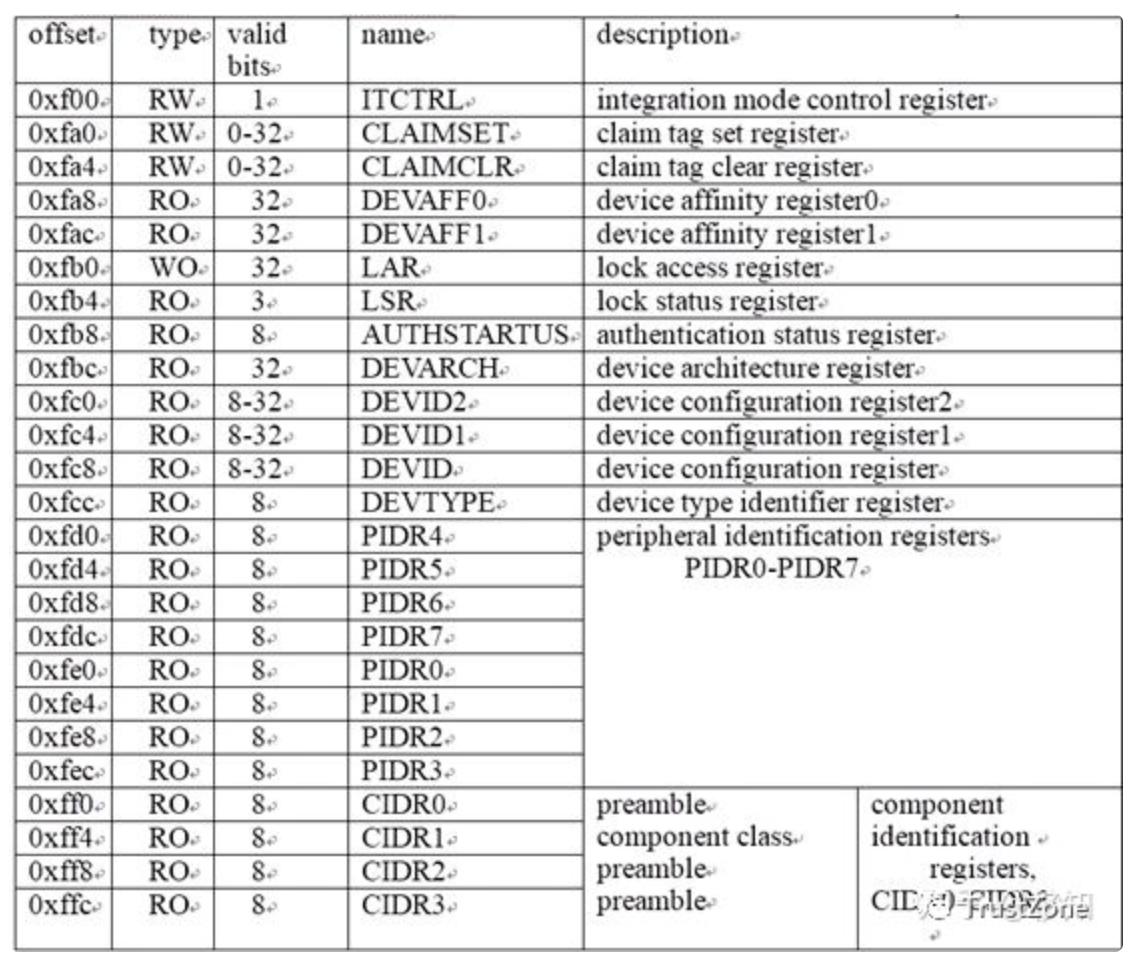

1、寄存器一览

coresight架构,对于coresight的组件,定义了若干个固定的寄存器。第一个寄存器的偏移从0xf00开始,直到0xffc。以下是寄存器列表:

以上的寄存器的地址,在coresight的组件中,是不能当作其他功能使用的。如果该寄存器,在该组件没有实现,那么该寄存器地址要保留,读取要返回0,写被忽略(read must return zero, and writes must be ignored),而不能当作其他功能使用。

对于coresight的组件,占用1个4k或者整数倍的4k空间的memory空间。

而coresight的寄存器,处于组件占用空间的最后一个4K空间的最后一部分。

以下是一个coresight组件占用的memory空间。占用一个4k空间。

寄存器分为两部分:

- device-specific registers:组件自定义寄存器,从0x000-0xeff。 coresight组件利用这些寄存器,实现该组件的功能 。

- coresight management registers:coresight固定的寄存器,从0xf00-0xfff。这部分寄存器的功能是固定的。

以下是包含了多个coresight组件memory分布,每个组件,占用4K空间的整数倍空间。

对于第2个组件,占用了16k的空间,但是coresight寄存器,是在最后一个空间的最后位置。

而其他3个组件,都只占用了1个4K空间。因此coresight寄存器,在这一个空间的最后位置。

2、ITCTRL,integration mode control register 工作模式寄存器。

对于每个coresight组件,可以工作在两种模式下:

- functional mode

- integration mode

两种模式的区别,在于对coresight组件的寄存器的访问,是否会引发寄存器相应的功能。

integration mode是用来topology detection的。当一个debugger连接到一个soc后,此时debugger是不知道soc内部有哪些coresight组件的。因此就需要通过查询,来得知soc中有哪些coresight组件的。

而查询,就是通过访问coresight组件的寄存器来实现的。此时soc还不知道组件是什么组件,因此也就不知道组件的寄存器是有什么功能。因此此时是不能随意对组件的寄存器进行访问的。

为了使访问的过程中,不影响组件的功能,就可以让组件工作在integration mode下,此时访问组件的寄存器,不会引发寄存器相应的功能。

待debugger查询完毕后,获取到soc中各个coresight组件的信息后,再将组件的模式切换为functional mode。

复位后,组件必须工作在functional mode下。因此外部debugger对组件查询完毕后,可以直接对组件进行复位,这样所有的组件就恢复到了function mode了。

3、CLAIM寄存器

这个寄存器是一个32位的不可见寄存器。只能通过访问CLAIMCLR和CLAIMSET这两个寄存器,来设置或者获取该寄存器的值。

该寄存器,可以用来表示该组件的状态。这个是由实现来定义的 ,比如可以规定,该寄存器的最低位,表示最近该寄存器被读取过,第1位,表示最近该寄存器被写过。

CLAIMCLR寄存器:

CLAIMSET寄存器

4、DEVAFF

device affinity register 组件关联功能寄存器 。有时候,组件需要和其他组件,联合起来工作,这样,就需要指示该组件是和另外的什么组件进行关联,就可以用这寄存器。

比如一个ETM,追踪一个core的trace信息,那么这个寄存器,就保存core的MPIDR寄存器信息, 这样debugger就可以通过DEVAFF寄存器,得知这个ETM是关联的哪一个core 。

我还以为是和别的CIT组件这些配合

DEVAFF0寄存器:

DEVAFF1寄存器:

5、lock 寄存器

对于coresight组件的寄存器,ARM定义了如下的一些访问方式:

可以分为两类访问:

- 系统寄存器访问:通过MSR,MRS指令(aarch64),MCR,MRC指令(aarch32)

- external debug接口访问:DAP访问,或者是memory-mapped访问,也就是软件通过load store访问

对coresight组件寄存器的访问,是有权限要求的 。

对于系统寄存器访问和memory-mapped访问,ARM 定义了software lock这个权限限制 。当software lock有效的时候,软件是不能访问coresight组件寄存器的。

software lock的目的, 是为了防止软件意外的修改coresight组件的寄存器 ,从而修改当前系统状态,或者获取一些不该获取的信息。可以用来防黑客。

software lock提供了两个寄存器,一个是LAR,一个是LSR。

- LAR是用来设置software lock状态,

- 而LSR是保存当前的software lock的状态。

往LAR写入0xc5acce55,software lock状态切换为unlock, software可以正常访问coresight组件的寄存器,写入其他值,software lock状态切换为lock,software不可以正常访问coresight组件的寄存器(实现自定义)。

对于DAP访问,software lock是没有用的。因为要通过DAP访问,是必须要debugger连接芯片的。所以coresight组件要能够区分,当前的访问是DAP访问,还是非DAP访问。

在DAP访问中,需要使用debugger工具来连接芯片,并执行一些特定的操作,例如读取或者修改芯片的寄存器或者内存。在这个过程中,软件锁(software lock)是没有用的,因为软件锁主要用于防止未经授权的软件访问coresight组件的寄存器,而在DAP访问中,debugger工具需要获得特定的授权才能进行访问。

另一方面,非DAP访问通常是由软件直接进行的,例如通过串口或者USB接口进行数据传输。在这个过程中,就需要使用软件锁来防止未经授权的软件访问coresight组件的寄存器,以保护系统的安全和稳定。

非DAP访问场景:

- 开发人员使用IDE(集成开发环境)编写代码,并通过编译器将其编译为可执行文件。

- 开发人员使用串口或者USB接口将可执行文件下载到目标嵌入式系统中。

- 开发人员使用串口调试器或者类似的工具来连接到目标嵌入式系统,并通过发送特定的命令来执行调试操作,例如设置断点、单步执行等。

- 在这个过程中,开发人员不需要获得特定的授权才能进行访问,但是需要+ 对目标嵌入式系统的硬件和软件有一定的了解,以便正确地发送命令和解析调试信息。

DAP访问场景:

- 开发人员使用专门的调试工具(例如GDB)来连接目标嵌入式系统。

- 开发人员使用调试工具来设置断点、单步执行等操作,并通过调试器来查看和修改目标嵌入式系统的寄存器和内存。

- 在这个过程中,开发人员需要获得特定的授权才能进行访问,因为调试工具需要连接到目标嵌入式系统的核心寄存器或者内存中。

- DAP访问通常需要更高的技术要求和更复杂的设置,但是它可以提供更高级别的调试功能和更灵活的控制方式。例如,开发人员可以在不重新编译代码的情况下对目标嵌入式系统进行实时调试,查看和修改寄存器和内存的值,以及进行多线程和多进程的调试等操作。

关键在于想访问的一个是程序本身,还有一个是系统平台更底层的东西

6、AUTHSTATUS

authentication status register debug功能的认证接口。

debug可以分为non-invasive和invasive。

- non-invasive就是self-hosted

- invasive就是external debug。

non-invasive debug(非侵入性调试): 非侵入性调试通常指的是self-hosted(自托管)调试。在这种方法中,开发人员使用同一台计算机来执行程序和监视程序的执行过程。这通常是通过在开发人员机器上运行一个vwin 器或虚拟机来模拟目标系统或设备的行为。非侵入性调试不需要直接访问目标系统的硬件或底层资源,因此它不会干扰目标系统的正常操作。这种方法的优点是简单、安全且易于使用。然而,它可能无法提供与实际硬件完全一致的仿真体验,因此可能会遗漏一些特定于硬件的错误或问题。

invasive debug(侵入性调试): 侵入性调试通常指的是external debug(外部调试)。在这种方法中,开发人员需要将调试器连接到目标系统或设备的硬件上,以便直接监视和控制其执行过程。这种方法需要侵入目标系统,可能会对目标系统的正常操作产生干扰或影响。因此,在进行外部调试之前,通常需要先备份目标系统的状态或创建一个测试版本来保护原始数据。外部调试的优点是可以提供更准确和详细的调试信息,特别是在处理硬件相关的问题时。然而,它需要更高的技术要求和更复杂的设置,并且可能会对目标系统的稳定性或性能产生负面影响。

实际中,可以根据不同的应用需求,可能会需要支持debug,但是也可能需要支持debug中的一种,也有可能不需要支持debug功能。

因此考虑到这些需求,ARM定义了认证接口。认证接口总共包括4个。这4个接口是每个ARM的core要实现的。这些接口是debug功能的总开关。

- DBGEN:invasive debug enable

- SPIDEN: secure invasive debug enable

- SPNIDEN:secure non-invasive debug enable

- NIDEN: non-invasive debug enable

DBGEN:这是invasive debug enable(调试使能)的缩写,这个接口可能用于开启或关闭侵入性的调试功能。在调试过程中,通过这个接口,可以控制调试器的接入和运行,从而实现对ARM核心的调试。

SPIDEN:这是secure invasive debug enable(安全侵入性调试使能)的缩写,这个接口可能用于在安全环境下启动侵入性的调试功能。在需要保证安全性的情况下,例如在处理敏感数据或在进行关键任务的操作时,这个接口可以控制调试器的安全接入和运行。

SPNIDEN:这是secure non-invasive debug enable(安全非侵入性调试使能)的缩写,这个接口可能用于在安全环境下启动非侵入性的调试功能。与SPIDEN类似,这个接口可以控制调试器的安全接入和运行,但是不会对目标系统或数据产生干扰或损害。

NIDEN:这是non-invasive debug enable(非侵入性调试使能)的缩写,这个接口可能用于开启或关闭非侵入性的调试功能。与DBGEN类似,这个接口可以控制调试器的接入和运行,但是不会对目标系统或数据产生干扰或损害。

而这个authentication status寄存器,就是保存了这4个接口信号的状态。DBGEN使能的时候,NIDEN被忽略,即NIDEN被认为是使能。SPIDEN使能的时候,SPNIDEN被忽略,即SPNIDEN被认为是使能。

7、DEVARCH

device architecture register 这个寄存器,标识了coresight组件的架构信息。

这里主要关心ARCHID这个位域。

8、DEVID

device configuration register 这个寄存器的功能,由实现进行定义,总共包括3个寄存器,DEVID,DEVID1,DEVID2,每个寄存器32位,只读。

DEVID寄存器:

DEVID1寄存器:

DEVID2寄存器:

9、DEVTYPE

device type identifier register 组件的具体类型信息。依靠MAJOR位域和SUB位域来表示。

以下是组合情况:

可以看出,arm对组件分成了7大类:

- miscellaneous: 杂散类,

- trace sink: 最终接收trace信息的组件,包括有TPIU,ETB,router。

- trace link:trace信息传递过程中需要的中间组件,包括有router, filter, FIFO

- trace source: 产生trace信息的master

- debug control:debug的控制器

- debug logic:具有debug功能的master

- performance monitor:性能的检测器检测的master

举一个例子,假设有一个基于Cortex-A处理器的嵌入式系统,该系统使用Coresight进行调试和跟踪。在Coresight中,可能存在一个Trace Sink组件,用于收集和处理跟踪数据。该组件的MAJOR位域可能被设置为0x1,以表示它属于Trace Sink类别。而它的SUB位域可能被设置为0x100,以表示它是该类别中的一个特定组件。

通过读取该组件的DEVTYPE寄存器值,可以确定它的类型和身份。如果DEVTYPE的值为0x101(即MAJOR位域为0x1,SUB位域为0x100),则可以知道该组件是一个Trace Sink,并且它是该类别中的一个特定组件。

通过DEVTYPE寄存器的值,开发人员可以更好地理解系统的运行状况并进行适当的调试操作。例如,如果开发人员知道该组件的功能和行为,则可以通过修改该组件的代码或配置来改善系统的性能或稳定性。

总之,DEVTYPE寄存器的作用是提供组件的类型信息,以便在Coresight中进行调试和跟踪。它是开发人员了解系统运行状况和进行适当调试操作的重要工具之一。

10、PIDR0-PIDR7

peripheral identification registers 外设识别寄存器。

这里面,我们关心的是SIZE,和Part number。因为其他的值在一个soc中,所有的组件的值是固定的。

- SIZE:表示这个组件,占用4k空间的块数。如果只占用一个块,那么值是0,如果占用两个块,值是1。占用的块数为 2^SIZE。以下是SIZE对应的组件占用的大小。以及需要访问这个组件需要的地址宽度。

part number:组件的唯一编号。soc中有多个coresight的组件,为了较好方便的管理这些组件,给每个组件分配了唯一的编号。这个编号就保存在part number中。

对于JEP106,这个是JEDEC标准,可以查阅以下网站; www.jedec.org

Coresight寄存器PIDR0-PIDR7以及peripheral identification registers外设识别寄存器的作用是识别和分类不同的外设组件。这些寄存器提供了关于ARM核心上组件的详细信息,例如组件的名称、类型、大小以及它们在ARM核心上的位置。通过读取这些寄存器的值,可以识别和区分不同的组件,以便进行调试、性能监控等操作。

11、CIDR0-CIDR3

component identification registers 这四个寄存器,每个寄存器只有最低8位有效。 这四个寄存器的组合,用来标识组件的类型 。

对于ARM的组件,CIDR寄存器的有些位是固定的。比如对于CIDR0,CIDR1[3:0],CIDR2,CIDR3,是有固定值的。

CIDR1寄存器中有一个CLASS位域,用来表示组件属于哪一个类 。ARM对自己的组件,也划分了若个的类。

CIDR0-CIDR3寄存器是ARM核心上的一部分,每个寄存器只有最低8位有效。这些寄存器的组合被用来标识组件的类型,以便进行调试和优化。

这里,我们关心如下的class:

- 0x1:rom table

- 0x9:coresight组件。

- 0xf: corelink组件

读取组件的CIDR寄存器,即可知道这个组件是属于哪一类。

- 对于rom table, 固定为 0xb105_100d 对于

- coresight组件,固定为 0xb105_900d 对于

- corelink组件, 固定为 0xb105_f00d

假设我们有一个ARM核心,我们想要识别其上的所有组件。首先,我们可以使用Coresight寄存器PIDR0-PIDR7以及外设识别寄存器来读取每个组件的标识信息。这些寄存器的值将提供关于组件的名称、类型、大小以及它们在ARM核心上的位置等信息。

然后,我们可以使用CIDR0-CIDR3寄存器来进一步确定每个组件的类型。通过读取这些寄存器的值,我们可以确定哪些类型的组件存在于ARM核心上。例如,如果CIDR0-CIDR3寄存器的值组合表示某个组件是一个内存管理单元(MMU),那么我们就可以将该组件归类为MMU类型。

ARM核心就像是一本书的章节,每个章节都是一个组件。Coresight的寄存器PIDR0-PIDR7以及外设识别寄存器就像是一本目录,告诉我们每个章节的名称和页码。而CIDR0-CIDR3寄存器就像是每个章节里面的标题,通过它们我们可以知道每个章节的标题是什么。

通过查看目录(Coresight的寄存器),我们可以知道这本书有哪些章节,它们分别在哪些页码(页数)。然后,通过阅读每个章节的标题(CIDR0-CIDR3寄存器),我们可以了解每个章节的内容大致是什么。

这样,我们就能够更好地了解这本书的结构和内容,以便进行阅读、理解或参考。同样的,通过使用Coresight的寄存器,我们可以更好地了解ARM核心的组件结构和功能,以便进行调试和优化等操作。

rom table, coresight组件,corelink组件

ROM TABLE

ROM TABLE是ARM系列SOC(System on a Chip)必须有的一个组件,它主要用于识别和调试组件。

ROM TABLE包含了用于调试的多种信息,例如调试寄存器的基地址、调试指令、版本信息等。 这些信息被存储在芯片出厂前,并在系统启动时被加载到芯片中。

- Debug ROM表:它包含了在调试过程中用到的指令,比如读取寄存器的指令、设置断点的指令等。这些指令在系统启动时会被加载到芯片中。

- Vector Table:它包含了异常向量表,即当系统发生异常时,程序会跳转到这个表中对应的异常处理程序。

- Breakpoint Table:它包含了断点地址表,即可以设置断点的地址列表。在调试过程中,当程序执行到断点地址时,程序会被暂停,从而帮助开发人员检查程序状态。

- Symbol Table:它包含了程序中定义的全局变量和函数地址列表。这些信息对于调试过程中进行变量访问和函数调用非常有用。

- Other Debug Information:除了上述提到的信息,ROM TABLE还可能包含其他调试信息,例如版本信息、调试寄存器的基地址等。

Coresight组件

Coresight组件是一种用于调试和追踪SOC芯片的工具,它可以帮助开发人员检查程序运行时的状态和数据,例如查看寄存器的值、设置断点、跟踪程序的执行路径等。通过Coresight组件,开发人员可以更好地了解程序运行时的情况,找到并解决问题。

CoreLink组件

CoreLink组件是ARM公司提供的一套IP核,用于实现片上通信和共享资源管理。它提供了一组通信和同步机制,以及一个统一的接口,使得多个处理核心可以相互通信并共享系统资源,从而形成一个完整的片上系统。CoreLink还包含了一系列用于调试和跟踪的组件,例如ETM(Embedded Trace Macrocell)和STIM(Serial Trace Injector),这些组件可以用于收集和分析系统运行时的数据,帮助开发人员调试和优化系统性能。

Coresight组件和CoreLink组件是不同的技术,它们的功能和用途也不同。Coresight主要用于实现SOC的调试和追踪功能,而CoreLink主要用于实现片上通信和共享资源管理。

-

寄存器

+关注

关注

31文章

5336浏览量

120224 -

ARM芯片

+关注

关注

1文章

125浏览量

21464 -

调试器

+关注

关注

1文章

303浏览量

23716 -

CoreSight

+关注

关注

0文章

6浏览量

7891 -

DFx

+关注

关注

0文章

35浏览量

10539

发布评论请先 登录

相关推荐

安川伺服辅助功能参数一览表

51单片机寄存器功能一览表

单片机怎么通过按键控制计时器的开始和停止_超详细!51单片机寄存器功能一览表...

为调试寄存器 DBGDRAR 设置的值错误

车载芯片安全寄存器的布局设计

芯片DFX:Coresight的寄存器一览

芯片DFX:Coresight的寄存器一览

评论