随着时间的推移摩尔定律逐渐趋于极限,人们迎来了后摩尔时代。封装技术即将成为摩尔定律的新拐点,为芯片集成的历史翻开了新的一页。

遥想当年,戈登·摩尔创造了摩尔定律,为半导体行业发展指明了一条罗马大道。不过,毕竟理论自1965年至今已有五十余年,节点已微缩至几近纳米极限,行业摩尔定律逐渐放缓,甚至有言道“摩尔定律已死”。

摆在现实的是,纳米节点转换越来越难了,物理极限越来越近了。处在后摩尔时代的企业只能默默面对纳米极限的逼近吗?不,摩尔定律探索中出现了新拐点,即封装技术。

封装技术成为摩尔定律的新拐点

摩尔定律到底是什么,封装技术和摩尔定律到底有什么关系?1965年起初,戈登·摩尔表示集成电路上可容纳的元器件数量约18个月便会增加一倍,后在1975年将这一定律修改为单位面积芯片上的晶体管数量每两年能实现翻番。

回望摩尔定律整个历史,让晶体管沟道进一步缩短,突破物理极限也曾先后经历多个瓶颈。首先碰到的便是半导体材料的限制,由此行业发明了电化学镀铜和机械平面化的双镶嵌结构技术;而后遇到了设备物理限制,Si栅极和SiO2栅极电介质材料被金属栅极和高K电介质取代;再到193nm节点以上,受到光刻技术限制,行业光刻技术得以发扬,在制程节点45nm-32nm下产生了浸没工艺、16nm-10nm下产生了多重曝光工艺、7nm-5nm则引入了极紫外线(EUV)工艺。

因此,可以看出,为了延续摩尔定律,专家绞尽脑汁想尽各种办法,包括改变半导体材料、改变整体结构、引入新的工艺。但不可否认的是,摩尔定律在近几年逐渐放缓。10nm、7nm、5nm……芯片制程节点越来越先进,芯片物理瓶颈也越来越难克服。

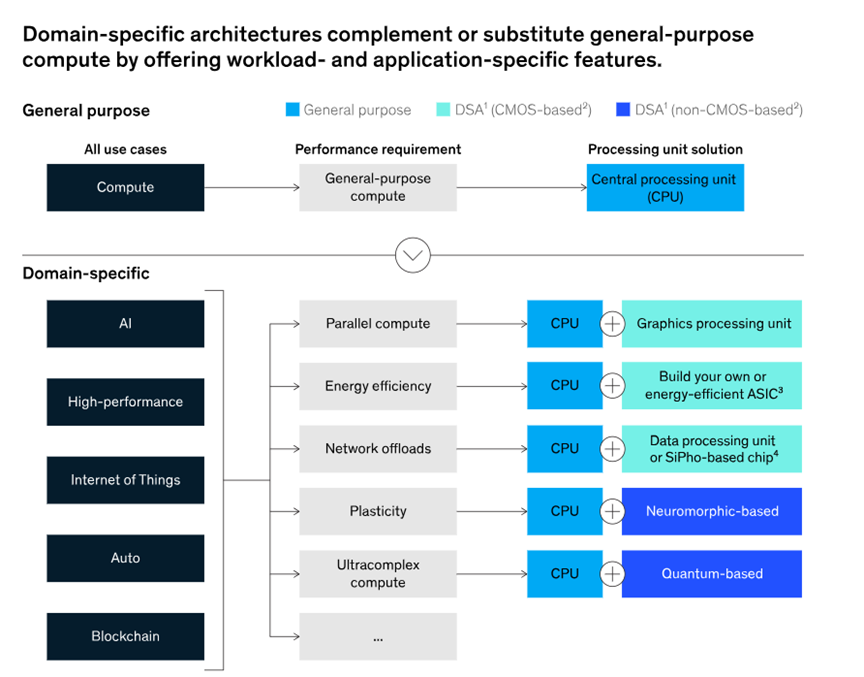

因此,业内专家指出了后摩尔时代的硅技术的发展方向。一种是继续采用“硅-冯诺依曼”范式,通过改变结构形成新型器件,使得摩尔定律能够继续;另一种则是采用类脑模式的新兴架构,利用3D封装模拟神经元特性,构建存算一体的计算,这种架构不仅低功耗,还拥有并行性。

那么封装究竟和摩尔定律有什么关系呢?

简单来说,封装能够减少芯片间的凸点间距,增大凸点密度。整体的密度越大,实际上也代表着单位面积上晶体管数量越密。所以说,封装虽然和摩尔定律没有直接关联,但却又影响着摩尔定律的发展。

封装技术正迈向新的凸点间距

封装技术是如何发展的?

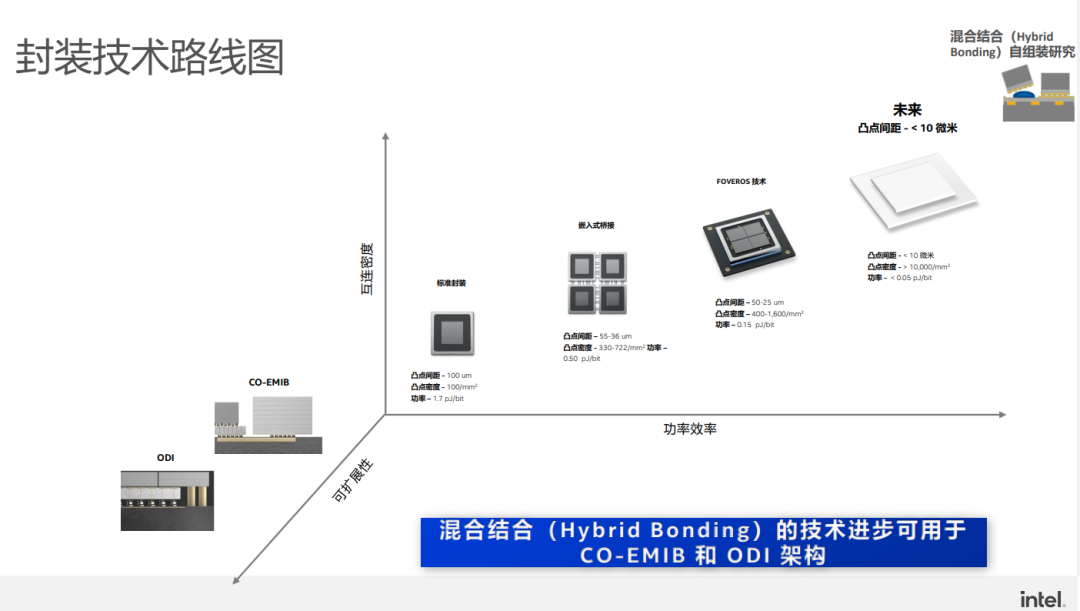

从标准封装到EMIB(嵌入式多管芯互联桥接)再到Foveros,凸点间距从100μm缩减到50-25μm。未来要做到小于10μm的凸点间距。

EMIB是一种2.5D高密度微缩技术,通过EMIB技术可以实现更好的导线密度。通过将硅中介层放入封装内,因而可进行局部高密度布线,并非全部芯片的高密度布线。利用EMIB技术,可将典型FCBGA(有机封装)的IO层提升至256-1024 IO/mm/层。这项技术能够实现55-36μm的凸点间距和每平方毫米330-722/m㎡的凸点密度,功率可以控制在0.5pJ/bit。

Foveros则是一种3D高密度微缩技术,如若在此基础上进行完美的设计,IO就甚至可以达到从400至10000 IO/mm²。这项技术能够实现50-25μm的凸点间距和400-1600/m㎡的凸点密度,功率可以控制在0.15pJ/bit。

既然目标是10μm以下,那么如何实现?答案是“混合结合”的Hybrid bonding技术。利用该技术不仅能够实现10μm凸点间距的愿景,还能使得凸点密度达到10000/m㎡,功率控制在0.05 pJ/bit。并且,混合结合技术可以使用与晶片到晶圆,也可以使用与晶圆到晶圆。

Hybrid bonding能够使两芯片间实现更多互连,也不必做扇入(fan-in)和扇出(fan-out)。有了更简单的电路,可以使用更低的电容,以降低通道的功率。

随着摩尔定律的继续推进,芯片的尺寸可能会变得越来越小,为了保证足够的带宽,必须要在导线上下功夫。整个小芯片尺寸变得越来越小,其实随着间距变得越来越短,传统基于焊料的技术已经快要到极限了,这就是为什么要使用全新的技术混合结合Hybrid bonding封装。

那么Hybrid Bonding到底和Foveros有什么区别,凭什么混合结合封装就能减少凸点间距?

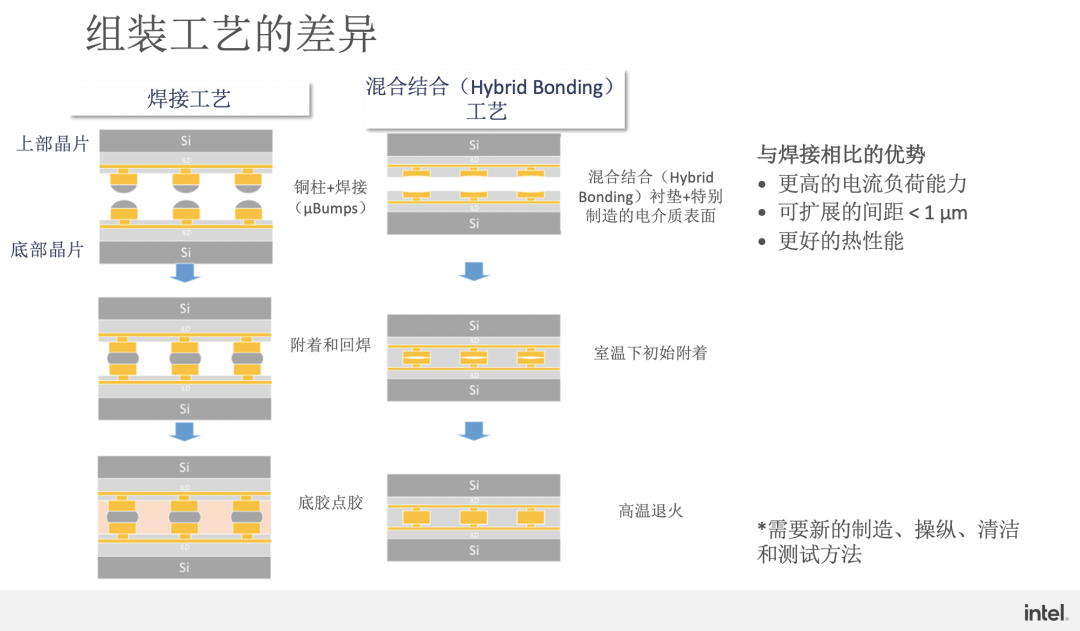

硅晶片分布在顶部和底部,中间则是带焊料的铜柱,将它们附着在一起和回焊,让它升温。这些芯片之间有不同的温度,需要熔化焊料,将其放在一起,进行连接和回焊,再制作电气接头。在这之后,进行底部填充胶的分配,将填充有环氧树脂的硅放入模具之间以确保它们密封并能够完成放入并组装。

Hybrid Bonding与Foveros的焊接工艺不同,与焊接技术相反,混合结合技术使电介质的芯片非常光滑,而不是有突出的凸点,甚至实际上还会略微凹陷。当采用混合结合技术将这两个组件放在一起时,不必升高温度,可以在室温粘合两个组件。在其相互附着后,再升高温度并进行退火,铜在这时会膨胀,从而形成电气连接。Swan强调,这是非常有用的,因为这样可获得更高的载流能力。

甚至可以将间距缩小到 10 微米以下。这样在这些接口之间获得了比底部填充和紧密的铜密度更好的热性能。不过,当使用混合结合技术时,将需要一种新的制造、清洁和测试方法。

实际上,这种更小的间距颇具吸引力,能够联动许多技术的进化。

封装技术是三位一体的

除了在功率效率和互连密度上的提升,封装技术还分出可扩展性这个维度。这一维度之上,包括Co-EMIB和ODI两个技术。

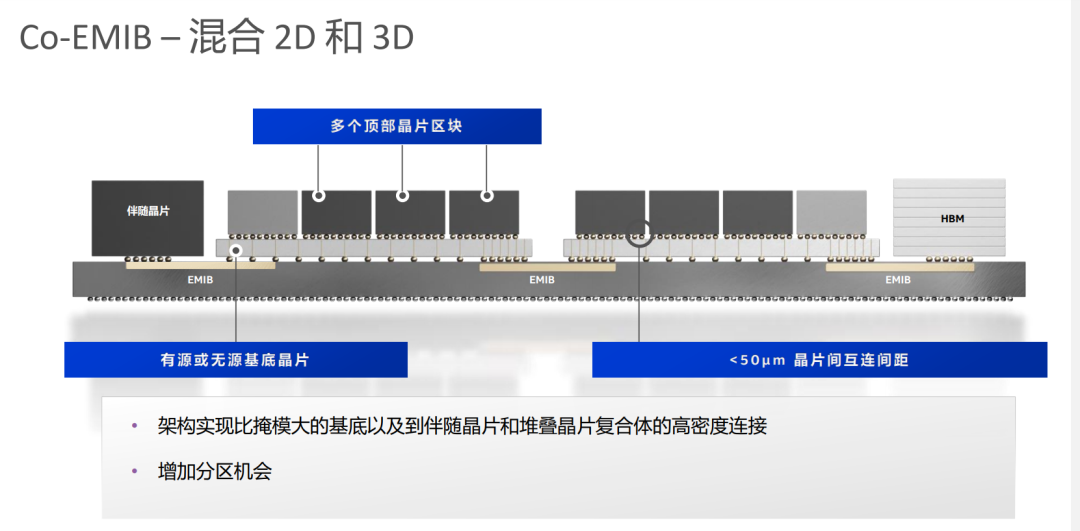

Co-EMIB是融合EMIB技术和Foveros技术的一种封装,是融合2.5D和3D的技术。如果将EMIB理解成水平方向,Foveros理解成垂直方向,那么Co-EMIB就是三位一体的兼顾两个方向的封装方式,能够真正发挥高密度微缩的效果。

可以说,可扩展的Co-EMIB的技术是发挥所有封装方式优势的平台,也是2.5D和3D封装技术碰撞交融、各自发挥优势的汇集地。

另一个颇具可扩展性的技术就是ODI(全方位互连技术)。根据此前的介绍,在常规的叠加方式下,下面的基础裸片必须是较大的,它要大于上面叠加的所有小芯片的总和。通过ODI技术可以改变这一点,两者之间可以进行更好的协调,并且可以上下做到面积统一。

总结

实际上现今封装技术,不仅达到了晶体管的级别,使得成为摩尔定律探索的新关键,还与未来新架构息息相关。

在摩尔定律逐渐逼近极限之时,未来集成电路行业在后摩尔时代不仅要着眼于半导体材料、结构和工艺,还要注意封装互连技术对晶体管的影响,或许这是未来破局的关键。

-

摩尔定律

+关注

关注

4文章

634浏览量

78995 -

封装

+关注

关注

126文章

7873浏览量

142891 -

半导体材料

+关注

关注

11文章

532浏览量

29558

原文标题:摩尔定律不会死去!这项技术将成为摩尔定律的拐点

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

击碎摩尔定律!英伟达和AMD将一年一款新品,均提及HBM和先进封装

后摩尔定律时代,提升集成芯片系统化能力的有效途径有哪些?

奇异摩尔专用DSA加速解决方案重塑人工智能与高性能计算

“自我实现的预言”摩尔定律,如何继续引领创新

封装技术会成为摩尔定律的未来吗?

半导体先进封装Wafer技术的深度解析

半导体行业能否走出低谷,中国影响几何?

摩尔定律的终结:芯片产业的下一个胜者法则是什么?

摩尔定律不会死去!这项技术将成为摩尔定律的拐点

摩尔定律不会死去!这项技术将成为摩尔定律的拐点

评论