Analog On Top的SOC如何做Top设计?

简介:

在片上系统(SOC)的世界里,vwin 运算(AOT)方法为设计过程带来了独特的风味。与数字逻辑处于顶端的传统方法不同,AOT颠覆了层次结构,模拟组件占据主导地位。本文旨在详细了解如何为AOT SOC设计Top,并在此过程中提供重要的见解和注意事项。

1.了解AOT SOC架构:

AOT SOC架构的特点是将模拟组件放在顶部,然后是下面的数字逻辑块。这种布置允许更好的连接性、减少噪声干扰和最小化信号退化。关键模拟组件包括ADC、DAC、PLL、LDO和特定于应用程序的自定义模拟模块。

2.确定模拟性能要求:

在深入顶层设计之前,确定模拟组件的性能要求至关重要。必须彻底分析噪声、线性、带宽、功耗和热特性等参数。仔细考虑这些要求将有助于做出适当的设计决策。

3.定义通信接口:

接下来,需要定义数字域和模拟域之间的通信接口。这涉及到选择合适的协议并设计用于电压和信号转换的缓冲器或电平移位器。重要的是要确保数字逻辑在适当的电压电平下工作,并且在转换期间信号不被破坏。

4.设计模拟块:

设计模拟块包括选择合适的电路拓扑、确定晶体管大小和设计布局结构。模拟块应小心放置和布线,以最大限度地减少寄生效应并确保信号完整性。原理图捕获工具,如Cadence Virtuoso,可用于创建初始电路设计。

5.布局设计:

顶部布局应考虑模拟组件的独特要求。必须结合足够的间距、屏蔽和专门的模拟电源/接地网络设计。AOT SOC对敏感的模拟信号给予更高的优先级,因此必须小心将任何可能降低性能的潜在耦合或串扰问题降至最低。

6.配电网规划:

由于模拟部件对噪声的敏感性,AOT SOC的PDN至关重要。每个模拟块都需要一个专用的LDO或一个隔离的电源域,以确保干净稳定的电源。应战略性地放置适当的去耦电容器和电感器,以抑制噪声并保持信号完整性。

7.信号完整性和串扰分析:

为了保证最佳性能,必须在AOT SOC设计中对信号完整性进行深入分析。EMXPert和Spice等工具可以帮助识别潜在的串扰和噪声耦合问题。在分析过程中发现的任何设计问题都应及时解决,同时牢记对模拟性能的影响。

8.模拟和验证:

仿真工具,如Cadence Spectre或Synopsys HSPICE,对于验证整体系统级性能至关重要。每个模拟块都应该单独模拟,然后必须将整个SOC作为一个整体进行模拟,以评估模拟域和数字域之间的相互作用。模拟行为建模(ABM)可以用于快速准确的模拟。

9.制造设计(DFM):

在AOT SOC中,不应忽视DFM考虑因素。必须注意确保模拟块满足工艺变化,对温度变化具有鲁棒性,并保持制造成品率。适当的灵敏度分析和蒙特卡罗模拟将有助于识别任何需要注意的关键领域。

10.硅后验证:

一旦SOC设计完成,就必须进行硅后验证,以验证模拟性能是否符合所需规范。应仔细规划测试设置和方法,以确保准确测量噪声、线性和效率等参数,为SOC设计的成功提供证据。

结论:

为模拟On Top SOC设计Top需要对细节给予细致的关注,并对模拟性能要求有全面的了解。从确定性能规范到设计布局和进行硅后验证,每一步都在确保SOC的最佳性能方面发挥着至关重要的作用。通过遵循本文提供的指导方针,设计师可以有效应对挑战,并成功实现AOT SOC。

-

片上系统

+关注

关注

0文章

186浏览量

26806 -

隔离电源

+关注

关注

6文章

280浏览量

36300 -

DFM

+关注

关注

8文章

463浏览量

28191

发布评论请先 登录

相关推荐

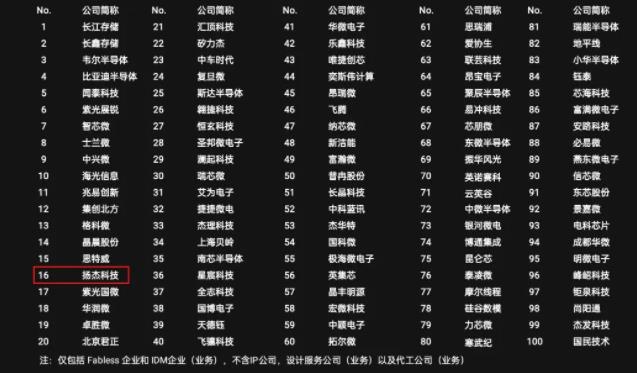

扬杰科技登榜“2024中国半导体企业TOP100”

Analog On Top的SOC如何做Top设计?

Analog On Top的SOC如何做Top设计?

评论