针对DFX设计,Vivado提供了命令report_pr_configuration_analysis,该命令会从设计复杂度、时钟和时序等方面对其进行分析。使用该命令时,我们主要会用到其中3个选项:-complexity、-clocking和-timing。

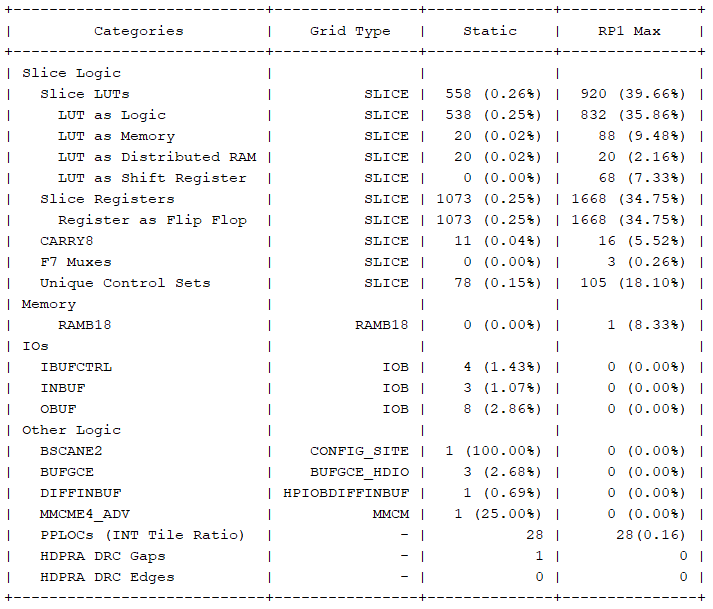

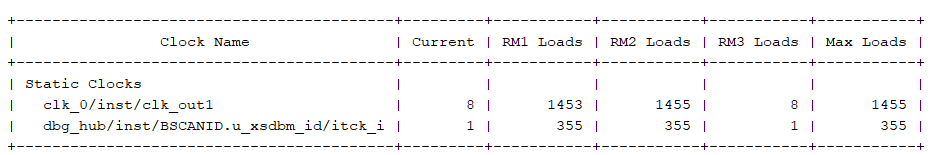

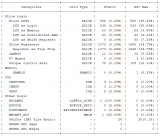

选项-complexity聚焦在设计的资源使用情况,会给出指定RP下各RM的资源使用情况,同时给出各RM之间相比各种资源使用量的最大值,这需要用到选项-cells和-dcps。其中-cells指定RP的名字,而-dcps则会列出各RM所在的dcp文件。如下图所示,Static列显示了静态区的资源利用情况,RP1 Max给出了RP1各RM相比各种资源使用量的最大值。这一点可从报告的第二部分进行验证。报告的第二部分是对各RM资源利用情况的比较。

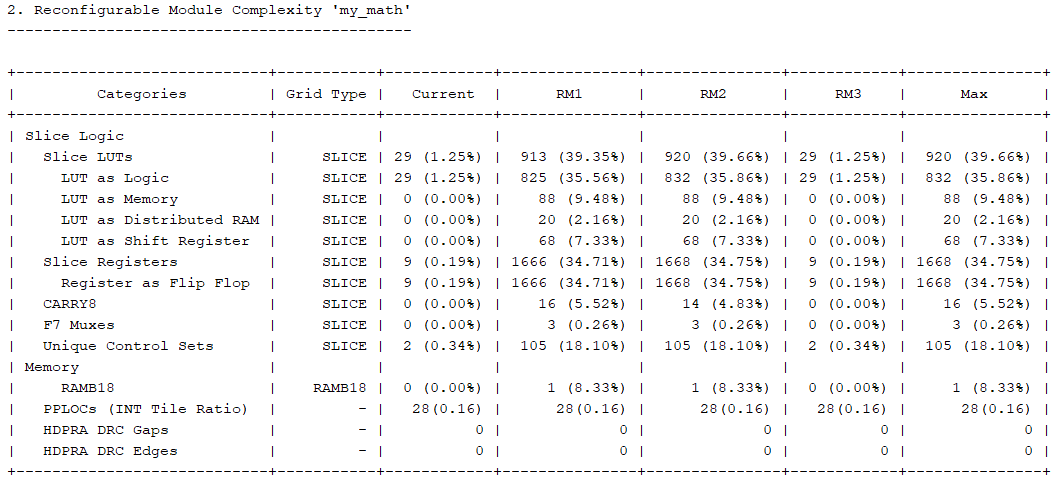

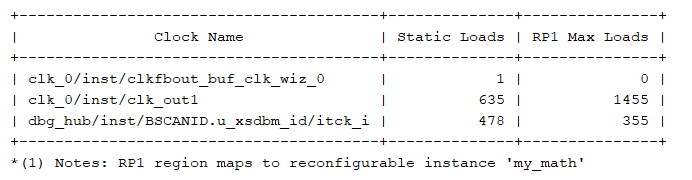

选项-clocking聚焦在时钟的使用情况上。会给出各时钟在静态区和每个RM的负载个数,如下图所示。

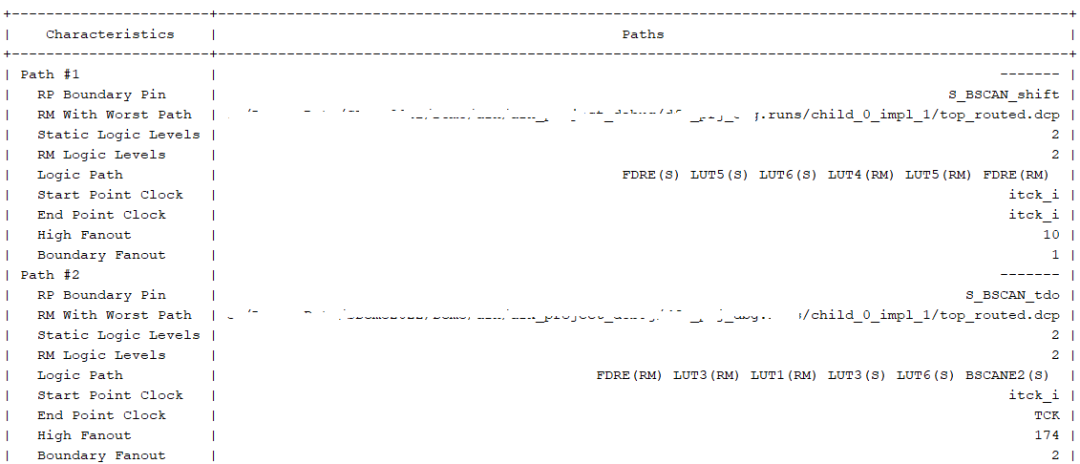

选项-timing聚焦在时序上,给出各RM和静态区接口关键路径时序,如下图所示。

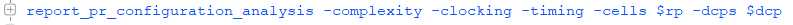

为了对各RM进行比较,使用report_pr_configuration_analysis时,要添加选项-cells和-dcps。由于该命令会逐次打开所有指定的dcp文件,所以会比较耗时,为此,确保每打开一个dcp,所要分析的条目全部执行。这里给出该命令的最佳使用方式,如下图所示,即同时添加-complexity、-clocking和-timing这3个选项。

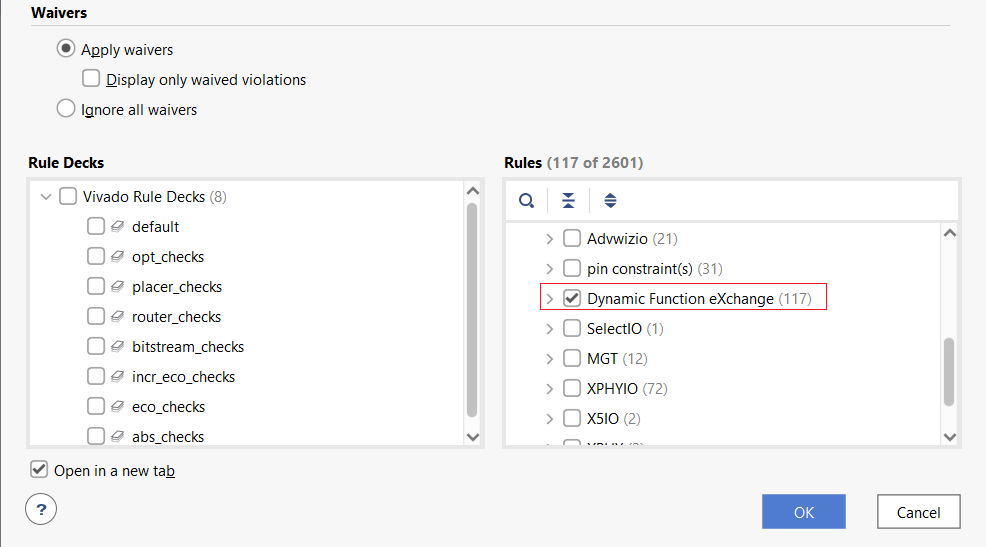

我们还可以用report_drc对DFX设计进行分析,如下图所示,点击Vivado左侧导航栏的Report DRC后会弹出如下图所示界面,确定勾选DFX。建议在综合之后执行该命令,这样可以尽早发现设计存在的问题。

我们还可以用report_drc对DFX设计进行分析,如下图所示,点击Vivado左侧导航栏的Report DRC后会弹出如下图所示界面,确定勾选DFX。建议在综合之后执行该命令,这样可以尽早发现设计存在的问题。

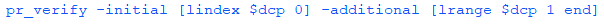

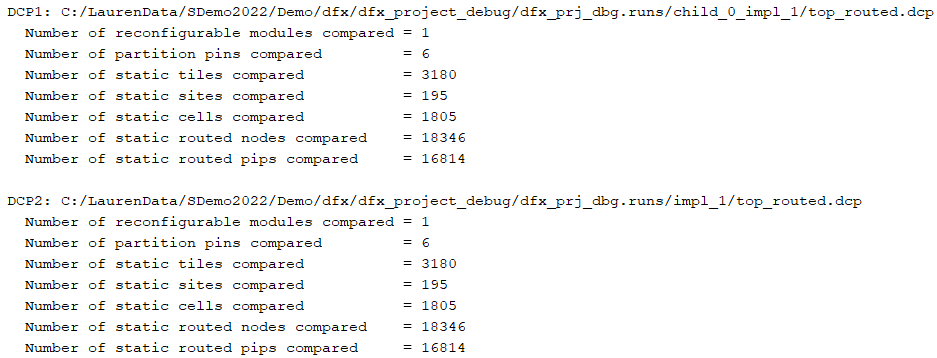

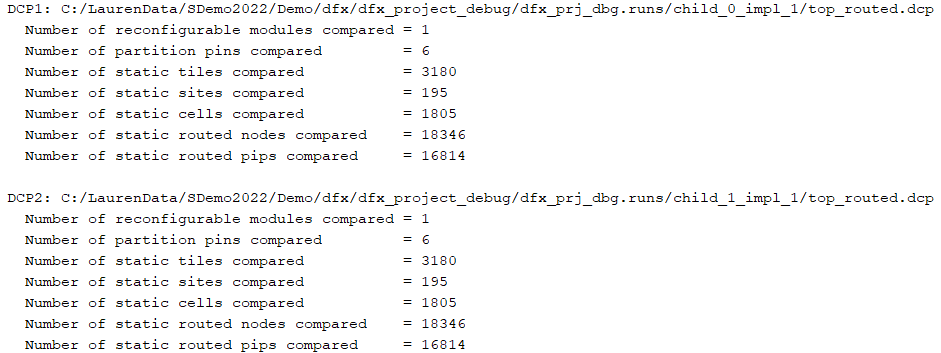

对于DFX设计,所有configuration的静态区应该是完全一致的,因为Parent Run一旦执行完毕,工具就会在布线层面锁定静态区供后续childrun使用。我们可借助命令pr_verify来验证各configuration对应的静态区是完全一致的,具体命令如下:

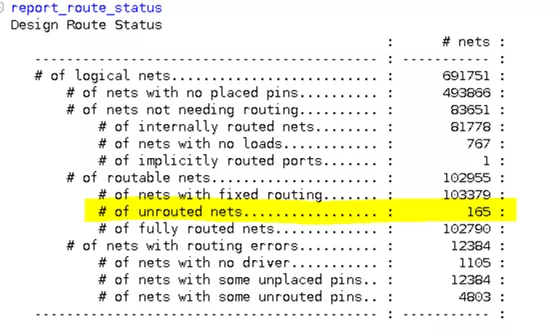

该命令生成报告如下:

该命令生成报告如下:

编辑:黄飞

-

时钟

+关注

关注

10文章

1733浏览量

131445 -

时序

+关注

关注

5文章

387浏览量

37317 -

Vivado

+关注

关注

19文章

812浏览量

66470

发布评论请先 登录

相关推荐

DFX设计如何分析

招兼职dfx、dfm培训讲师

硬件电路设计中常见的DFX

简述DFX理念与产品研发(一)

简要分析DFX实施流程

HarmonyOS对DFX能力的要求

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?

DFX设计如何分析

DFX设计如何分析

评论