日本佳能一直在投资纳米压印(Nano-imprint Lithography,NIL)这种新的芯片制造技术,并宣布推出“FPA-1200NZ2C”纳米压印半导体制造设备集群。计划将新型芯片制造设备的价格定为阿斯麦极紫外***的十分之一左右,从而在***领域取得进展。

佳能首席执行官御手洗富士夫(Fujio Mitarai)表示,基于NIL的新型芯片制造设备售价将比阿斯麦(ASML)的极紫外光刻(EUV)设备少一位数,虽然最终的定价目前还没有敲定,但是可以预见将为小型芯片制造商生产先进芯片开辟出一条新的道路。

御手洗富士夫说到:“我不认为纳米压印技术会取代EUV,但我相信这将创造新的机会和需求,而且我们已经收到了很多客户的咨询。”

据DIGITIMES此前消息,SK海力士2023年引进佳能纳米压印设备,正在进行测试与研发,目标在2025年左右将该设备用于3D NAND量产。有业内人士表示:“与EUV相比,纳米压印技术形成图案的自由度较低,因此预计将优先用于生产维持一定图案的NAND型闪存。”SK海力士开始采购设备也是因为这个原因。

纳米压印技术是EUV技术的低成本替代品,可⽤更小的功率形成精细图案,相比传统的EUV投影曝光设备在形成图案时对应的功耗可降低至1/10。据此前消息,ASML的新旗舰***价值约4亿美元,其功耗则可能飙升至两百万瓦,比当前***的额定耗电量还要高出一倍。在拥有全球最多***的台积电,80台功耗一百万瓦的***已让台积电能源消耗占到全台湾地区的12.5%。

01

什么是纳米压印技术

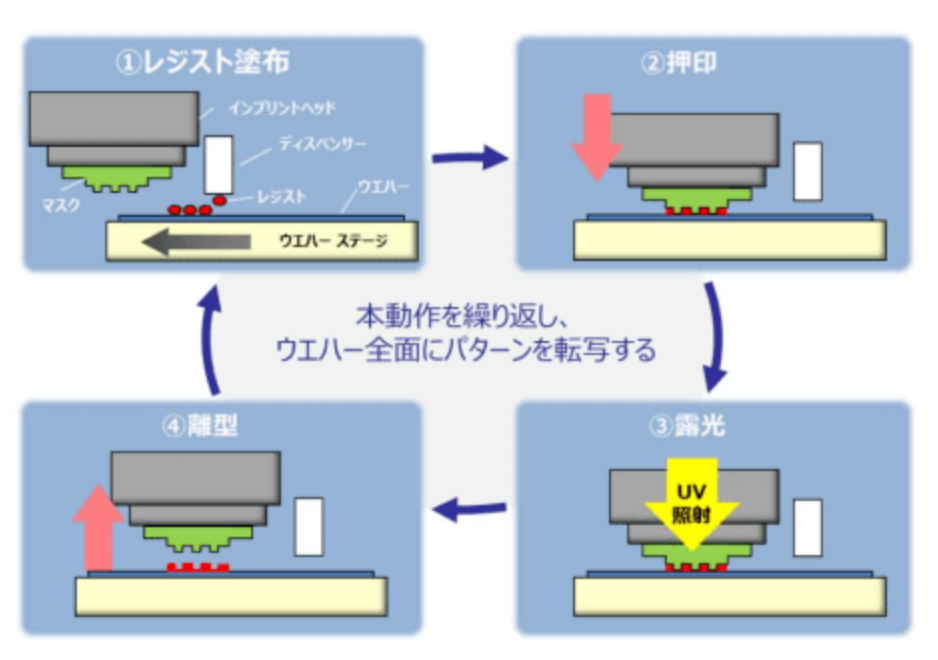

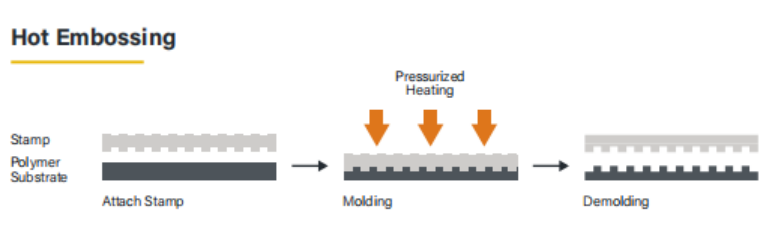

纳米压印是一种微纳加工技术,它采用传统机械模具微复型原理,能够代替传统且复杂的光学光刻技术。简单而言,像盖章一样造芯片,把栅极长度只有几纳米的电路刻在印章上,再将印章盖在橡皮泥上,得到与印章相反的图案,经过脱模就能够得到一颗芯片,这里的橡皮泥是指纳米压印胶,印章即模板。

要理解纳米压印技术,可以先跟光刻技术做对比。目前芯片制造最主要的方式是光学投影式光刻,类似于胶片相机洗印照片时,将胶片上的的图像印在相纸上,只不过在光刻过程中,“胶片”变成了掩膜版,“相纸”变成了涂抹了光刻胶(PR)的硅片。

刻有电路图案的掩膜版,经过***特定波长的光学系统投影后被缩小,再“曝光”到硅片上,光刻胶会发生性质变化,从而将掩膜版上的图案精确的复制到硅片上。最后一步就是“显影”,也就是在硅晶圆上喷洒显影液,把多余的光刻胶洗掉,再用刻蚀机把没有光刻胶覆盖的刻蚀掉。

总的来说,光刻的就是利用光线将电路图案“印刷”到晶圆上,是芯片制造过程中最重要、最复杂也最昂贵的工艺步骤,其成本占总生产成本的30%以上。以ASML顶级的EUV***为例,它需要功率极高又稳定的光源,这就对成像反射镜头的制作工艺和机械精度提出了极高要求,所以价格昂贵。

而纳米压印技术,就是要抛弃***里面复杂、昂贵的光学系统,直接把带有电路设计图的膜版压到硅片上:首先将电路设计图或其他图形通过高温加热或者紫外光线辐射的方式转移到某一类材质的膜版上;然后再将图案刻印到涂抹了压印胶的硅片或其他所需材料上,压印胶的作用类似于光刻胶但成分各有不同;最后再进行刻蚀即可得到成品。

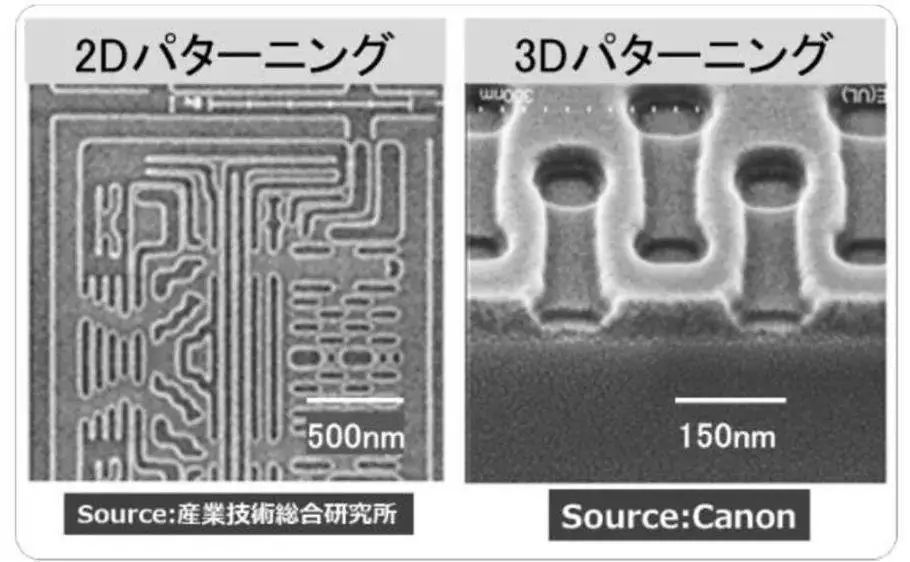

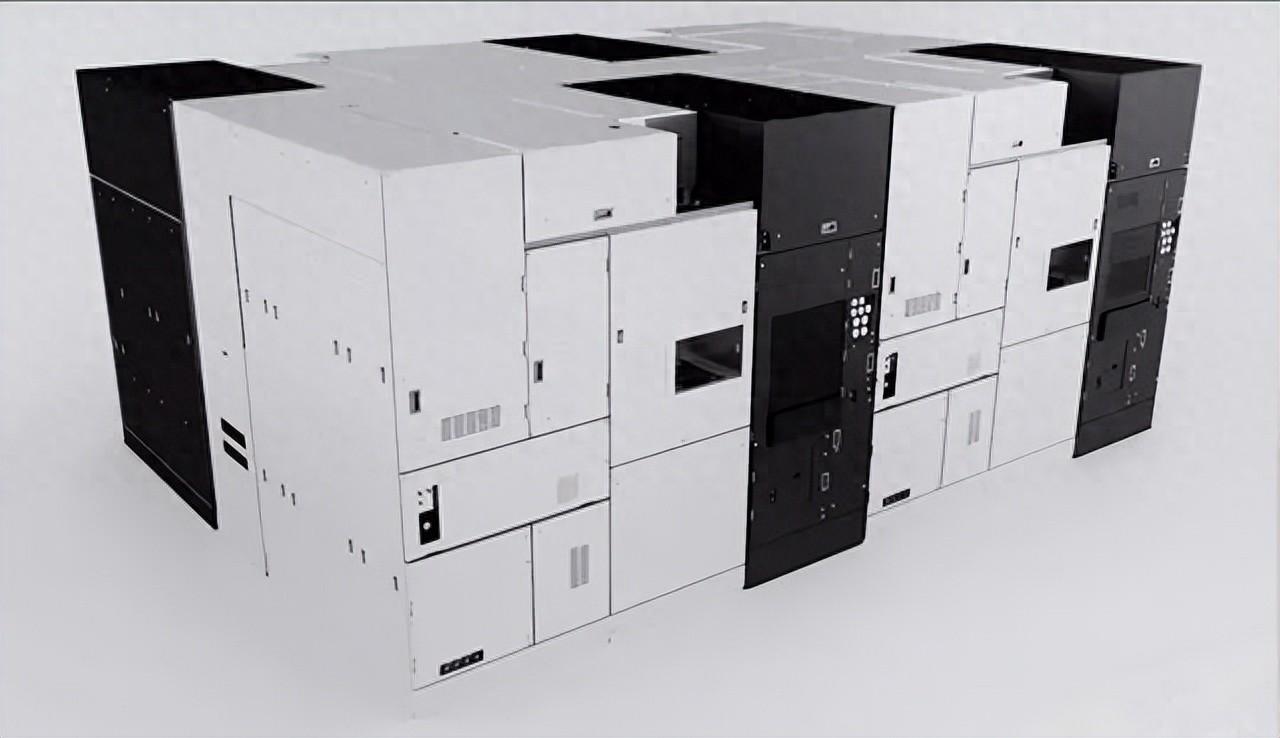

佳能的纳米压印设备用自家的喷墨技术将适量的抗蚀剂添加到合适的位置,最后将掩模印在涂有抗蚀剂的晶圆上进⾏精准曝光。单⼀压印即可形成复杂的2D或3D电路图。官方称该设备结构简单,由于不需要EUV的大规模特殊波长光学系统和真空腔,所以基于NIL技术的设备得以大幅缩小体积。

在半导体制造领域,纳米压印技术展现出了对传统光刻技术的重大挑战,以其独特的低成本和高精度特点,吸引了行业内外的广泛关注。纳米压印技术的优点之一是其低成本,由于它省去了昂贵的光学光刻和化学物质的使用,因此可以大大降低制造成本。此外,通过使用模板压印的方式,可以同时处理多个芯片,实现大规模生产。而且,由于该技术主要使用的是电子衍射,克服了传统光科技的分辨率问题,因此能比传统光刻技术达到更大分辨率。

纳米压印替代的是光刻环节,只有光刻的步骤被纳米压抑技术代替,其他的刻蚀、离子注入、薄膜沉积这些标准的芯片制造工艺是完全兼容的,能很好的接入现有产业,不用推翻重来。未来当光学光刻真正达到极限难以向前时,纳米压印技术或将是一条值得期待的路线,而那时,芯片制造或许也会迎来全新的范式,一切都会被颠覆。

02

纳米压印并非没有挑战

纳米压印的核心是一个简单的概念,以其直接压印方法绕过了其中一些障碍,但是其执行在技术上可能具有挑战性。

最大的缺点莫过于膜版的制作。在传统***中,光掩膜板不和硅片直接接触,又是用光学投影倍缩到硅片上,因此光掩膜版可以按照4:1的比例做成比较大的膜版。而纳米压印是“盖章”,必须要做到1:1精确的膜版,这种高质量的压印膜版跟造芯片难度一样,同样需要复杂的制备工艺,因此也有业内人士称其为“套娃”,是一种不必要的浪费。

另一个缺点是大规模生产中的时间成本问题。虽然和EUV比起来不算贵,但是从芯片产出的良率和每小时产量来看,纳米压印可能会更“贵”。根据佳能员工对上一代纳米压印设备集群的论文数据显示,每小时纳米压印可以处理90张硅片(90WPH),而ASML的1980Di***一小时的产量已经达到275以上。

纳米压印每一次压印都需要经过喷涂滴状压印胶、定位、压模、光照固化再脱模,每一步都需要防止空气进入,还要确保压印瞬间对芯片局部加热,使纳米级形变过程中能严丝合缝地贴合掩膜版,这一过程中其实在实际操作中更为繁琐。

产能短板之外,纳米压印的良率也值得关注。任何物理接触施压都会造成产品和模板的变形,因为很难保证不同区域压印胶的填充和溢出率,而且膜版磨损得很快,就需要频繁更换,成本不见得低,所以图形复杂的一般性集成电路不适合这一技术。

佳能机器更像是为小型芯片生产商提供的选择,同时也能让台积电和三星电子等大型代工商更容易生产小批量芯片,从而节约成本。

03

佳能“弯道超车”?

纳米压印最早出现于1996年,佳能此前一直专注于制造普通芯片,2014年开始大力投资纳米印记技术,以1.5亿美金收购了主攻纳米压印技术的分子压模公司(Molecular Imprints Inc.);从2017年开始,佳能就与铠侠(Kioxia)以及半导体零组件制造商大日本印刷株式会社(DNP)合作,研发基于纳米压印的量产技术。

佳能尤其关注纳米压印在存储和逻辑芯片的制造应用,这也跟自己在***领域被压着打的现状有关。全球前道设备***市场已基本被ASML、尼康、佳能所垄断,去年三家***出货量达551台,市场规模达189亿美元,但这其中有345台是来自ASML,占据了82%以上的市场。

独占鳌头的ASML也是唯一有顶级EUV***的供应商,其在EUV上的成功,也彻底断绝了尼康、佳能一切冲击高端的企图。导致佳能只能选择主要做i-line、KrF两类***,想要改变这一格局,佳能只能押注了另一条并行的赛道。

之前铠侠等一些日本半导体厂商曾尝试使用该技术来替换EUV,但因为内部颗粒污染、良率过低等问题没能实现商业化,看来佳能可能解决了这些问题。而这次佳能发布的“FPA-1200NZ2C”设备的环境控制新技术可抑制内部细颗粒的产生和污染,实现多层半导体制造所需的高精度对准,并减少由颗粒引起的缺陷,从而可以形成微小且复杂的电路。

佳能称该设备可实现最小线宽14nm的图案化,相当于生产目前最先进的逻辑半导体所需的5nm节点。此外,随着掩模技术的进一步改进,有望实现最小线宽为10nm的电路图案,相当于2nm节点。

据悉,佳能正在建设自己的第一家纳米压印设备工厂,预计将在2025年上线。而值得一提的是,台积电和三星代工都计划将于2025年开始量产自己2nm工艺芯片,对于NIL设备究竟是否能威胁到ASML EUV的市场,我们将拭目以待。

在半导体制造的高科技世界中,在纳米尺度上创建复杂图案的能力至关重要。随着对更小、更快、更高效的电子设备的需求不断增长,对先进光刻技术的需求也在增加。但是想成为主流光刻技术的替代路线,不是高投入就能“弯道超车”,还需要上游原料技术迭代、下游应用端等共同合作、打磨,最终才能有可靠而成熟的纳米压印产业。就像***从造出来的那刻起,才算是来到真正的起点。

在半导体制造领域,光刻技术一直是最核心、最关键的技术之一。近年来,随着科技的飞速发展,芯片的制程技术节节攀升,对光刻技术的要求也越来越高。

佳能纳米压印光刻技术的出现,无疑给半导体制造行业带来了新的希望。长期以来,ASML EUV***在光刻技术领域一直处于垄断地位,而佳能纳米压印光刻技术的出现,有望打破这一局面,使芯片制造更加多元化,从而推动整个行业的发展。

-

佳能

+关注

关注

2文章

388浏览量

39585 -

ASML

+关注

关注

7文章

718浏览量

41227 -

纳米压印

+关注

关注

0文章

9浏览量

6472

原文标题:佳能押注纳米压印技术 挑战光刻机老大ASML

文章出处:【微信号:WW_CGQJS,微信公众号:传感器技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

纳米压印光刻技术应用在即,能否掀起芯片制造革命?

7纳米工艺面临的各种挑战与解决方案

今日看点丨TCL收购LGD广州厂;佳能首次出货纳米压印光刻机

荷兰纳米压印技术公司Morphotonics获1000万美元融资

ASML创始人离世!

ASML光刻机技术的领航者,挑战与机遇并存

佳能预计到2024年出货纳米压印光刻机

佳能推出5nm芯片制造设备,纳米压印技术重塑半导体竞争格局

台积电的1纳米技术挑战与成本压力的博弈

纳米技术的特点 纳米技术有哪些用途

ASML为什么能在EUV领域获胜?

佳能押注纳米压印技术 挑战***老大ASML

佳能押注纳米压印技术 挑战***老大ASML

评论