ram冲突是几乎每颗芯片都需要关注的问题,部分场景下,ram访问冲突不容易验证到,容易造成芯片bug。ram访问冲突的类型通常有访问接口冲突和访问地址冲突。

术语解释:1r1w ram表示ram存在一个写口和一个读口,一共2个端口。1rw ram表示ram只有一个端口,此端口能写能读,同一个周期不能同时读写。1r1rw ram表示存在2个端口,其中一个端口只支持读操作,另外一个端口支持写操作和读操作(不能同时读写)。下文中的Logic访问指的由硬件逻辑发起的访问。csr表示可配置模块, 其对应的soft_access通常是由软件发起的对ram的访问,可能是读操作,也可能是写操作。

1、访问接口冲突

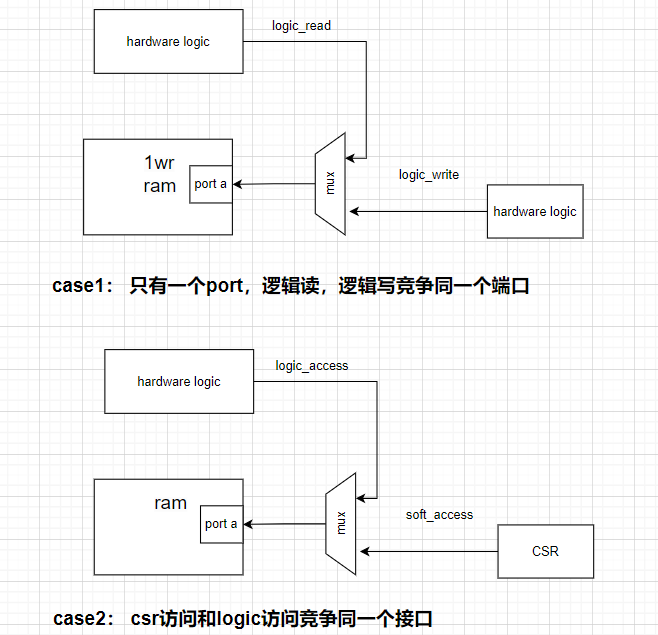

接口冲突,即多个访问请求同时访问一个ram的端口,例下图所示,logic 访问和soft访问同时竞争同一个端口。Case1所示为1rw ram(只有一个端口,能读能写),逻辑读和逻辑写同时竞争一个端口。Case2所示ram(可以是多个端口的ram),逻辑访问(读or写)和软件(写or读)访问同时竞争一个端口。

危害:接口冲突类型中,如果某一个访问存在高优先级,那么低优先级访问可能一直无法响应。轻则导致访问失败,重则模块挂死。

解决方案:高优先级访问接口需要控制连续访问次数,必须在一定时间内插入空拍。

2、访问地址冲突

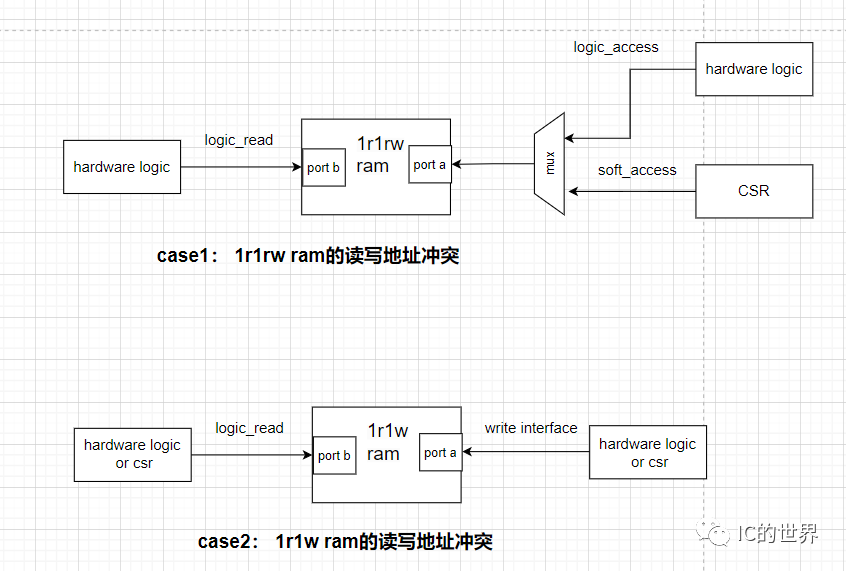

我们以1r1w的ram和1R1RW的ram为例进行讲解。如图所示:访问地址冲突,指的是读操作和写操作同时访问且地址相同。注意:此处的同时并不一定是同一个周期,同时指的是从ram读接口收到读操作直到返回读数据的若干个周期内(一般是1~3周期)。例如T0 clk,ram收到对addr(0x10)的读操作,T1 clk,读数据还未返回,此时ram收到对addr(0x10)的写操作,这种也算读写地址冲突。

危害:发送读写地址冲突时,读返回的数据可能不符合期望,读返回的可能是不确定值,可能是新值(写操作写入的值),也可能是旧值(不同厂家不同类型的ram响应因为不一样),部分厂家支持ram定制返回新值或者旧值,部分厂家ram返回的就是不确定值。读到不确定值明显会影响模块功能。

解决方案:在ram访问接口添加保护模块。

如果读返回需要新值,则在发送地址冲突时,将写操作的写数据转移给读返回。

如果读返回需要旧值,(比较少见)

定制读返回旧值的ram

添加冲突保护模块,发生地址冲突时,对写操作进行反压,此方案需要应用场景允许

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50711浏览量

423105 -

接口

+关注

关注

33文章

8573浏览量

151007 -

IC设计

+关注

关注

38文章

1295浏览量

103914 -

RAM

+关注

关注

8文章

1368浏览量

114638

原文标题:IC设计:常见的ram访问冲突【必学】

文章出处:【微信号:FPGA_Study,微信公众号:FPGA自习室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IC设计:常见的ram访问冲突

IC设计:常见的ram访问冲突

评论