近年来,随着晶圆级封装技术的不断提升,众多芯片设计及封测公司开始思考并尝试采用晶圆级封装技术替代传统封装。其中HRP(HeatRe-distributionPackaging)晶圆级先进封装工艺技术的研究,由深圳市华芯邦科技有限公司(Hotchip)提出,可解决元器件散热、可靠性、成本、器件尺寸等问题,是替代传统封装技术解决方案之一。本文总结了HRP工艺的封装特点和优势,详细介绍其工艺实现路线,为传统封装技术替代提供解决方案。

1 传统封装技术及其弊端介绍

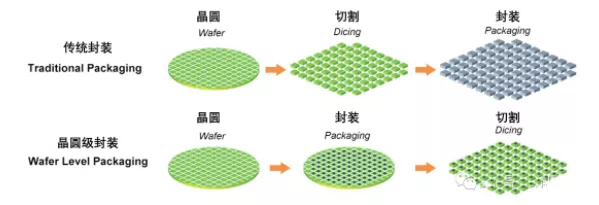

集成电路封装是半导体器件制作的最后一步。传统的芯片封装是指将制作好的晶粒嵌入具有保护作用的塑料、金属或陶瓷壳体中,并与外界电路及其他元器件连接的过程。此过程需要借助银浆或其他胶水将晶粒粘接固定在引线框架上,通过引线键合实现芯片输入输出端口与引线框架引脚实现电气互联,再进行模压塑封、陶瓷烧结或采用金属壳体将晶粒包覆起来,最后进行切割、测试完成芯片封装(如图1)。

图1 传统封装工艺流程

图1 传统封装工艺流程

此传统封装技术使得元器件存在以下弊端:

(1)散热问题。芯片散热主要途径有:

a. 芯片内部热量通过硅衬底、导电银浆、引线框架、芯片管脚、焊接锡膏、电路基板进行散热,散热路径 长,热阻高,散热效果一般。

b.芯片内部产生的热量通过电气互联线导热至引线 框架上,再通过引线框架引脚及焊接锡膏导热到电路基板上进行散热。通常电气互联线为铜线,线径为0.8~1.2mil,线径小、路径长,导热能力有限。散热效果一般。

c.芯片产生的热量散发到外壳包封的塑胶、陶瓷或金属包封壳体散热。塑胶包封壳体导热系数低,散热能力差。而陶瓷或金属壳体导热系数较好,但是同时也带来高昂的成本。

图2 传统心态封装结果

图2 传统心态封装结果

(2)可靠性问题。

图3 引线键合线径受损

图3 引线键合线径受损

(如图2)为传统芯片封装结构,每颗芯片由几根、几十根甚至上百根键合线实现晶粒与引线框架引脚的电气互联。引线键合工艺因焊线瓷嘴磨损、焊线参数匹配性等因素容易导致键合线焊球颈部受损(如图3所示)。

而塑封材料、晶粒、键合线、引线框架由于不同材料热膨胀系数不一样,在应用端SMT高温过炉或产品使用过程中发热,热应力导致键合线受损部位断开,导致器件失效。塑封器件因塑封材料容易吸潮,不同封装材料结合面存在缝隙也容易导致水汽进入,在SMT工艺及产品使用过程中,热应力和湿应力的双重作用下将加速器件失效。

(3)成本问题。

芯片封装经过晶粒固定、引线键合、AOI检查、模压、电镀、切割、测试工序,工艺流程长,生产效率慢,需要投入高额的设备成本、人工成本及材料成本,使得产品成本居高不下。

(4)器件尺寸大,阻碍产品微型化问题。芯片封装需要预留足够的引线键合空间,完成引线键合后,还需要进行塑封,使得器件尺寸远大于晶粒尺寸,对于器件或产品尺寸微型化造成了阻碍。 基于以上传统封装存在的弊端,我们进行了深入的技术研究,采用HRP晶圆级先进封装技术替代传统封装技术,有效解决产品散热、可靠性、成本、产品尺寸微型化等问题。

2 HRP工艺介绍

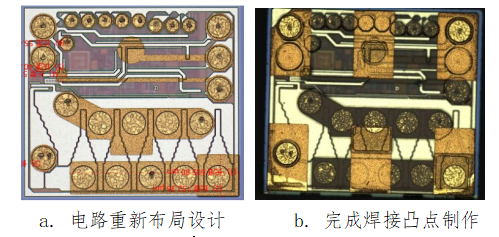

HRP旨在依据芯片电流大小、发热量、输入输出端口电路连接设计等,对芯片做线路层重构设计,并制作焊接凸点。主要设计内容为,依据电流大小、发热量及散热要求,设计符合要求的线宽、线距、线厚,确保芯片电学、热学特性达到设计需求。依据输入输出端口电路连接进行重新设计,简化线路及焊接凸点制作。

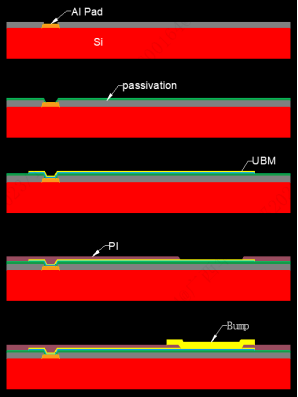

图4 HRP工艺流程图

图4 HRP工艺流程图

2.1 HRP工艺技术路线 HRP的工艺路线为使用物理气相沉积(PVD)制作UBM层,接着通过光刻、电镀和蚀刻工艺完重构电路布线。 HRP具体的工艺过程如图4所示。首先在Wafer上沉积一层金属薄膜(UBM),沉积方法可用物理气相沉积(PVD)或者化学气相沉积(CVD),沉积金属可选择Ti、Au、Cu等的一种或两种。随后在其上涂敷光刻胶,将设计好的图案或路线通过光刻技术“刻画”在光刻胶上,然后通过电镀或化学镀的方法把图案或线路进行金属化,最后在其上涂敷一层PI绝缘层,作为金属层间绝缘阻隔,在所需制作焊接凸点区域开窗预留凸点制作位置。完成PI层制作后,接着通过UBM层制作、光刻、电镀、蚀刻完成焊接凸点制作,也可以通过焊料印刷的方式制作焊接凸点。依据所需要制作的电路层数,不断重复以上步骤就可以获得所需的多层HRP。

HRP工艺是在晶圆上进行设计制作,随着所需的HRP完成,芯片的焊接区域也已按照设计所需生成,将晶圆进行划片后即可得到一颗颗的芯。以往的传统封装工艺技术,在完成晶圆划片后,还要进行后到器件级封装,即晶粒固定、引线键合、模压塑封、电镀、切割、测试等工序,才能贴装到PCB板上组装使用。而HRP则无需再进行后道的封装,而是将芯片以倒装(Flip Chip)的方式焊接组装在PCB板上,极大地缩短了互联长度,减小了RC延迟,有效的提升了器件的电性能。

2.2 HRP工艺特点

基于HRP晶圆级先进封装技术对芯片进行了电学、热学的电路设计重构,并直接倒装焊接在PCB板上,其具有如下特点:

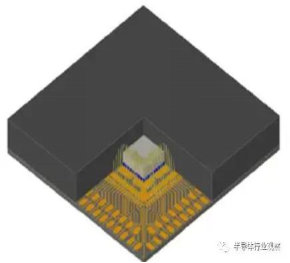

图5 HRP封装结构

图5 HRP封装结构

(1)散热能力好。如图5所示,电路重构设计在芯片表面设计了大面积金属布局,并在特定位置设计较大尺寸的焊接凸点,最终直接倒装焊接在PCB上,其散热路径为直接通过重构电路、焊接凸点、焊接锡膏即可将热量传导到PCB上,且均为大面积的金属导热,导热系数高,散热路径短,从而带来了较好的散热性能。经测试对比,相同芯片,采用HRP晶圆级封装技术替代传统的封装技术,使用过程中,达到热稳态后,其温度比传统封装产品低40%以上。

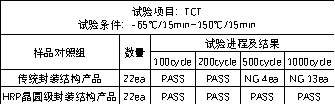

(2)可靠性高。参考图5所示的电路重构设计及焊接凸点设计,均为大面积金属致密结合,并通过倒装的方式焊接在PCB板上,封装结构简单,抗机械强度高,没有传统封装的引线键合损伤的失效风险,也没有塑封材料吸潮、热膨胀系数差异大导致的应力影响,具有优秀的可靠性表现。

如右侧表1为相同芯片两种不同封装形式的可靠性对比。

(3)成本低。HRP晶圆级封装技术是在晶圆上进行,单片晶圆颗粒数为几千甚至几万颗,UBM生长、光刻、电镀、蚀刻均是正片wafer上所有晶粒同时进行,生产效率极高,良率高达99.9%以上,单位生产成本低。同时HRP线路重构可采用钯、铜等金属制作,使用的材料较少,材料费用低。晶圆完成划片后即可贴装到PCB板上进行组装使用,不再进行后道器件级封装,省去全部的后道工艺制作。经测算,采用HRP晶圆级封装技术综合成本比传统封装技术低30%以上。

(4)产品尺寸微型化。HRP晶圆级封装技术在晶粒上进行电路重构及焊接凸点制作,相比传统封装尺寸因引线键合及塑封额外增加了大量的尺寸空间,采用HRP晶圆级封装技术完成封装后的芯片,其尺寸与裸晶粒完全相同,不会额外增加尺寸,对于追求产品尺寸微型化的应用是最优的解决方案。

3 HRP工艺进展

华芯邦科技HotChip的研发团队对HRP晶圆级先进封装技术做了深入研究及大量的探索验证,目前HRP工艺技术已成功批量应用与微机电芯片,未来,我们还将继续拓展应用于电源IC、LDO、存储器等领域。 目前,大多数芯片采用的封装方式因散热能力不足而或多或少的存在一些可靠性方面的问题。在持续的进行高功率输出时,芯片容易过热进而触发保护机制,导致性能中断,严重影响用户体验。为了解决这些问题,HotChip HRP封装技术进行了深入研究,并从底层传热学逻辑出发,全面分析了元器件在工作状态下的界面热阻。研发团队运用有限元仿真技术,构建了元器件的传热模型,以便改善散热问题。通过对传热模型的研究,HotChip改善了现有的封装方式,提高了芯片的散热性能,保证了可靠性,从而有效地提升了用户的使用体验。

4 结束语

如今,随着芯片成本日渐上涨以及封装难度的增加,HRP工艺路线将会逐渐在先进封装领域中大放光彩,主要的优势为:

1)可以直接贴合在柔性线路板上,实现柔性封装;

2)可以实现超高密度的多层布线;

3)具有更高的良率、更低的成本及更好的可靠性。因此,虽然HRP应用不久,但研发者们在工艺优化、材料选择、设备改进等方面已经进行了大量的实验验证并取得了一系列成果,未来将成为系统级集成的重要解决方案。

5 参考文献

(1)一文讲透QFN封装- 半导体行业观察

(2)晶圆级封装技术的发展-戴锦文

(3)扇出型晶圆级封装可靠性问题与思考-范懿锋1董礼2张延伟1王智彬1孟猛1

(4)先进的扇出晶圆级封装进展-Yonggang JinJeromeTeysseyreAnandanRamasamyYun LiuBing Hong Huang

(5)电子元器件封装技术发展趋势-黄庆红

审核编辑 黄宇

- 芯片

+关注

关注

450文章

49317浏览量

415581 - 封装

+关注

关注

124文章

7529浏览量

141948 - 晶圆级

+关注

关注

0文章

30浏览量

9836 - 先进封装

+关注

关注

1文章

322浏览量

158

发布评论请先登录

相关推荐

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)

评论