1 简介

eMMC(Embedded Multi Media Card)是嵌入式多媒体卡的简称,主要是针对智能手机和平板电脑特点等设计的。它的实质是在NAND Flash的基础上增加了一个控制器,并预留了一个标准接口。

2 eMMC尺寸及封装介绍

尺寸介绍

针对eMMC的封装,根据PIN脚可以分为153ball和 169ball ,但是这两种的引脚是兼容的,只是后者多了16个空脚,用于芯片的固定,没有任何信号定义。芯片封装万科的尺寸有:

- 11.5*13

- 12*16

- 14*18

- 16*20

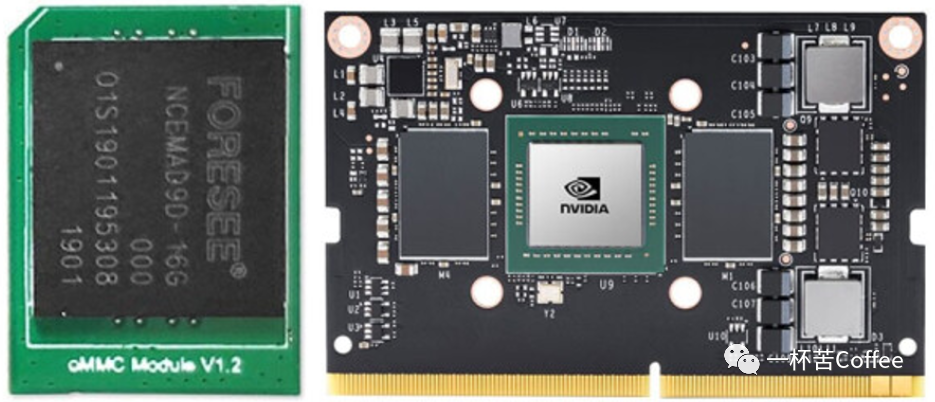

实物图片见下:

封装介绍

eMMC的封装通常有两种形态,分别153ball和 196ball, 196ball应用较少,这里主要说明153ball的相关信息:

封装见下:

尺寸信息

3 工作原理

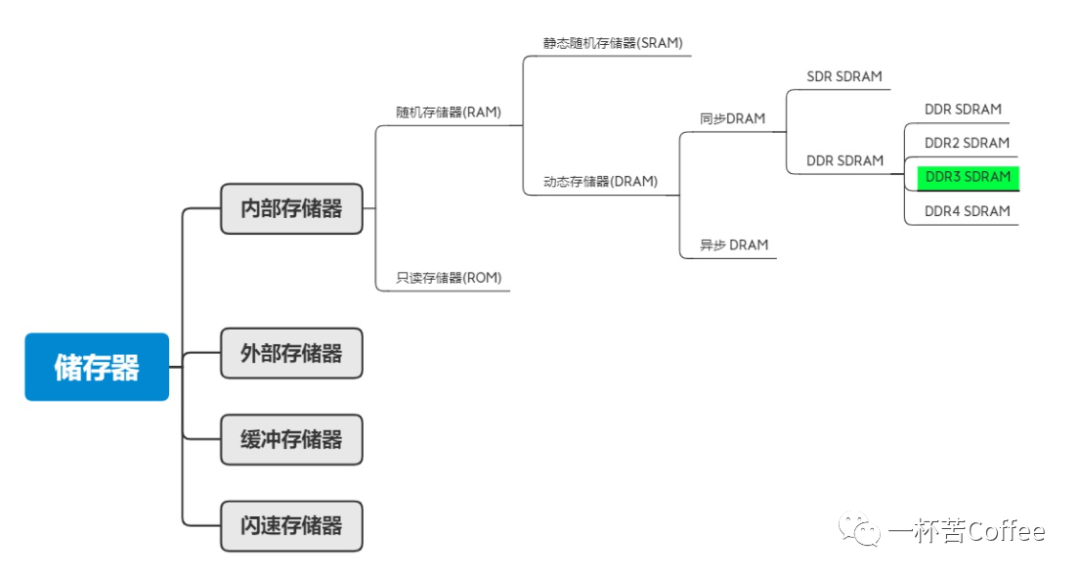

eMMC主要可以分为两个部分:Flash和 Contrller 。eMMC的实质是集成了存储控制器的Nand Flash。详见下图:

Flash

eMMC常采用非易失性存储器,掉电后数据不丢失的Nand Flash。

Contrller

各个区域的功能见下:

| 区域 | 名称 |

|---|---|

| BOOT Area Partition 1 & 2 | 此分区主要是为了支持从 eMMC 启动系统而设计的。该分区的数据,在eMMC上电后,可以通过很简单的协议就可以读取出来。同时,大部分的 SOC 都可以通过GPIO或者 FUSE 的配置,让ROM代码在上电后,将eMMC BOOT 分区的内容加载到SOC 内部的 SRAM 中执行。 |

| RPMB Partition | RPMB是Replay Protected Memory Block 的简称,它通过 HMAC SHA-256和Write Counter来保证保存在 RPMB 内部的数据不被非法篡改。在实际应用中,RPMB 分区通常用来保存安全相关的数据,例如指纹数据、安全支付相关的密钥等。 |

| General Purpose Partition 1~4 | 此区域则主要用于存储系统或者用户数据。General Purpose Partition 在芯片出厂时,通常是不存在的,需要主动进行配置后,才会存在。 |

| User Data Area | 此区域则主要用于存储系统和用户数据。User Data Area 通常会进行再分区,例如 Android 系统中,通常在此区域分出 boot、system、userdata 等分区 |

4 引脚说明

电源引脚

| 序号 | 名称 | 意义 |

|---|---|---|

| 1 | VCCQ电压 | 该电压由CPU的数据总线的VCCIO决定(eMMC总线VCCIO值必须与VCCQ保持一致) |

| 2 | VCC电压 | 该电压为核心电压; |

| 3 | VDDIM | 内部与内核供电端相连,主要功能是稳定内核电压,该PIN脚直接连接一个对地的1μF电容。 |

控制信号引脚

| 序号 | 名称 | 意义 |

|---|---|---|

| 1 | CLK | 从Host输出的时钟信号,用于数据的同步。 |

| 2 | CMD | 主要用于Host向eMMC发送指令以及eMMC向Host发送请求。 |

| 3 | DS时钟 | DS时钟由eMMC发送给Host,用于Host与eMMC进行数据接收同步。只有在HS400模式下,才需要使用DS引脚。 |

注意 :HS200模式下,需要使用CLK、CMD、D[3...0];HS400模式下,需要使用CLK、CMD、D[7...0]、DS。

数据信号引脚

D[7...0]:Dx信号主要用于 Host 和 eMMC 之间的数据传输。在 eMMC 上电或者软复位后,只有 DAT0 可以进行数据传输,完成初始化后,可配置 4bit 或者8bit进行数据传输。

5 eMMC电路设计实战

电源部分

eMMC供电采用3.3V和1.8V电源,注意电容应该靠近IC引脚放置。注意去耦电容大小,详见附件。

数据通信部分

该部分需要需要添加上拉电阻,不同厂家的芯片应该注意上拉电阻的阻值,详见附件。

NC部分

该部分的引脚无实际功能,在进行PCB走线时可压PIN走线。

附件

上拉电阻和去耦电容的大小,一般由详细说明,具体见下:

6 PCB布局建议

信号CLK、CMD、DQ和DS均做阻抗50Ω±10%匹配管控。

信号CLK、CMD、DQ和DS约束为同组信号,长度差控制在±50mil范围内。

所有信号线走线长度约束在2000mil以内,且注意使用IBIS模型进行仿真评估阻抗匹配和反射情况。

信号线有完整的参考层。

内部走不出来的信号可以从NC PAD走,不能从RFU PAD上走线。

CLK和RST_N长度差在1000mil以内。

-

控制器

+关注

关注

112文章

16332浏览量

177798 -

嵌入式

+关注

关注

5082文章

19104浏览量

304771 -

电路设计

+关注

关注

6673文章

2451浏览量

204125 -

封装

+关注

关注

126文章

7873浏览量

142890 -

emmc

+关注

关注

7文章

203浏览量

52720

发布评论请先 登录

相关推荐

怎么成为硬件电路设计高手?

硬件电路设计的思路分享

硬件电路设计之“磁珠”的应用资料下载

硬件电路设计之eMMC电路设计

硬件电路设计之eMMC电路设计

评论