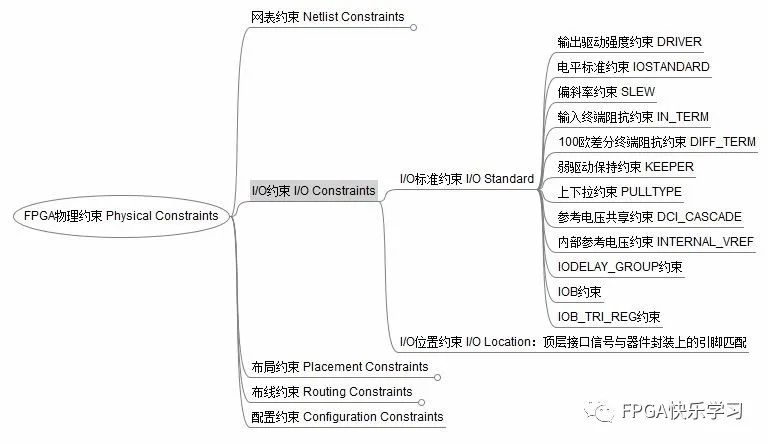

I/O约束(I/O Constraints)包括I/O标准(I/OStandard)约束和I/O位置(I/O location)约束。

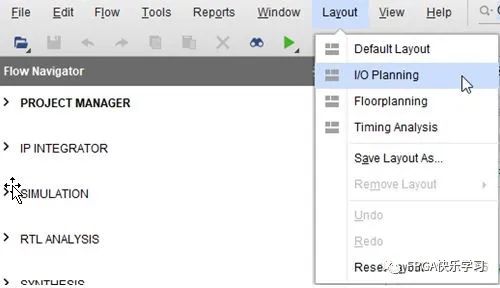

以Xilinx Vivado开发工具为例,点击OpenImplemented Design,打开实现设计(Implemented Design)页面。接着如图1所示,在菜单上点击Layout-> I/O Planning,打开I/O约束页面。

图1I/OPlanning菜单

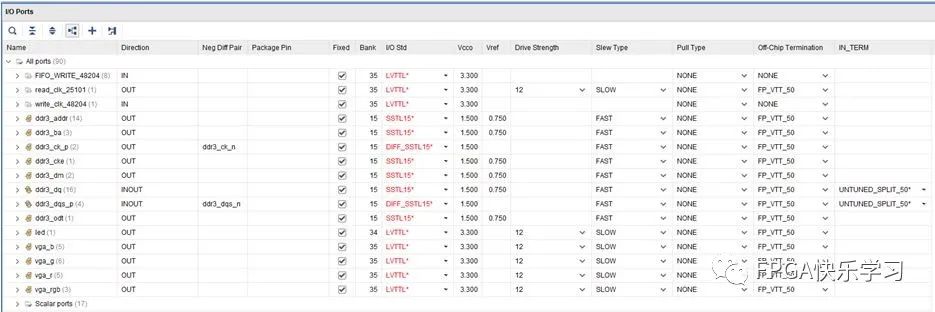

I/O约束页面如图2所示,在该页面中,Allports一列中按照总线的方式进行分类,可以进一步展开看到每一个具体的I/O引脚的约束信息。这里的I/O标准约束包括了电平标准(I/O Std)、输出驱动强度(Drive Strength)、上下拉类型(Pull Type)、偏斜率类型(Slow Type)、输入终端阻抗(IN_TERM)等。由于I/O标准和FPGA外部所连接的外设芯片息息相关,每个外设芯片所对应的I/O标准不同,在FPGA中的约束设置也有所不同。

图2I/O约束页面

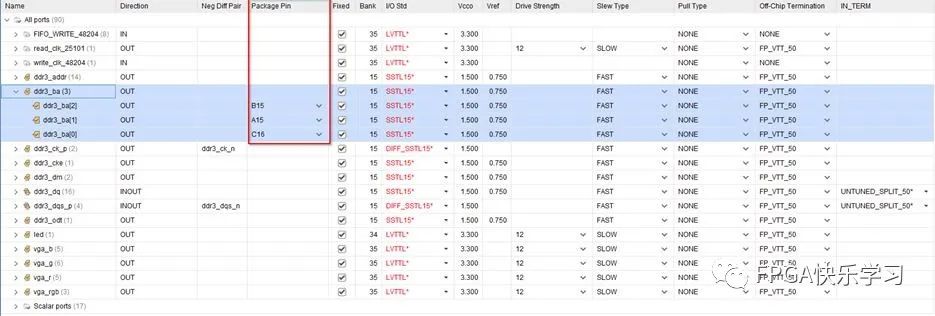

如图3所示,展开一组名为ddr3_ba的总线,其下的3个I/O引脚详细的约束信息都一目了然。Package Pin一列即I/O的位置约束信息,通常对应着一些字母和数字组合的位置代号,如图示的B15、A15、C16,即FPGA器件封装上对应着的具体的物理引脚的代号。通过这样的位置约束,就将FPGA顶层模块代码中的I/O信号和器件封装上的引脚映射在一起了。

图3I/O位置约束

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21729浏览量

602953 -

Xilinx

+关注

关注

71文章

2167浏览量

121289 -

引脚

+关注

关注

16文章

1193浏览量

50405 -

约束

+关注

关注

0文章

82浏览量

12728 -

Vivado

+关注

关注

19文章

812浏览量

66470

原文标题:物理约束实践:I/O约束

文章出处:【微信号:FPGA快乐学习,微信公众号:FPGA快乐学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

物理约束之IO约束

物理约束之布局约束

如何约束内部生成的i2s o时钟?

Adam Taylor玩转MicroZed系列74:物理约束

FPGA设计约束技巧之XDC约束之I/O篇(下)

物理约束实践:I/O约束

物理约束实践:I/O约束

评论