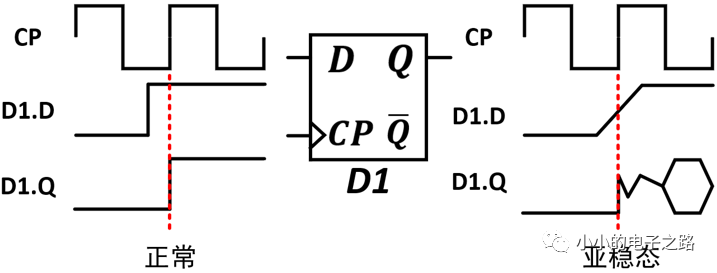

亚稳态是指触发器的输入信号无法在规定时间内达到一个确定的状态,导致输出振荡,最终会在某个不确定的时间产生不确定的输出,可能是0,也可能是1,导致输出结果不可靠。

1、亚稳态产生原因

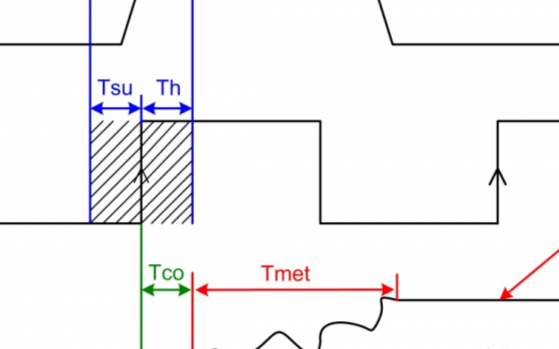

亚稳态的产生是 输入信号违背了触发器的建立时间和保持时间导致的 。建立时间是指在时钟边沿到来之前输入信号必须保持稳定的时间。保持时间是指在时钟边沿到来之后数据必须保持稳定的时间。输入信号如果在这两个时间段内没有保持稳定,就将产生亚稳态现象。

2、同步机制

亚稳态无法避免,只能通过一定方法阻止其向后级传播,避免其对后级电路产生影响。主要方法有: 引入同步机制 、 采用响应更快的触发器 、降低时钟频率等。接下来介绍一下如何通过同步机制阻断亚稳态的传播。

如下图所示,如果触发器出现亚稳态现象,该电路将无法准确检测输入信号是否出现上升沿。

(1)若D1.Q稳定在低电平,能够检测出上升沿;

(2)若D1.Q稳定在高电平,不能检测出上升沿;

但是,如果采用两个触发器级联的方式引入同步机制,情况就不一样了,电路将准确检测输入信号是否出现上升沿。

(3)若D1.Q稳定在低电平,在输入信号上升沿出现两个时钟周期后,检测出上升沿;

(4)若D1.Q稳定在高电平,在输入信号上升沿出现一个时钟周期后,检测出上升沿。

总而言之,该电路始终能够检测出上升沿,只是时间问题。

-

时钟频率

+关注

关注

0文章

49浏览量

20333 -

数字电路

+关注

关注

193文章

1605浏览量

80577 -

触发器

+关注

关注

14文章

2000浏览量

61129 -

亚稳态

+关注

关注

0文章

46浏览量

13267 -

输入信号

+关注

关注

0文章

455浏览量

12547

发布评论请先 登录

相关推荐

FPGA中亚稳态——让你无处可逃

FPGA中亚稳态——让你无处可逃

在FPGA中,同步信号、异步信号和亚稳态的理解

今日说“法”:让FPGA设计中的亚稳态“无处可逃”

一种消除异步电路亚稳态的逻辑控制方法

数字电路中的亚稳态产生原因

数字电路中的亚稳态产生原因

评论