本文转载自: TechInsights微信公众号

2021年10月12日,三星宣布“三星新的五层EUV工艺实现了业界最高的DRAM位密度,将生产率提高了约20%”[1]。TechInsights在2023年2月17日发布的三星Galaxy S23 plus智能手机中获得了三星D1a LPDDR5X DRAM器件[2]。经过深入的SEM和TEM成像,并结合TEM EDS/EELS元素分析,TechInsights即将发布三星D1a nm 16 Gb LPDDR5X器件的分析报告。基于结构和材料逆向工程分析数据,TechInsights发现了四种EUV光刻(EUVL)工艺,用于阵列有源切割/外围有源(有源修剪)、位线接触(BLC)、存储节点接触垫(SNLP)/外围第一金属层 (M1)和存储节点(SN)管图形化。通过逆向工程分析没有明显的证据来确定EUVL工艺的第五层图形化层。

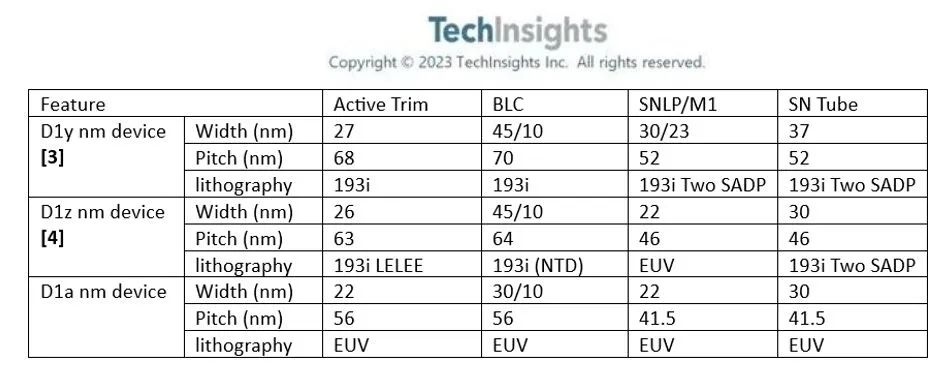

下表列出了三星D1y nm、D1z nm和D1a nm工艺器件的阵列有源切割、BLC、SNLP、SN管的最小宽度和节距,以及用于每层制模的光刻工艺。

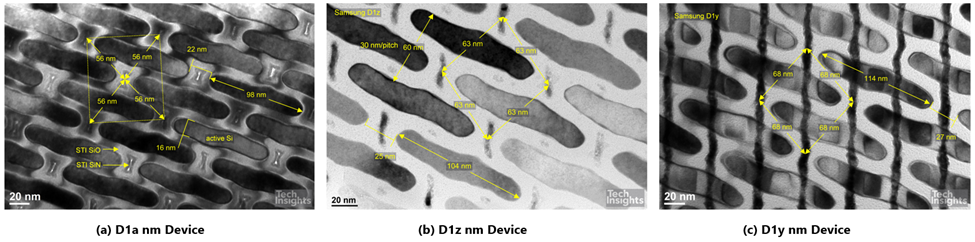

下图包含了三星D1a nm(图a)、D1z nm(图b)和D1y nm(图c)器件在存储阵列有源层的TEM平面视图。存储器阵列中的有源切口具有交错孔布局。三星D1y nm器件的阵列有源切割间距为68 nm,达到了193i光刻的分辨率极限。单193i光刻工艺用于图形化阵列有源切割/外围有源。三星D1z nm器件的阵列有源切割间距为63 nm。双图形化工艺可能用于图形阵列有源切割/外围有源。三星D1a nm器件的阵列有源切割间距为56 nm。

图1:在DRAM阵列有源层上的TEM平面视图

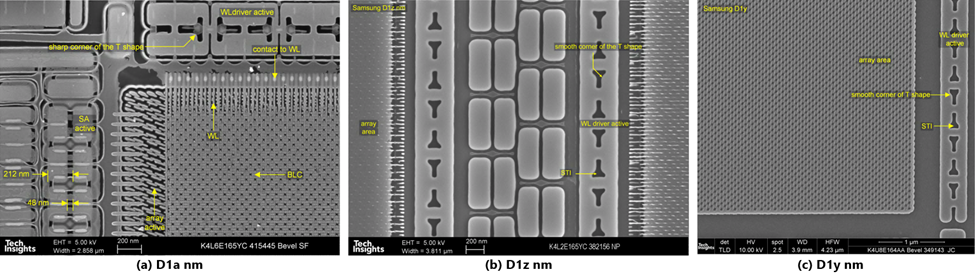

图2是三星D1a nm (a)、D1z nm (b)和D1z nm (c)器件在外围有源层的SEM平面视图图像。WL有源驱动中间的T型STI有一个尖角,如图2(a)所示;而WL有源驱动中间的T型STI有一个相对光滑的角,如图2(b)和图2(c)所示。这清楚地表明,存储阵列中的有源切口和外围的有源切口采用的是单一EUVL工艺,而不是193i双重图形化工艺。

图2:外围有源层SEM平面图

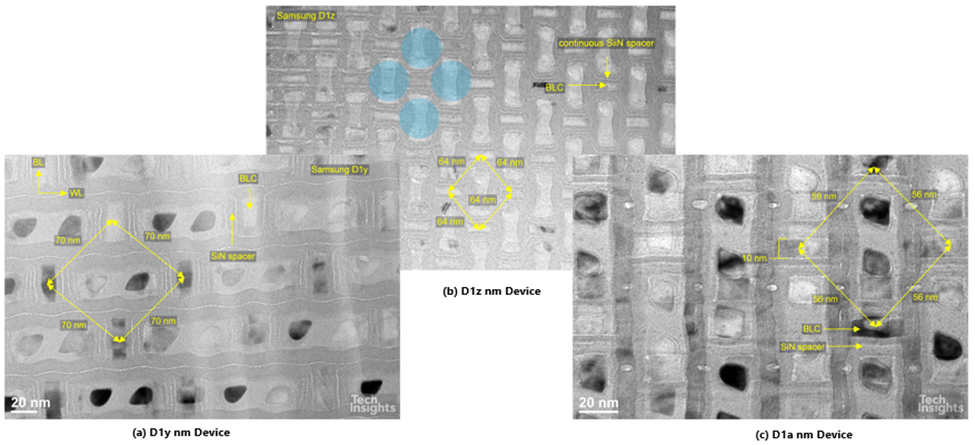

图3为三星D1y nm (a)、D1z nm (b)和D1a nm (c)在DRAM位线接触(BLC)层的TEM平面视图图像。BLC具有如下图所示的交错孔布局。三星D1y nm器件的BLC间距为70 nm(图a),这是193i光刻的分辨率极限。因此,采用单一的193i光刻工艺对BLC进行图形化。如图3 (b)所示,三星D1z nm器件的BLC间距为64 nm;由于在BLC特殊区域(如蓝点所示)使用掩膜的负色调显影(NTD)光刻工艺来对BLC进行图形化设计,因此可以观察到连续的SiN间隔(参见有关三星12 Gb 1z EUV LPDDR5 Advanced Memory Essentials, AME2102 -801的更多详细信息)。如图3(c)所示,三星D1a nm器件的BLC间距为56 nm;如图3 (a)所示,BLC SiN间隔片不是连续的,这与三星D1y nm器件中的BLC SiN间隔片相同。单个EUVL工艺可能用于三星D1a nm器件中的BLC图形化。

图3:阵列BLC层TEM平面视图

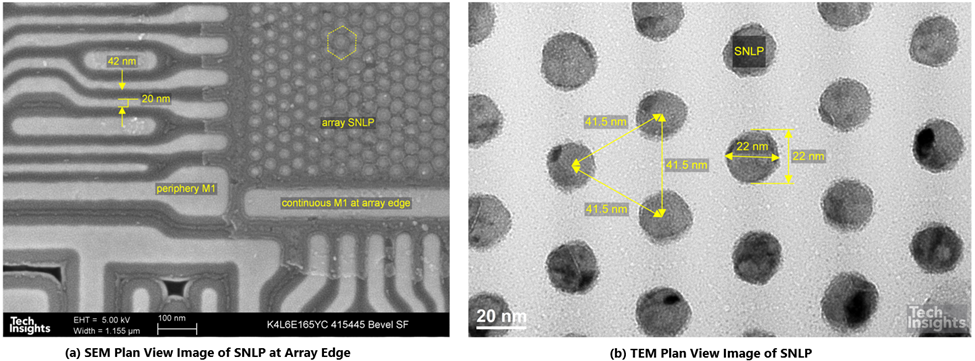

图4包括了三星D1a nm器件SNLP层的SEM (a)和TEM (b)平面视图图像。与三星D1z nm制程器件相同,圆形SNLP和阵列边缘的连续M1线表明使用单个EUVL制程对存储节点接触垫(SNLP)和外围M1进行了图形化。

图4:三星D1a nm器件阵列SNPL层的SEM和TEM平面视图

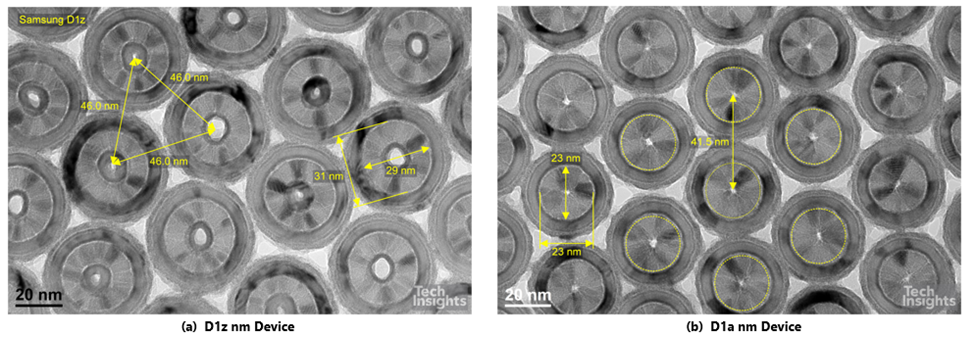

图5为三星D1z nm (a)和D1a nm (b)器件电容层的TEM平面视图图像。D1z nm器件的电容存储节点(SN)管间距为46.0 nm, D1a nm器件的SN管间距为41.5 nm。在三星D1z器件中,采用双向自对准双图像化工艺对SN管进行图像化(详见三星12Gb 1z EUV LPDDR5 process Flow Full, PFF-2102-801)。如图5 (a)所示,由于双向自对准图像化工艺的偏移和工艺均匀性问题,部分SN管在一个方向上比另一个方向略微拉长。D1a nm器件中的SN管在TEM斜角水平呈圆形,直径为23 nm(图5 (b))。因此,单一EUVL工艺可能用于三星D1a nm器件的SN管图案。

图5:在阵列电容层的TEM平面视图

References:

[1] Samsung Starts Mass Production of Most Advanced 14nm EUV DDR5 DRAM

[2] Samsung Announces Global Launch of the Galaxy S23 Series

审核编辑 黄宇

-

DRAM

+关注

关注

40文章

2311浏览量

183438 -

光刻

+关注

关注

8文章

320浏览量

30155 -

EUV

+关注

关注

8文章

605浏览量

86004 -

LPDDR5

+关注

关注

2文章

89浏览量

12061 -

三星

+关注

关注

1文章

1521浏览量

31203

发布评论请先 登录

相关推荐

佰维存储发布LPDDR5X高效能内存

佰维存储发布新一代LPDDR5X内存

今日看点丨 2011亿元!比亚迪单季营收首次超过特斯拉;三星将于2025年初引进High NA EUV光刻机

简述光刻工艺的三个主要步骤

光刻工艺的基本知识

三星量产最薄LPDDR5X内存,技术再突破

三星电子实现低功耗LPDDR5X DRAM的量产

三星开始量产其最薄LPDDR5X内存产品,助力端侧AI应用

三星10.7Gbps LPDDR5X成功在联发科天玑平台上完成兼容性验证

三星10.7Gbps LPDDR5X在联发科技下一代天玑移动平台上完成验证

三星拟应用金属氧化物抗蚀剂(MOR)于DRAM EUV光刻工艺

10.7Gbps,LPDDR5X还能继续卷性能

三星D1a nm LPDDR5X器件的EUV光刻工艺

三星D1a nm LPDDR5X器件的EUV光刻工艺

评论