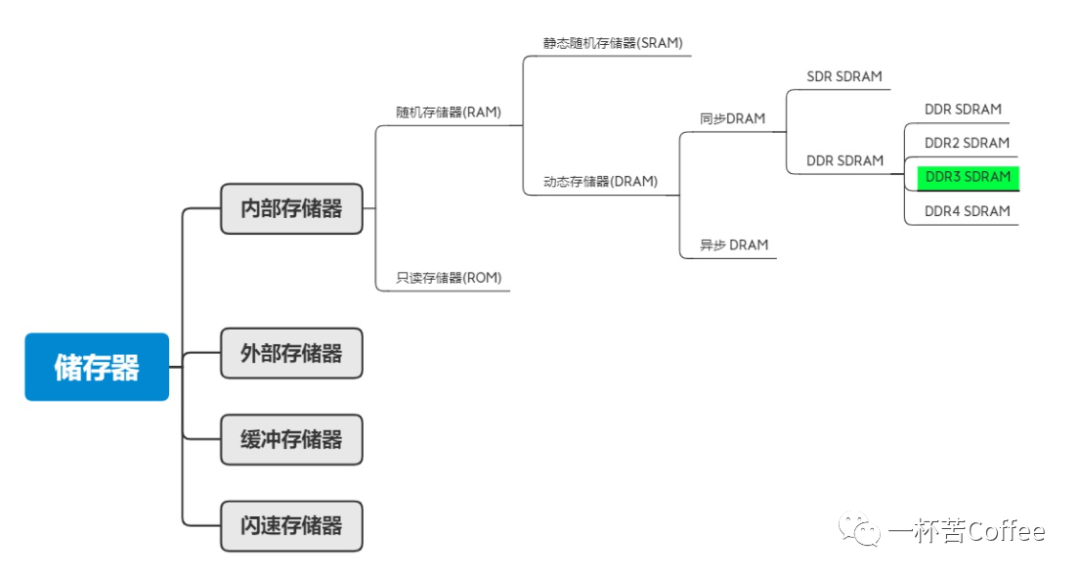

1 简介

- RAM存储器: 存储器掉电数据丢失,重新上电后数据无法回复。

- ROM存储器: 存储掉电数据不丢失,重新上电后能依然存在。

电路设计中常见的DDR属于SDRAM,中文名称是同步动态随机存储器。其中同步和动态的意义分别如下:

- 动态存储器(Dynamic RAM,DRAM) :存储器需每隔一段时间,要刷新冲一次电,否则会丢失内部的数据。

- 静态存储器(Static RAM,SRAM) :不需要刷新电路,内部数据不会丢失。

- 同步(Synchronous) :工作需要同步时钟,它是内部数据和指令的发送与接收的基准。

- 随机存储器 :数据不是线性存储,而是通过指定地址来进行数据的读写。

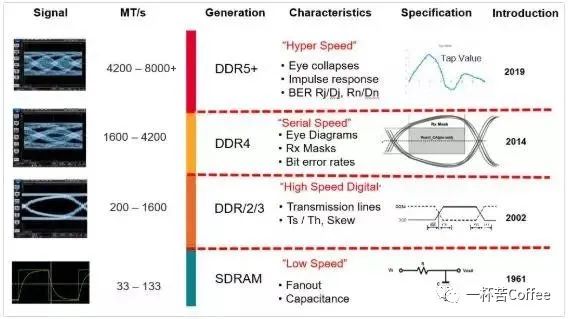

2 DDR的发展历程

- 版本迭代

DDR的发展经历了SDRAM、DDR2、DDR3、DDR4、DDR5五个阶段,随着时间的推移,存储的速率越来越高,核电越来越低。

- 最高传输速率

目前DDR5所能到达的最高的速率为6400T/s。

| 序号 | 版本 | 核电压 | 最高速率 |

|---|---|---|---|

| 1 | SDRAM | 2.5V/3.3V | |

| 2 | DDR2 | 1.8V | |

| 3 | DDR3 | 1.5V | 1600MT/s |

| 4 | DDR4 | 1.2V | 3200MT/s |

| 5 | DDR5 | 1.1V | 6400MT/s |

这里顺带说一下T/S和bps的换算关系:

- T/S的含义

T/s表示每秒****传输次数(Transfer per second) ,有效带宽要结合传输协议来计算。

- bps的含义

bps表示每秒传输二级制位数(bit per second)。

案例 :PCI-e2.0 协议支持 5.0 GT/s, 即每一条Lane 上支持每秒钟内传输 5G次,因为PCIe 2.0 的物理层协议中使用的是 8b/10b的编码机制,即每传输8个bit,需要发送10个bit;这多出的2个bit并不是对上层有意义的信息。PCIe 2.0协议的每一条Lane支持 5 * 8/10=4Gbps的速率。 以一个PCIe 2.0 x8的通道为例,x8的可用带宽为 4 * 8=32Gbps。(后面PCIe文章还会更加详细讲解)

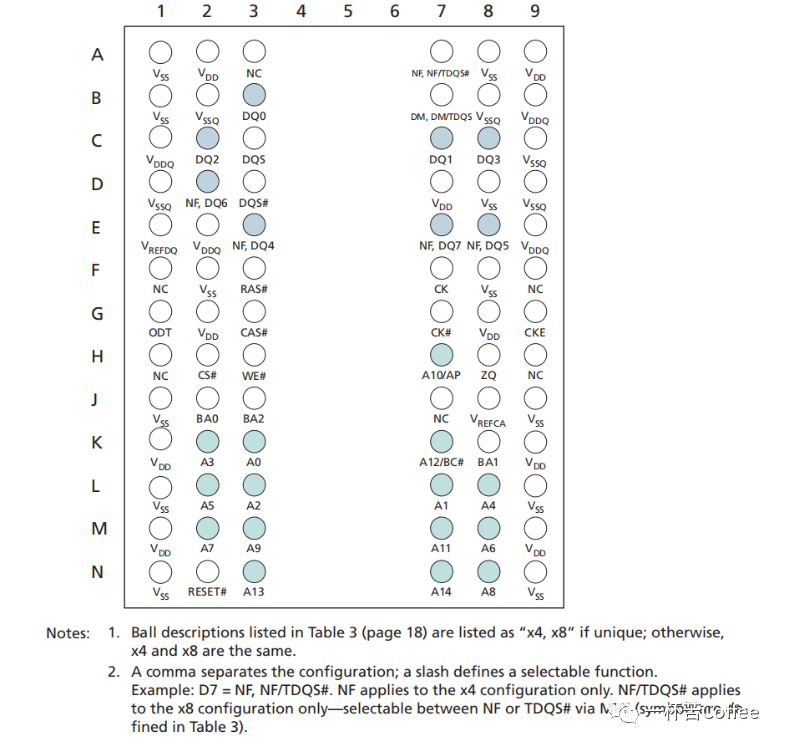

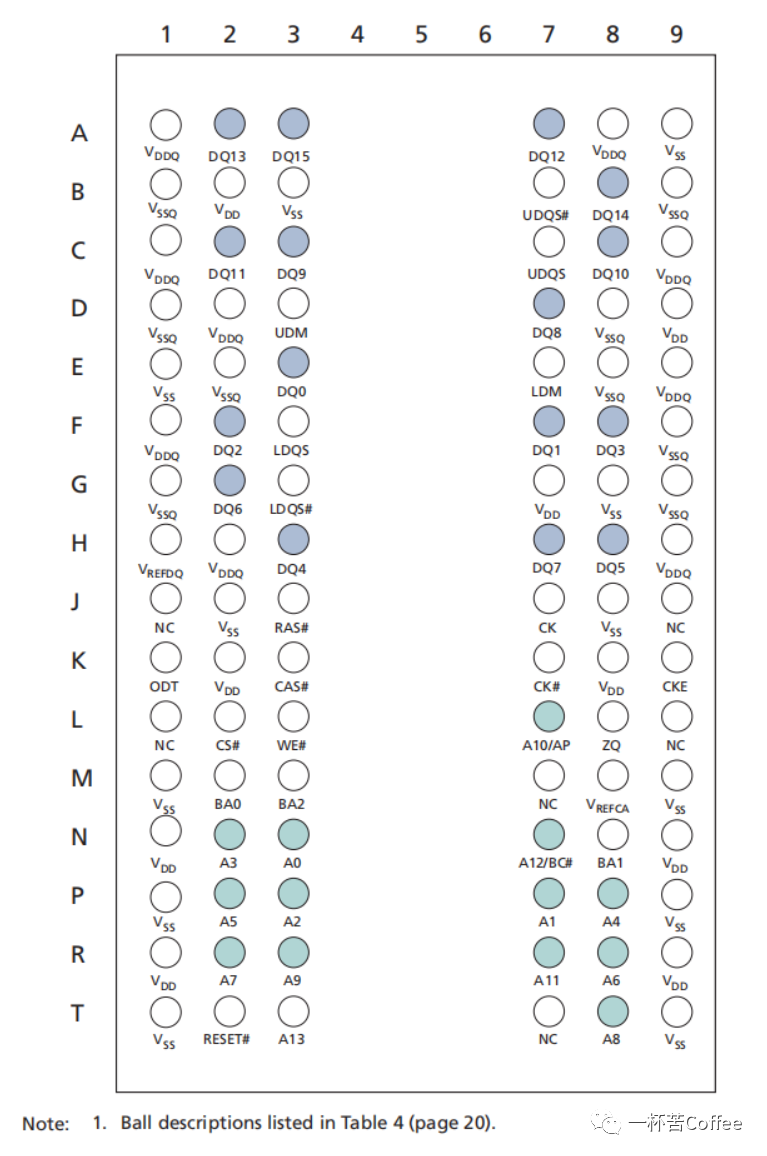

3 DDR的封装

DDR3和DDR4的封装主要有两种:78-Ball FBGA – x4, x8 和96-Ball FBGA – x16。

- 78-Ball FBGA – x4, x8 (Top View)

这种封装类型有78个PIN脚,仅支持4数据位宽和8数据带宽。

- 96-Ball FBGA – x16 (Top View)

这种封装类型有96个PIN脚,仅支持最高支持16数据带宽。

4 DDR的容量计算

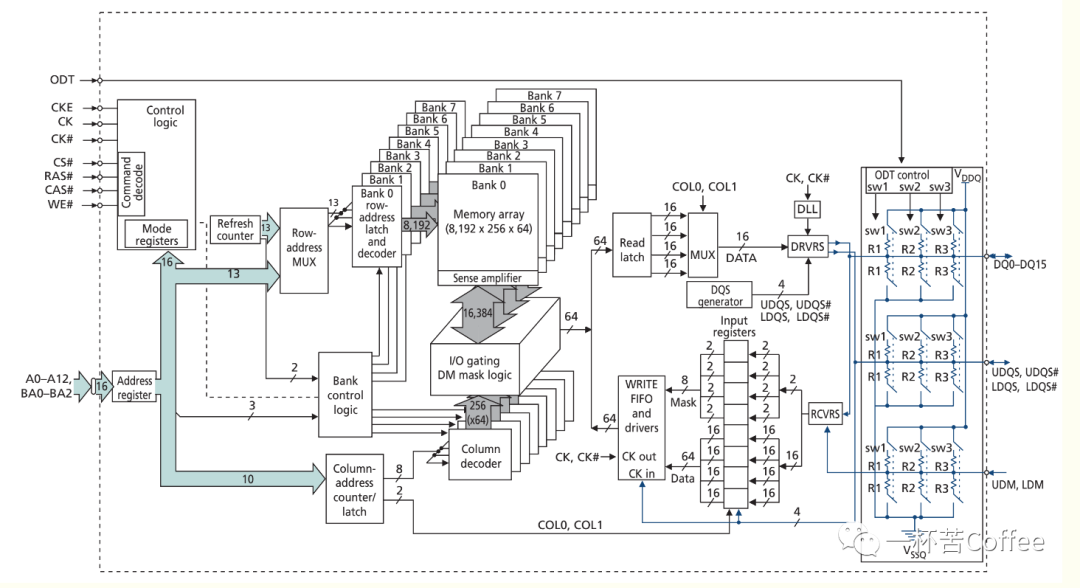

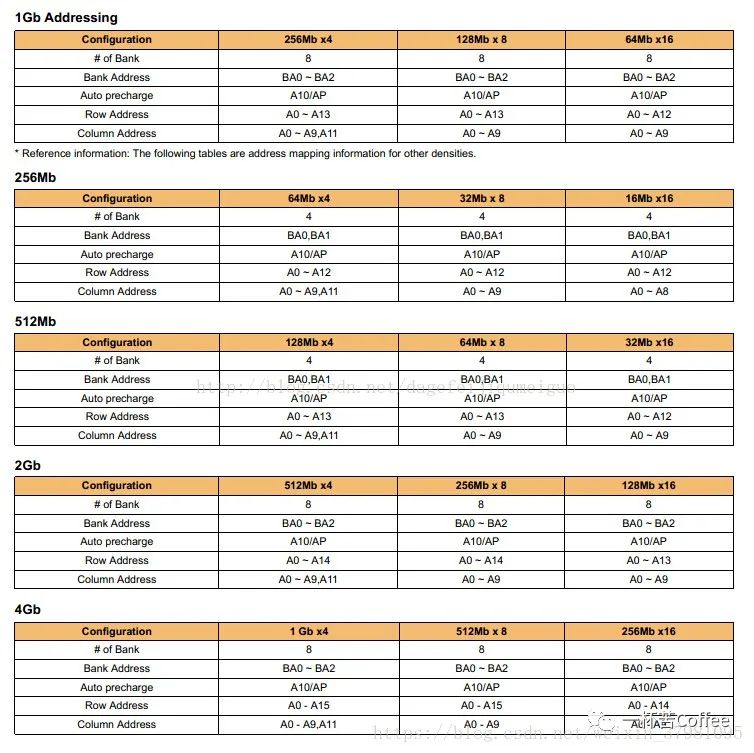

由图可以归纳出:

- bank有8个,对应BA[2:0];

- 行地址有15bit,列地址有10bit(其中低3bit不会用于列寻址);

- 内存颗粒的容量 = 2^15 * 2^10 * 8*16bit=4096Mbit;

- 根据DDR数据信号线位宽,描述上图产品的规格,即256 * 16bit。

说明:15为行地址数目;7为列地址数目;8为Bank数目;16为数据位宽。

以下是案例:

5 DDR的基本原理

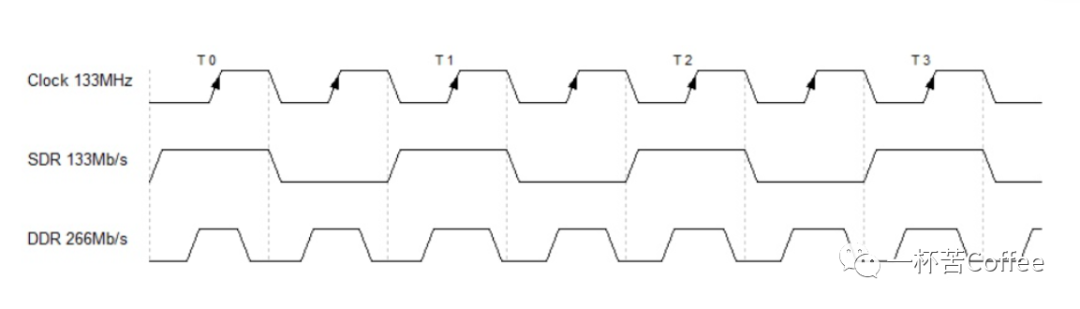

DDR里面主要使用了Double Data Rate 和 Prefetch两项技术。实际上,无论是SDR还是DDR3,内存芯片内部的核心时钟基本上是保持一致的,都是 100MHz 到 200MHz(某些厂商生产的超频内存除外)。DDR即 Double Data Rate 技术使数据传输速度较 SDR 提升了一倍。如下图所示,SDR 仅在时钟的上升沿传输数据,而 DDR 在时钟信号上、下沿同时传输数据。例如同为133MHz 时钟,DDR却可以达到266Mb/s的传输速度。

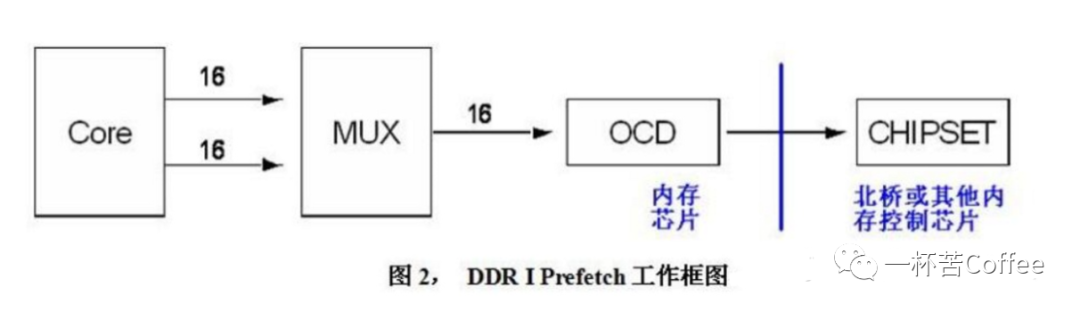

芯片内部数据数据传输速度的提升则是通过Prefetch 技术实现的。 所谓 Prefetch 简单的说就是在一个内核时钟周期同时寻址多个存储单元并将这些数据以并行的方式统一传输到IO Buffer中,之后以更高的外传速度将IO Buffer 中的数据传输出去 。这个更高的速度在DDR上就是通过Double Data Rate 实现的,也正因为如此,DDR外部 Clock 管脚的频率与芯片内部的核心频率是保持一致的。如下图所示为 DDR的Prefetch 过程中,在16位的内存芯片中一次将2 个16bit数据从内核传输到外部MUX单元,之后分别在Clock信号的上、下沿分两次将这 2 x 16bit 数据传输给北桥或其他内存控制器,整个过程经历的时间恰好为一个内核时钟周期。

发展到 DDR2,芯片内核每次Prefetch 4倍的数据至IO Buffer中,为了进一步提高外传速度,芯片的内核时钟与外部接口时钟(即我们平时接触到的Clock 管脚时钟)不再是同一时钟,外 Clock时钟频率变为内核时钟的2倍。同理, DDR3 每次Prefetch 8倍的数据,其芯片Clock频率为内核频率的4倍, 即 JEDEC标准(JESD79-3)规定的400MHz至800MHz,再加上在 Clock 信号上、下跳变沿同时传输数据,DDR3的数据传输速率便达到了800MT/s到1600MT/s。具体到内存条速度,我们以PC3-12800为例,其采用的DDR3-1600芯片核心频率为 200MHz,经过Prefetch后Clock信号频率到达 800MHz,再经过Double Data Rate 后芯片数据传输速率为1600 MT/s,内存条每次传输64 bits或者说8 bytes数据,1600*8 便得到12800MB/s的峰值比特率。

6 引脚描述

今天主要简单介绍一些关键信号,后续会详细说明这些信号在设计中应该注意的事项 。

| 信号名 | 方向 | 功能描述 |

|---|---|---|

| CK_t,CK_c | Input | 差分时钟输入。所有的地址、控制信号都是通过CK_t的上升沿与CK_c的下降沿进行采样的 |

| CKE | Input | 时钟使能:CKE为高电平时,启动内部时钟信号、设备输入缓冲以及输出驱动单元。CKE低电平时则关闭上述单元。当CKE为低电平时,可使设备进入PRECHARGE POWER DOWN、SELF-REFRESH以及ACTIVE POWER DOWN模式。CKE与SELF REFRESH退出命令是同步的。在上电以及初始化序列过程中,VREFCA与VREF将变得稳定,并且在后续所有的操作过程中都要保持稳定,包括SELF REFRESH过程中。CKE必须在读写操作中保持稳定的高电平。在POWER DOWN过程中,除CK_t,CK_c,ODT以及CKE以外的所有输入缓冲都是关闭的。在SELF REFRESH过程中,除CKE以外的所有输入缓冲都是关闭的。在正时钟上升边沿采样。 |

| CS_n | Input | 片选信号:当CS_n锁存为高电平时,所有的命令都被忽略。在正时钟上升边沿采样。 |

| CA_n | Input | 命令/地址输入信号。可作为地址线使用,也可作为命令代码使用,是命令代码的一部分。 |

| ODT | Input | On-Die Termination,片上终端电阻:ODT信号可使能DDR SDRAM内部的RTT_NOM终端电阻。该设计通过允许DRAM控制器独立地打开/关闭任一或所有DRAM设备的终端电阻来改善存储器通道的信号完整性。DRAM通过ODT控制引脚为每个DQ,DQS_t及DQS_c和DM开启/关闭终端电阻。与其他输入命令不同,ODT引脚直接控制ODT动作,不对其进行时钟采样。在自刷新模式下不支持ODT。可以选择在CKE掉电期间通过模式寄存器启用ODT操作。请注意,如果在掉电模式下启用ODT,则在掉电期间可能无法关闭VDDQ(I/O供电),同时DRAM也会在读操作期间无法关闭。 |

| DM_n | Input | 输入数据掩码:DM_n信号是作为写数据的掩码信号,当DM_n信号为低电平时,写命令的输入数据对应的位将被丢弃。DM_n在DQS的两个条边沿都采样。 |

| DQ | InputOutput | 数据输入、输出:双向数据总线。若模式寄存器中使能了CRC功能,那么在数据burst结束时就会附加一段CRC码。 |

| DQS_t,DQS_c | InputOutput | 差分数据选通信号:差分信号对,作输入时与写数据同时有效,作输出时与读数据同时有效。读数据时与边沿对齐,但是跳变沿位于写数据的中心。DDR4 SDRAM仅支持选通信号为差分信号,不支持单根信号的数据选通信号。 |

| NC | N.A | 无电气连接。 |

| VDDQ | Supply | I/O供电:1.2V +/- 0.06V |

| VSSQ | Supply | GND |

| VDD | Supply | Core供电:1.2V +/- 0.06V |

| VDDCA | Supply | CA供电 |

| VSSCA | Supply | GND |

| VSS | Supply | GND |

| VPP | Supply | DRAM激活供电:2.5V(最小2.375V,最大2.75V) |

| VREF | Supply | 参考电压 |

| ZQ | Supply | Drive Strength Caliation校准参考电阻 |

7 硬件电路实战

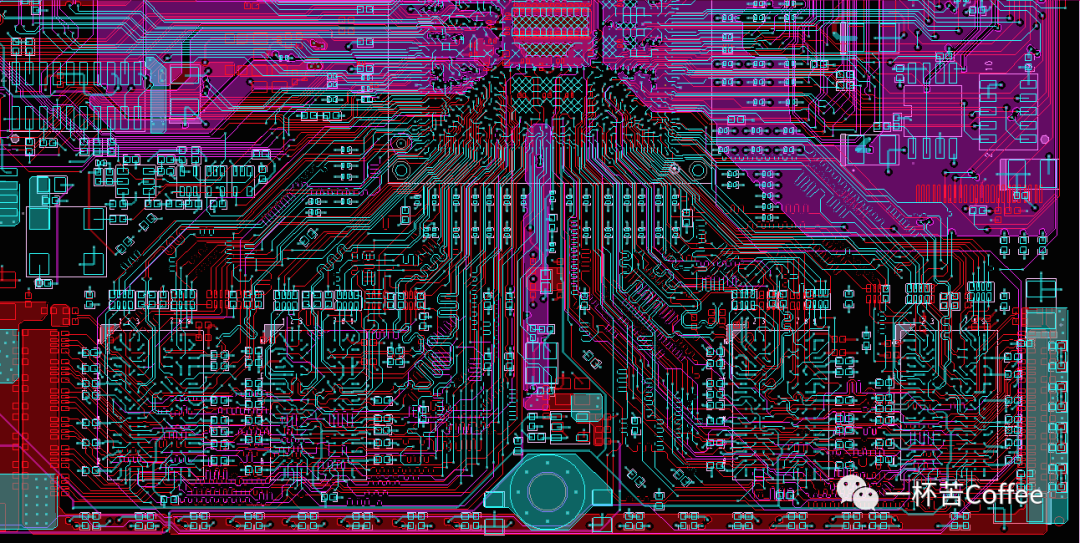

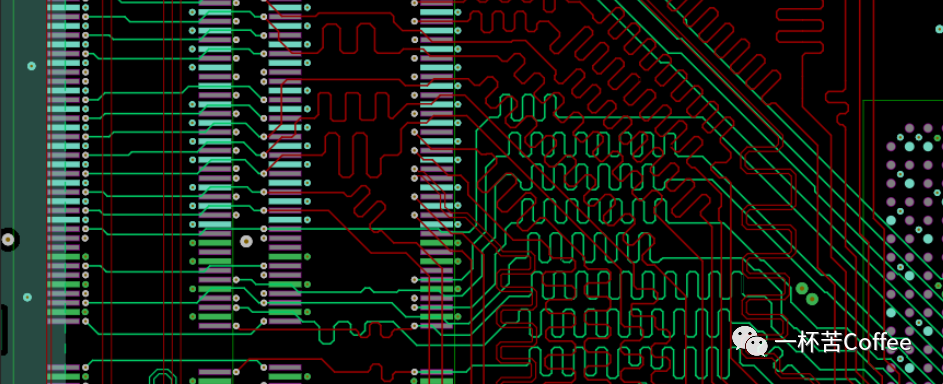

今天主要是放一些参考电路,下一篇文章会详细讲解DDR设计的整个过程,包括DDR的级联以及Layout中应该注意的事项。

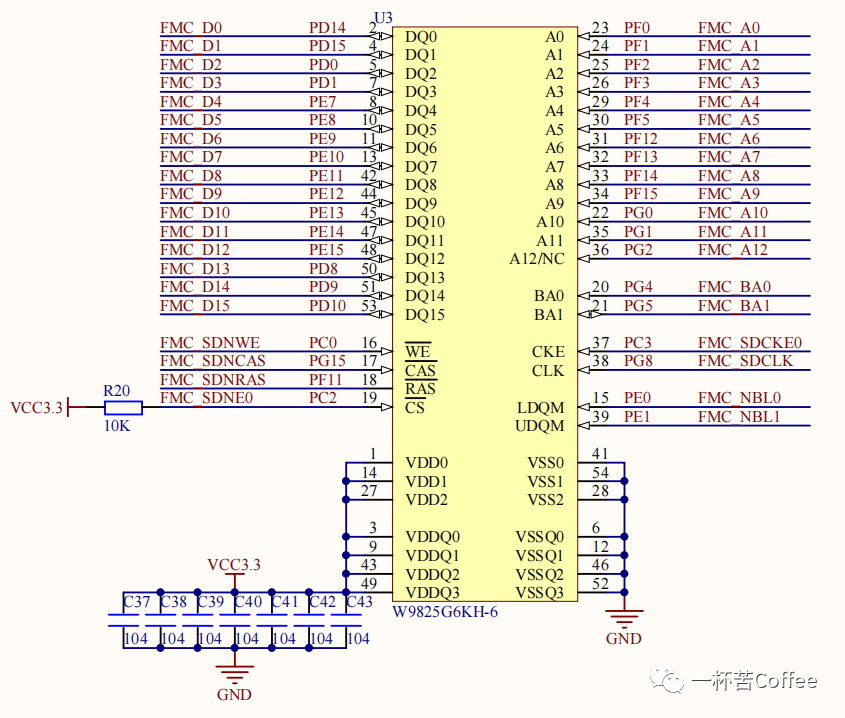

- SDRAM电路设计案例

SDRAM广泛应用于LCD屏幕中,通常搭配NAND Flash或者NOR Flash使用。

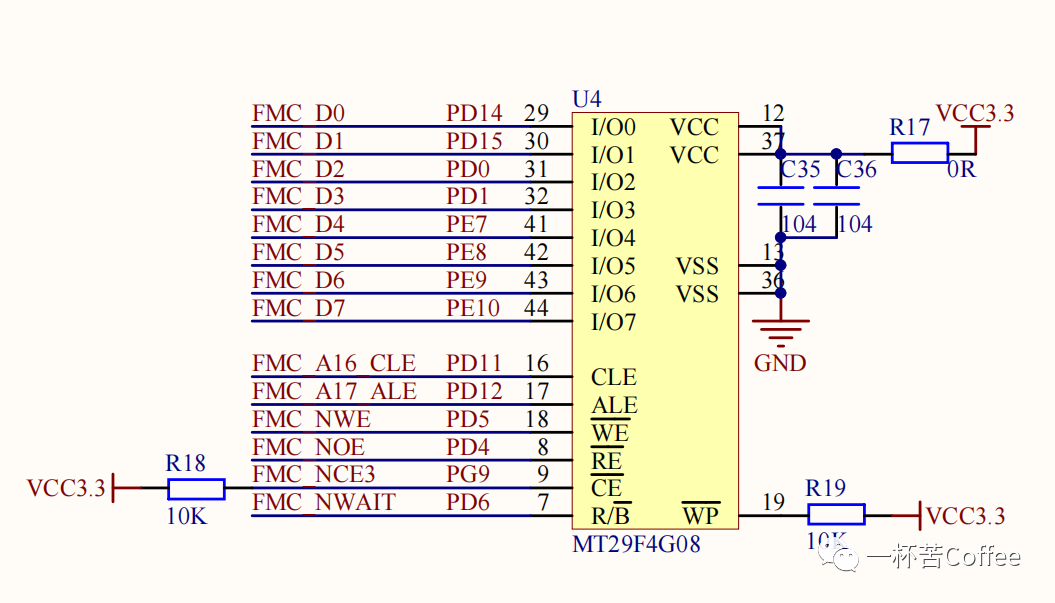

NAND Flash的存储电路见下图:

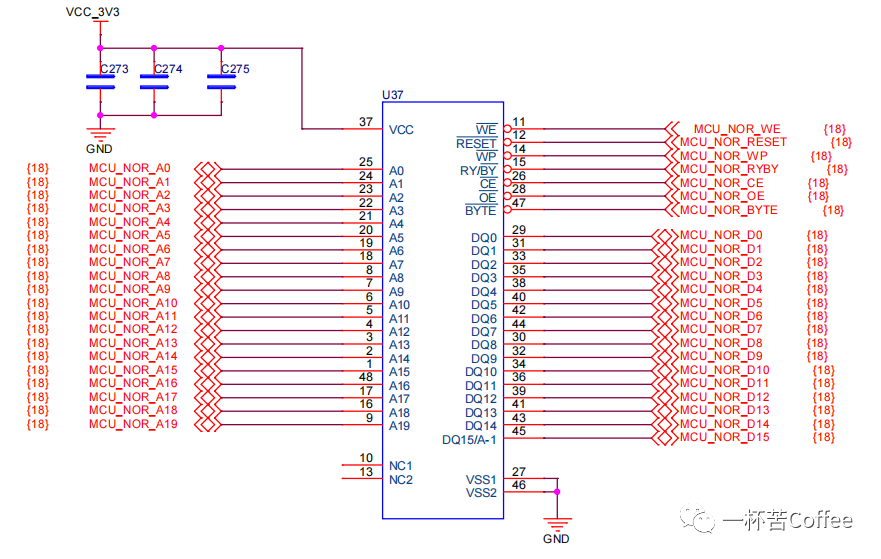

NOR Flash的电路设计见下:

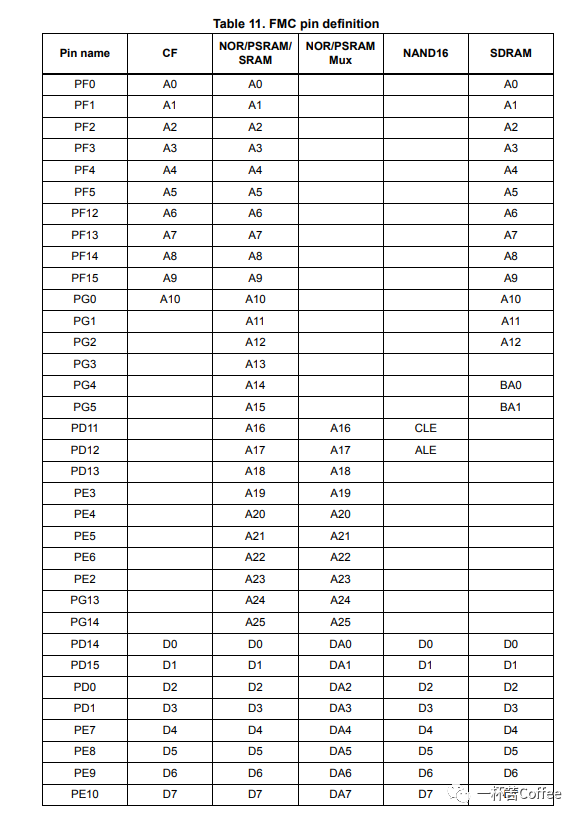

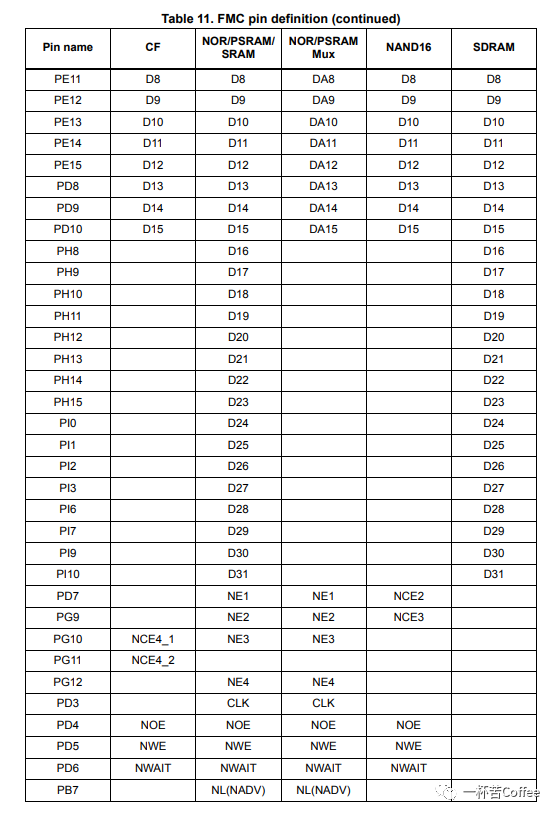

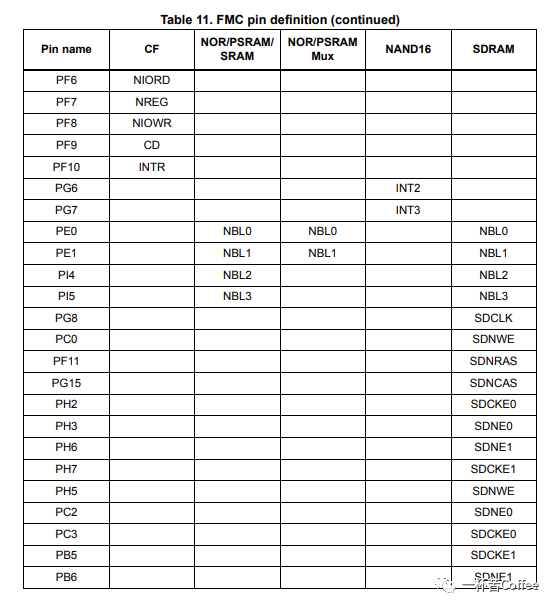

NOR Flash和SRAM的数据线和地址线通常是复用的,具体需要见手册,以下截取STM32手册部分内容:

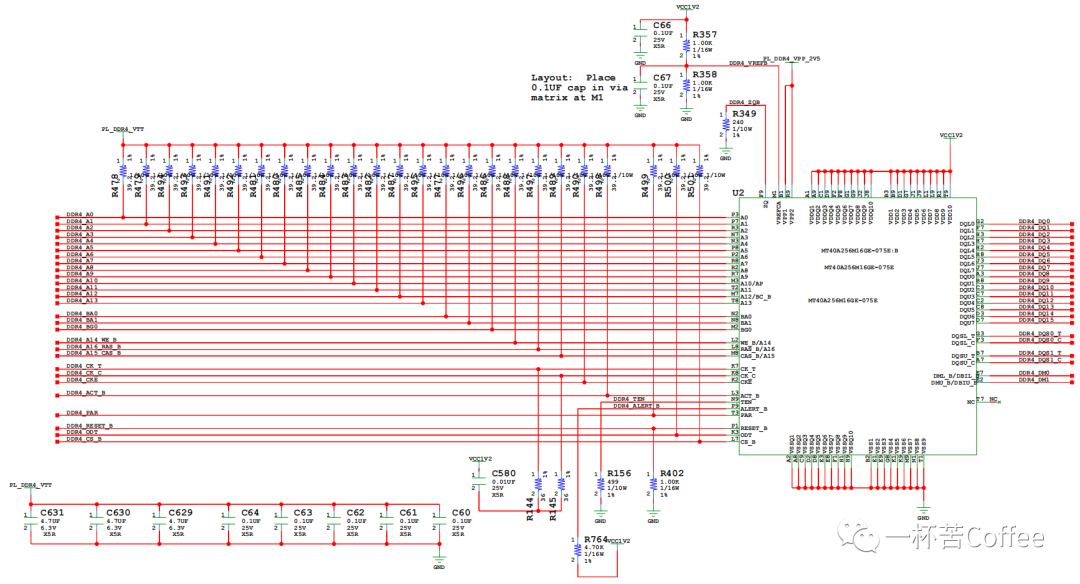

- DDR4电路设计案例

DDR4应用最为广泛,原因有两个:

- DDR4的存储速率能满足大部分工程师的需求;

- DDR5的走线对设计者的要求比较高。

NOR Flash/NAND Flash和SRAM的数据线和地址线通常是复用的

-

SDRAM

+关注

关注

7文章

423浏览量

55202 -

存储器

+关注

关注

38文章

7484浏览量

163759 -

电路设计

+关注

关注

6673文章

2451浏览量

204122 -

DDR

+关注

关注

11文章

712浏览量

65317 -

DDR2

+关注

关注

1文章

100浏览量

41552

发布评论请先 登录

相关推荐

怎么成为硬件电路设计高手?

硬件电路设计的思路分享

硬件电路设计之“磁珠”的应用资料下载

硬件电路设计之DDR电路设计(1)

硬件电路设计之DDR电路设计(1)

评论