什么是D触发器?

D触发器(D Flip-Flop)是一种数字电子电路,用于延迟其输出信号(Q)的状态变化,直到时钟输入信号的下一个上升沿出现。

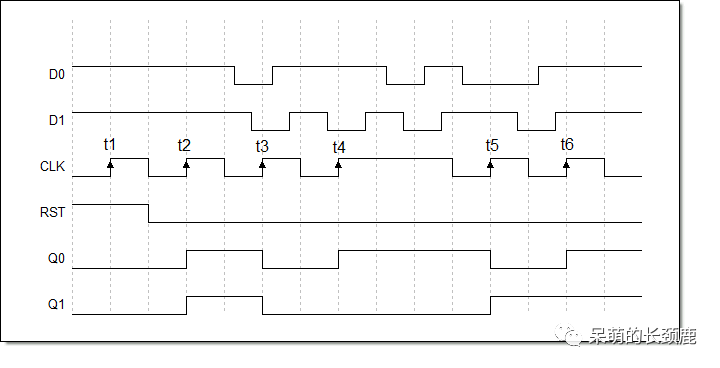

输出Q在输入CLK的每个上升沿时保存输入D的数值,等到输入CLK的下一个上升沿出现才会重新读取输入D的数值,输入RST为1时输出Q输出值为0且保持不变。

时间图如下:

特征表如下:

其中:RST:重置, CLK:时钟, D0、D1:输入 Q0、Q1:输出

*假设最初 RST 是高电平 ( RST = 1),无论D0 和 D1是否高电平,输出 Q0 和 Q1 是低电平 (Q = 0);

*当输入RST为低电平(RST = 0),在CLK脉冲的上升沿处,Q0=D0,Q1=D1,并保持数值到下一个CLK脉冲。

源代码如下:

FUNCTION_BLOCK "FF2E"

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

D0 : Bool;

D1 : Bool;

CLK : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q0 : Bool;

Q1 : Bool;

END_VAR

VAR

edge : Bool;

END_VAR

BEGIN

IF #RST THEN

#Q0 := FALSE;

#Q1 := FALSE;

ELSIF #CLK AND NOT #edge THEN

#Q0 := #D0;

#Q1 := #D1;

END_IF;

#edge := #CLK;

END_FUNCTION_BLOCK

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

D触发器

+关注

关注

3文章

164浏览量

47901 -

RST

+关注

关注

0文章

31浏览量

7394 -

时钟信号

+关注

关注

4文章

448浏览量

28542 -

CLK

+关注

关注

0文章

127浏览量

17156

发布评论请先 登录

相关推荐

d触发器有几个稳态 d触发器和rs触发器的区别

D触发器的稳态 D触发器是数字电路中常用的一种存储元件,它有两种稳态,即低电平稳态和高电平稳态。当输入D为低电平时,输出Q保持为低电平;当输

d触发器的逻辑功能 d触发器sd和rd作用

D触发器是一种常见的数字逻辑电路,它在数字系统和计算机中扮演着重要的角色。本文将详细探讨D触发器的逻辑功能、工作原理以及RD(Reset-D

t触发器与d触发器的区别和联系

在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的是T触发器(Toggle Flip-Flop)和D

d触发器是电平触发还是边沿触发

D触发器(Data Flip-Flop)是一种常见的数字逻辑电路元件,主要用于存储一位二进制数据。D触发器可以是电平触发的,也可以是边沿

t触发器变为d触发器的条件

在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的有JK触发器、D触发器和T

D触发器,请查收!

D触发器,请查收!

评论