3、状态机建模工具使用示例

3.1. 使用状态机建立电阻模型

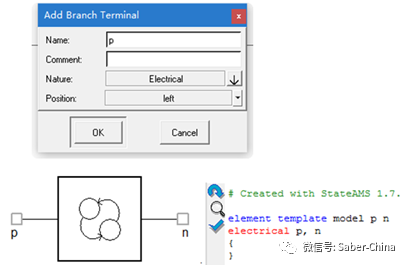

第一步****添加电阻端口

假设电阻阻值为r_normal,首先打开状态机建模工具,添加电阻端口,电阻端口包含贯通变量电流和跨接变量电压,使用分支型端口。

第二步****添加变量

添加电阻阻值r_normal为外部静态变量

添加电流变量ipn

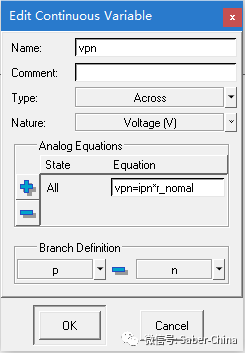

添加电压变量vpn

第三步****添加状态图

电阻在整过过程中没有状态变化,双击变量vpn,设置如下

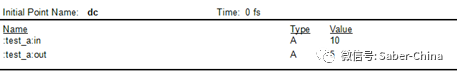

设置完成后,保存模型,搭建一个简单的电路测试电阻模型是否正确。

3.2. 使用状态机创建可变电阻

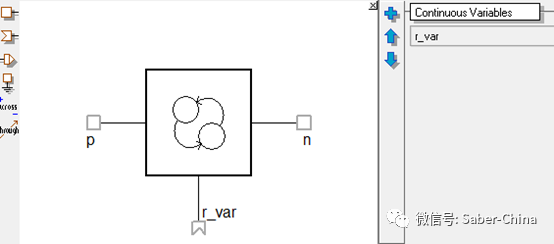

可变电阻的电阻值由外部管脚r_var控制。

首先建立symbol端子如下,设置p和n为electrical量

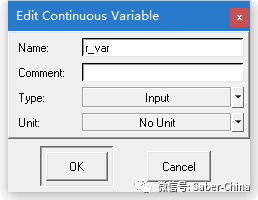

其中r_var是可变电阻的控制端。变量类型为

添加电阻的电压变量vpn(依次点击左侧across图标、p端口、n端口)和电流变量ipn(依次点击左侧through图标、p端口、n端口)

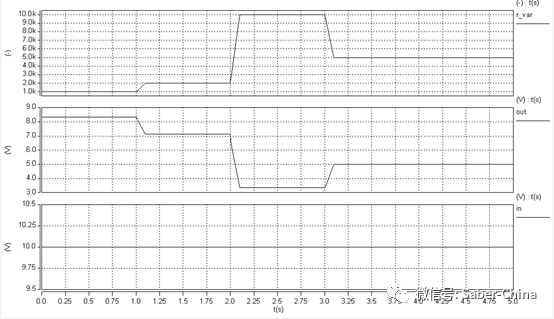

保存模型,搭建简单电路进行验证。

3.3. 创建基于公式的模型

如下公式是压控电机中的一部分算法,三相正弦交流电压幅值由控制电压U_control,增益gain。偏置U_offset控制。频率由f控制。

U_amp=U_control*gain+U_offset

U_a=U_ampsin(2pift)

U_b=U_ampsin(2pift+ 2*pi/3)

U_c=U_ampsin(2pift -2*pi/3)

建模时分两个状态机进行创建,vfconst和uf2abc。vfconst实现第一个公式,uf2abc实现后三个公式。

3.3.1. vfconst

建立symbol端子如下图,u_offset和f是输入,uout和fout是输出,单位都是 nunit。

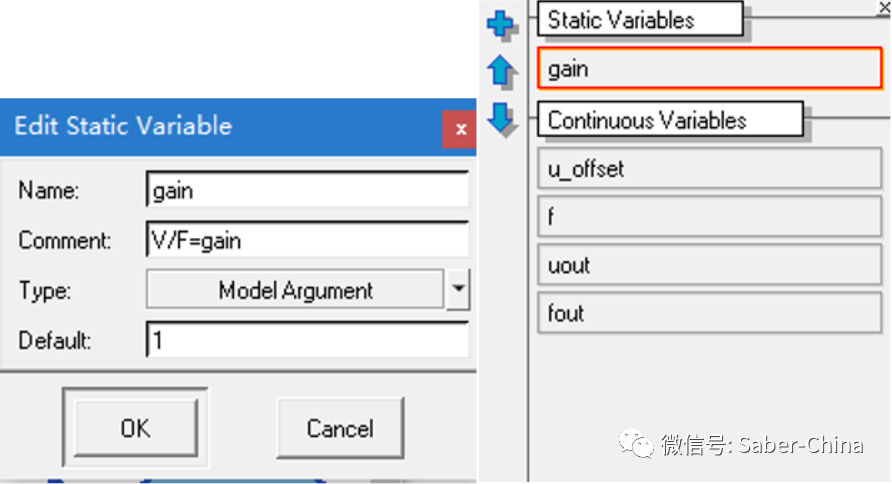

创建模型静态变量gain

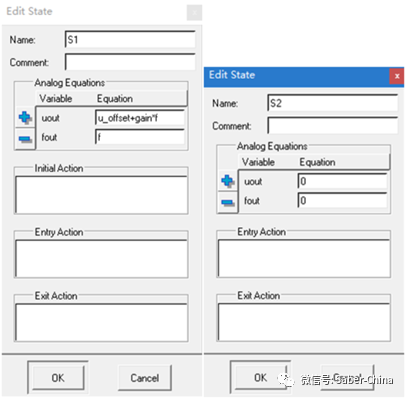

建立两个状态图S1和S2,状态关系为如果频率小于等于0时,进入state2,如果频率大于0时进入state1。、

鼠标双击state1和state2设置两个输出变量的公式,保存模型。

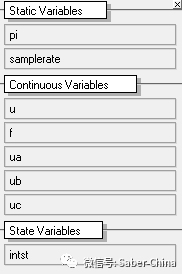

3.3.2. uf2abc建模

建立输入输出管脚,输入管脚u,f,输出管脚 ua,ub,uc。单位都是no unit。

创建两个ststic 变量,pi和samolerate,pi即3.141593,samplerate用来控制模型的最大采样间隔时间。创建一个state变量,配合下文的clk模块正常运行。

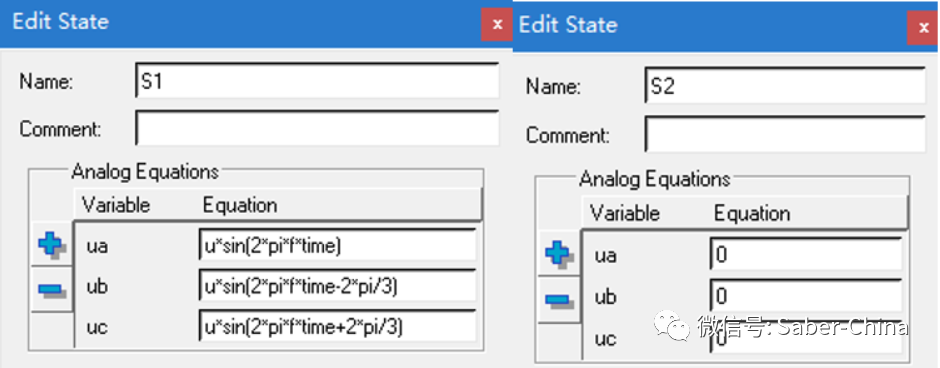

建立两个状态图S1和S2,状态关系为如果频率小于等于0时,进入state2,如果频率大于0时进入state1。

鼠标双击state1和state2设置两个输出变量的公式

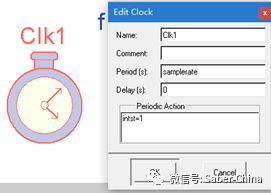

添加一个时钟源clk1,时钟源的周期为samplerate,每个周期内做的事为给intst变量赋值为1,这样处理的意义是:保证saber仿真器在计算ua,ub,uc的值在一个1/f周期内有足够的采样点。因为仿真器的步长会变,如果f变大的话,可能导致一个1/f周期内采样点不够,导致波形失真。samplerate可以依据1/20*fmax来考虑。

模型创建好后可以搭建一个简单电路进行验证。

3.4. 创建IGBT信号驱动模型

IGBT驱动器模型可将逻辑数字信号转换为电压信号输出以驱动IGBT模型工作。

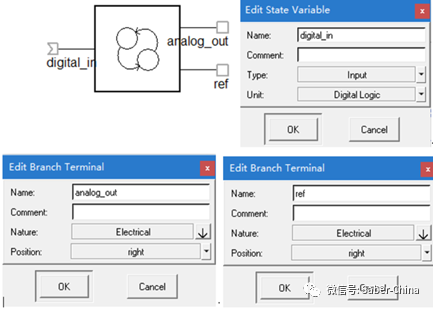

输入为数字逻辑信号digital_in,输出是模型信号analog_out,参考ref,高电平输出电压为vgon,低电平输出电压为vgoff,电平切换时间transition_time。

创建模型端口,digital_in输入,逻辑信号。analog_out和ref输出,电信号。

创建全局变量vgon,vgoff和transition_time

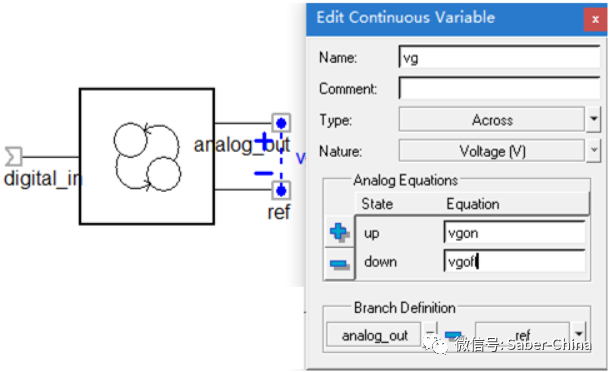

设置analog_out的电压输出变量vg。

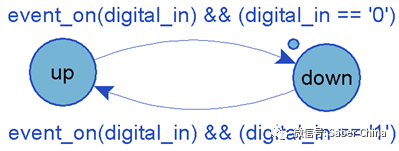

创建两个state,分别命名为up和down。up状态下设置vg=vgon,down状态下设置vg=vgoff。digital_in=0时切换到down模式,等于1时,切换到up。

使用event_on函数判断digital_in的状态变化,使用digital_in == '0'或digital_in == '1‘判断逻辑电平是高还是低。

mast语言中,高电平使用’1’表示,低电平使用’0’表示。

状态切换时间设置为transition_time

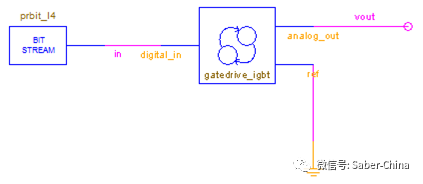

设置完成后保存模型,建立验证电路测试模型。

-

可变电阻

+关注

关注

0文章

46浏览量

15700 -

状态机

+关注

关注

2文章

492浏览量

27526 -

交流电压

+关注

关注

2文章

188浏览量

16900 -

控制电压

+关注

关注

0文章

35浏览量

16071 -

CLK

+关注

关注

0文章

127浏览量

17158

发布评论请先 登录

相关推荐

有限状态机的建模与优化设计

用状态机原理进行软件设计

如何构建基于状态机的软件系统

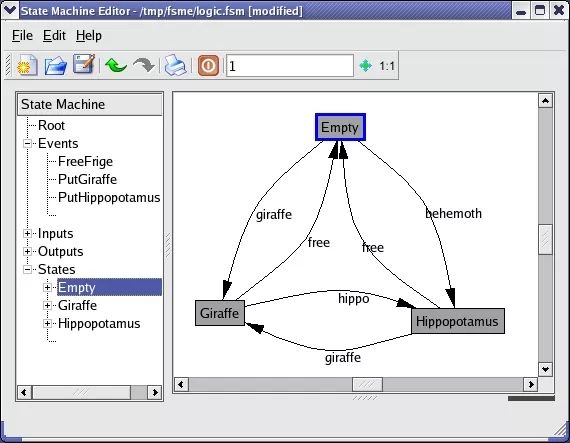

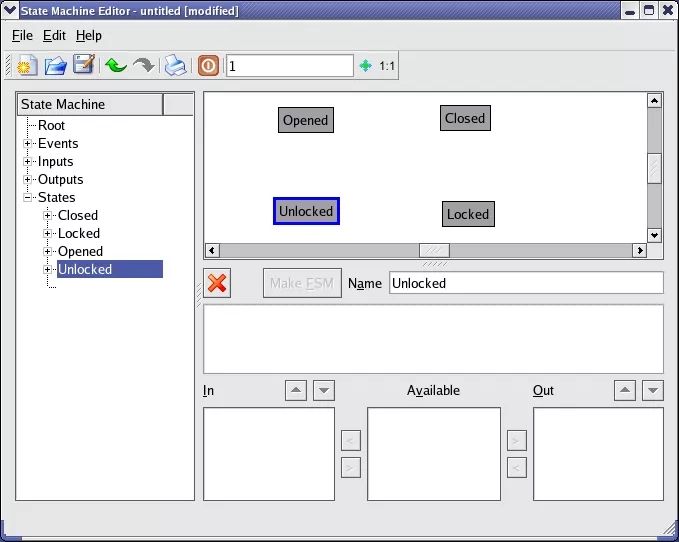

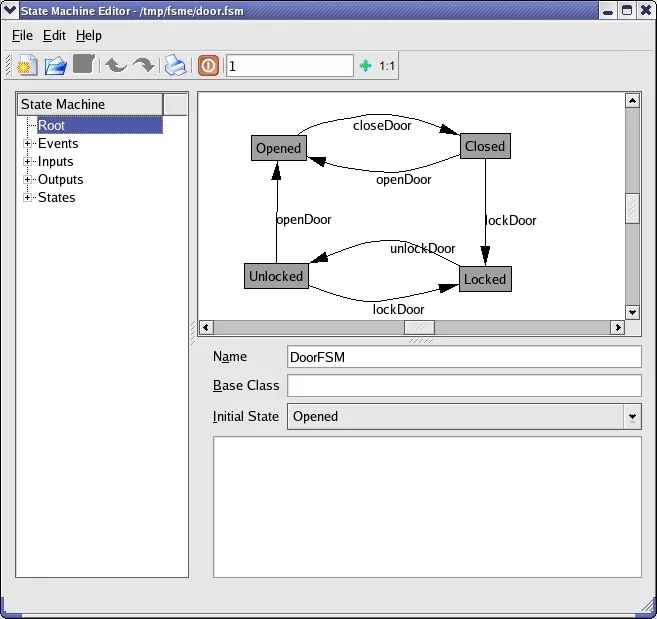

状态机自动生成工具FSME

自动生成程序状态机代码状态机建模方法

如何生成状态机框架

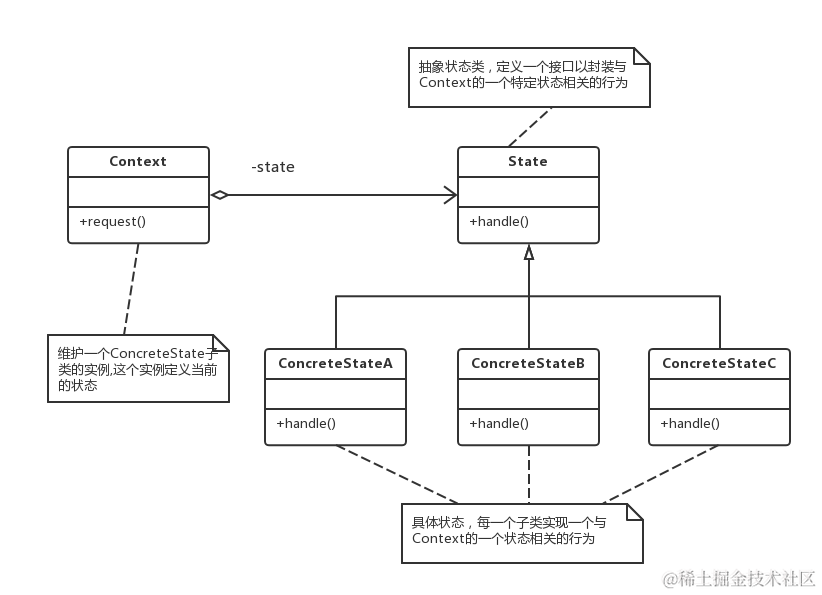

什么是状态机?状态机的种类与实现

什么是有限状态机?如何解决传统有限状态机「状态爆炸」问题?

SaberRD状态机建模工具介绍(二)状态机建模工具使用示例

SaberRD状态机建模工具介绍(二)状态机建模工具使用示例

评论