一、概述

1.1释义

10 Giga bit Ethernet,缩写为10GE、10GbE,俗称万兆网,是一种以太网的传输标准,最初在2002年通过,成为IEEE Std 802.3ae-2002,它规范了以10Gbit/s的速率来传输的以太网。

1.2分类

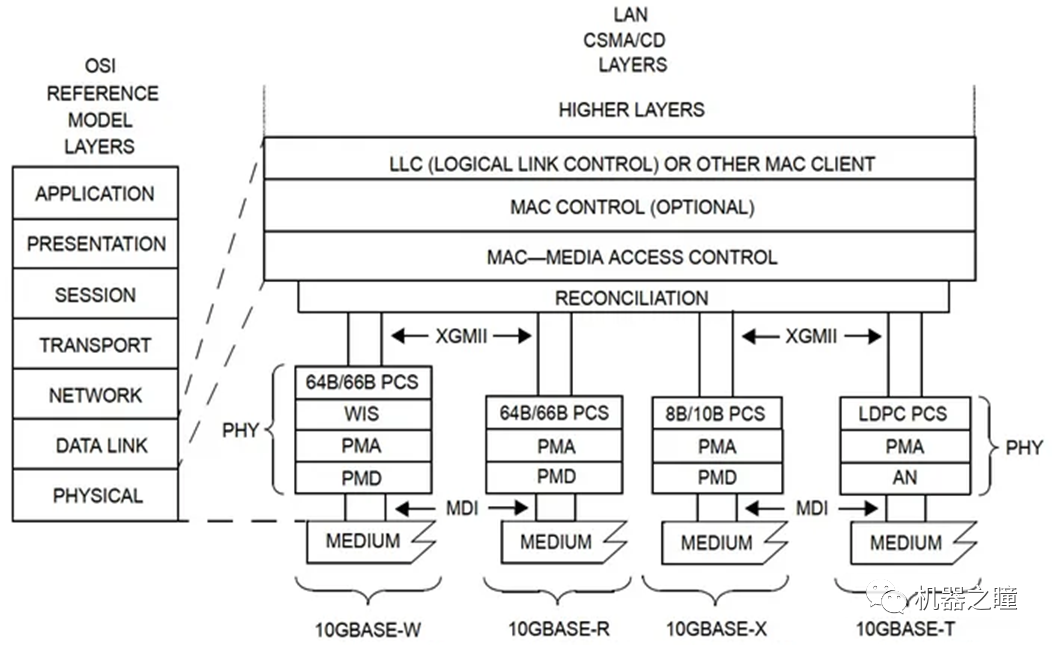

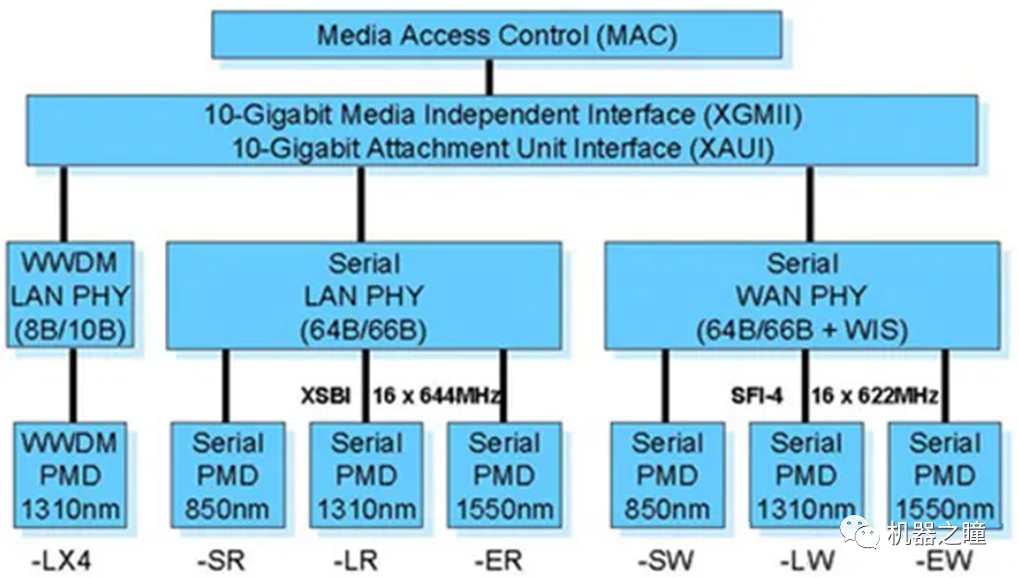

10G以太网的物理层包括10GBASE-T、10GBASE-X、10GBASE-R和10GBASE-W。

1.2.1 10GBASE-T

10GBASE-T(IEEE 802.3an)通过非屏蔽双绞线或屏蔽双绞线电缆,CAT-6的传输距离可达55米(180英尺),而CAT-6A则可达到100米(330英尺)。10GBASE-T采用在各种以太网中广泛使用的RJ45接口。根据传输的特性,传输时频率需要达到500MHz,IEEE 802.3an标准规定了用于10GBASE-T的PAM-16编码。在IEEE Std802.3ae-2002的标准中并没有10GBASE-T,因为他是在2006的标准中发布的,其标准是IEEE 802.3an-2006。

1.2.2 10GBASE-X

10GBASE-X使用一种特紧凑包装,含有1个较简单的WDM器件、4个接收器和4个在1300nm波长附近以大约25nm为间隔工作的激光器,每一对发送器/接收器在3.125Gbit/s速度(数据流速度为2.5Gbit/s)下工作。

1.2.3 10GBASE-R

10GBASE-R是一种使用64B/66B编码(不是在千兆以太网中所用的8B/10B)的串行接口,支持在光介质上传输。数据流为10.000Gbit/s,因而产生的时钟速率为10.3Gbit/s。

1.2.4 10GBASE-W

10GBASE-W是广域网接口,与SONET OC-192兼容,其时钟为9.953Gbit/s,数据流为9.585Gbit/s。

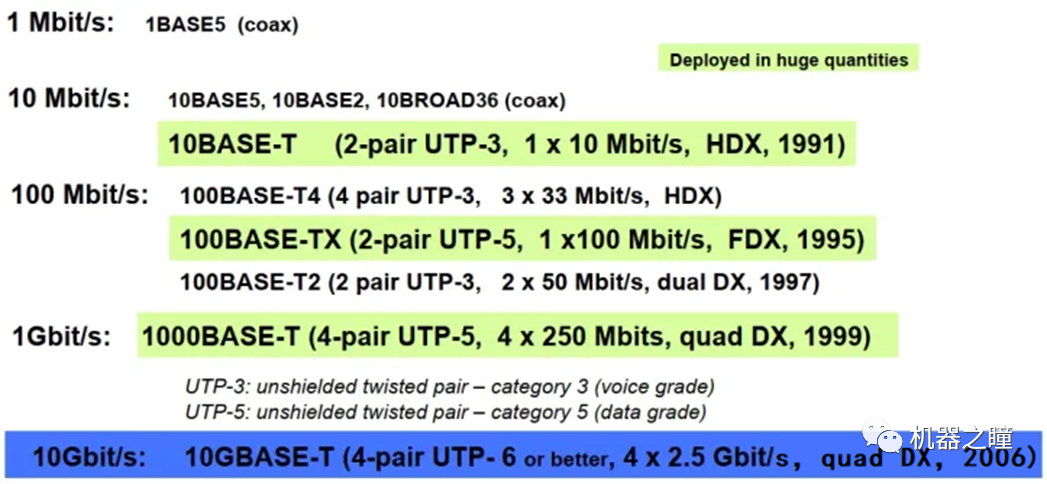

1.3发展

以太网的技术演进主要是以速度不断提升为标志的,从最初的1M、10M提升到10G甚至上百G,下图给出了以双绞线为传输介质以太网的速度提升和线束变化。

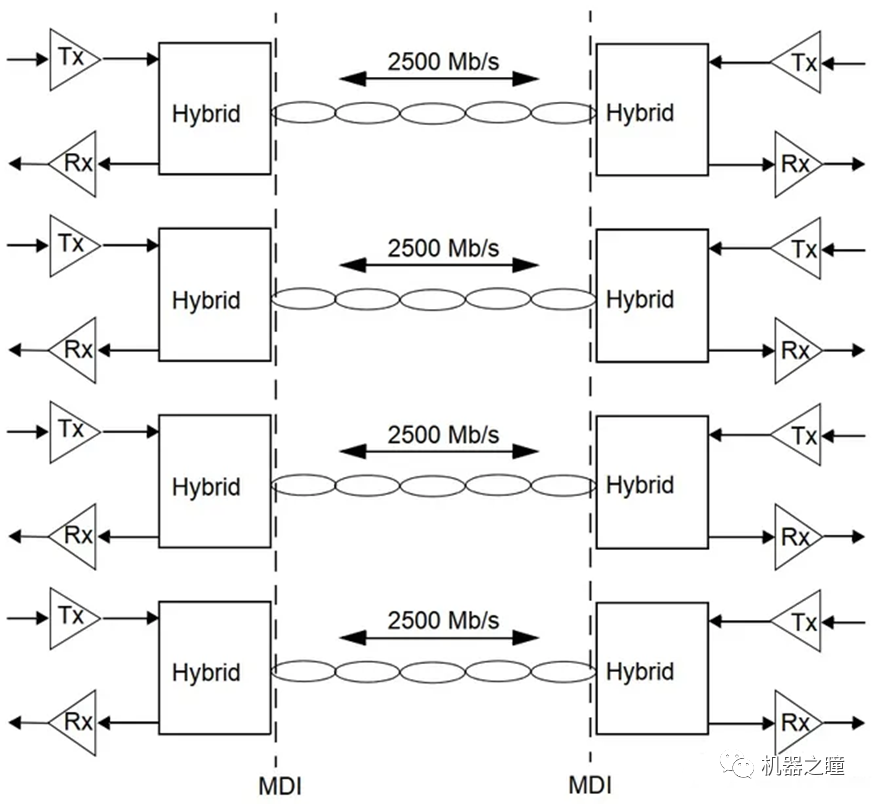

二、原理

标准制定者依靠4项技术构件使10GBase-T变为现实:损耗消除、vwin 到数字转换、线缆增强和编码改进。10GBase-T沿用1000Base-T的传输方式,仍然采用四个差分对同时双向传输,全双工,但传输的总速率高达10Gbps,每对线的速率高达2.5Gbps。在编码方面,不是采用原来1000Base-T的PAM-5,而是采用了PAM-16编码方式。

在前面介绍的四种物理层技术里面,现在10GBASE-R和10GBASE-T是应用的比较多的,10GBASE-R用于光模块的接口,10GBASE-T则是电口,使用RJ45和双绞线进行信号传输。

2.1结构

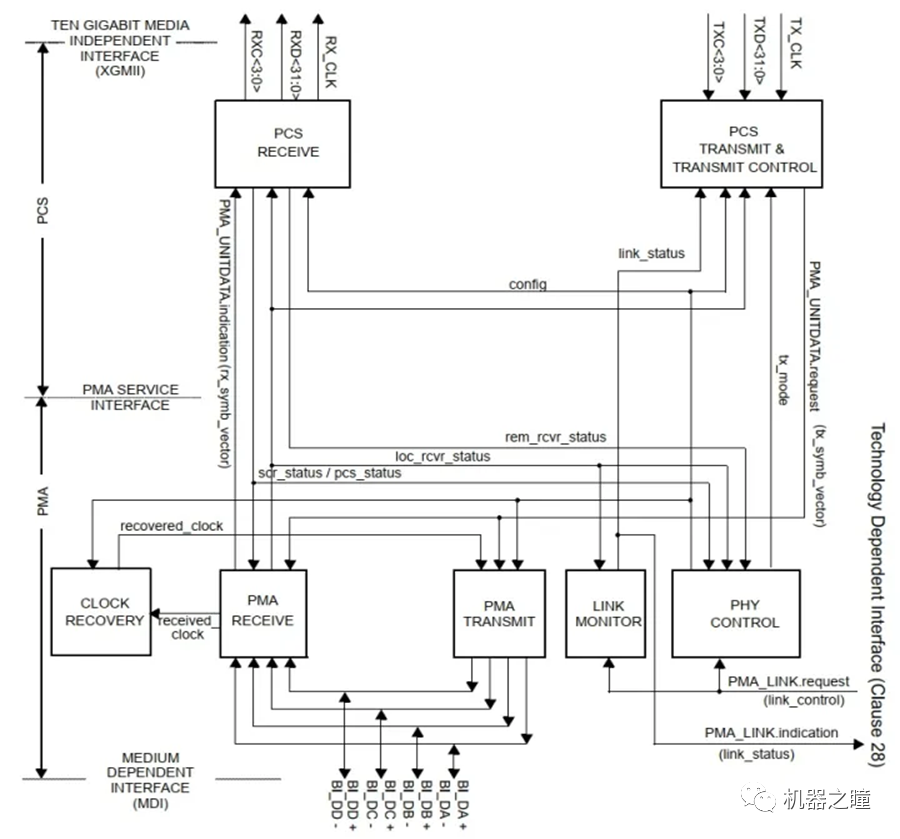

下图是从IEEE 802.3an-2006截取的,可以看出不同的物理层标准之间的差异。

物理层即PHY,分层为多个子层,主要完成数据编码校验和转换成模拟信号的功能。

XGMII,10G媒体独立接口(这里的“X”在罗马数字中表示10)用来使10G以太网下面不同的几个物理层对上面的MAC子层透明。其实和百兆网里面的RMII接口是一样的性质,只是传输的数据高达10Gbps,但是现在多用XAUI来代替。

PCS,物理编码子层,用来对数据进行编码(在发送数据时)和解码(当接收数据时)。

PMA,物理媒体连接子层,向PCS子层提供与媒体无关的方法,以支持使用面向串行比特的物理媒体。

PMD,物理媒体相关子层,定义物理层信令和媒体相关接口(MDI),以及所支持的媒体类型。需要指出的是,PMD子层是光信号子层,其主要功能是进行光信号的发送和接收,而PMD以上的各层都是使用电信号。

WIS,广域网接口子层,仅在广域网物理层中使用,它处在PCS子层和PMA子层之间。广域网接口子层的作用就是进行SONET/SDH组帧。

AN,自动协商子层(AUTO-NEGOTIATIONSUBLAYER),允许两端的PHY通告其功能(速度,PHY类型,半双工或全双工)并自动选择操作模式以在链路上进行通信,仅在10GBASE-T中使用。

MDI,媒体相关接口,用来将PMD子层和物理层的线缆连接。

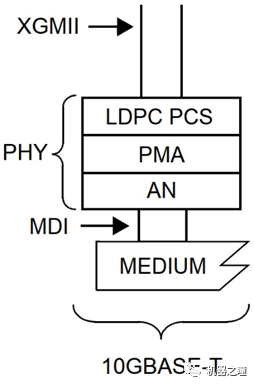

10GBASE-T的结构包含PCS、PMA和NA三层,有MII和MDI两个接口。其PCS层前多了一个LDPC,这个是低密度奇偶校验功能(low density parity check)。

2.2媒体独立接口

媒体独立接口是媒体访问控制(MAC)子层和物理层(PHY)之间的接口。XGMII是一种简单、廉价且易于实现的互连接口。我们也可以选择使用10千兆位连接单元接口(XAUI)来以减少的引脚数来扩展XGMII的操作距离。当然,由于XGMII的线数太多,并且距离较短,现在基本都是使用XAUI。

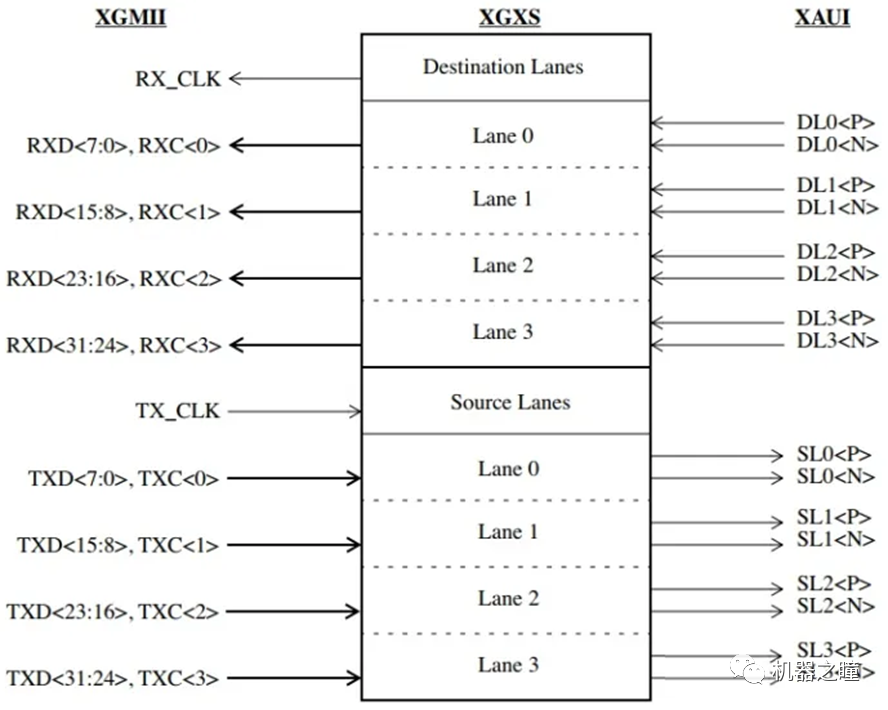

XAUI和XGMII之间既是替代关系,也可是扩展关系,这里先给出XGMII XAUI的图。

2.2.1 XGMII接口

XGMII接口的单端信号采用HSTL/SSTL_2逻辑,端口电压1.5V/2.5V,由于SSTL_2的端口电压高,功耗大,现在已很少使用。XGMII的通信线分为数据线、控制线和时钟线,收发对称,数据32根,控制线4根,时钟线一根。

TXD[31:0],发送信号线。

RXD[31:0],接收信号线。

TXC[3:0],发送通道控制信号,TXC=0时,表示TXD上传输的是数据。TXC=1时,表示TXD上传输的是控制字符。

RXC[3:0],接收通道控制信号,RXC=0时,表示RXD上传输的是数据。RXC=1时,表示RXD上传输的是控制字符。

TX_CLK,TXD和TXC的参考时钟,时钟频率156.25MHz,在时钟信号的上升沿和下降沿都采样数据。

RX_CLK,RXD和RXC的参考时钟,时钟频率156.25MHz,在时钟信号的上升沿和下降沿都采样数据。

156.25MHz×2×32=10Gbps。

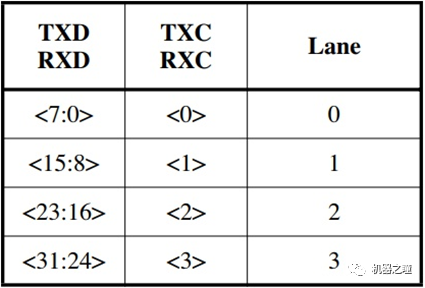

XGMII的收或者发的32根信号线被分成了4个lane,每个lane有一个控制信号,他们的对应关系如下图所示。

2.2.2 XAUI接口

XAUI借用了以太网“附加单元接口”的简称AUI(Attachment Unit Interface),首字母“X”代表罗马数字10,代表传输速率是每秒10G比特。和XGMII接口相比,XAUI接口大大简化。XAUI接口只有16条信号线,其中4对balanced差分线用于数据接收,4对balanced差分线用于数据发送,XAUI接口是自带时钟的串行总线。差分对使用CML逻辑,AC耦合方式,耦合电容在10nF~100nF之间。每对差分线上的数据速率为3.125Gbps,总数据带宽为12.5Gbps,有效带宽为12.5Gbps×0.8=10Gbps(因为XAUI总线数据在传输前进行了8b/10b变换)。

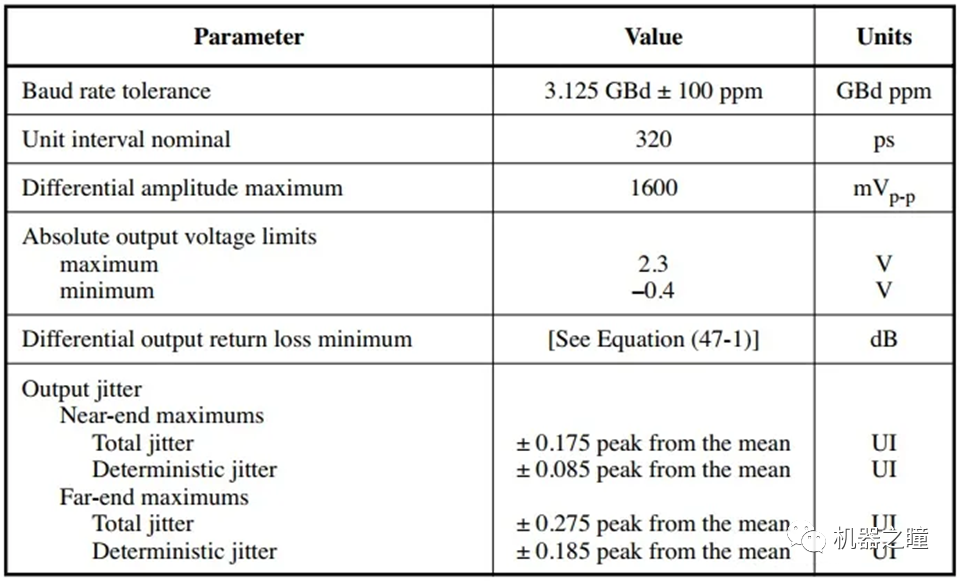

下面这张图是XAUI接口发送端的规格。

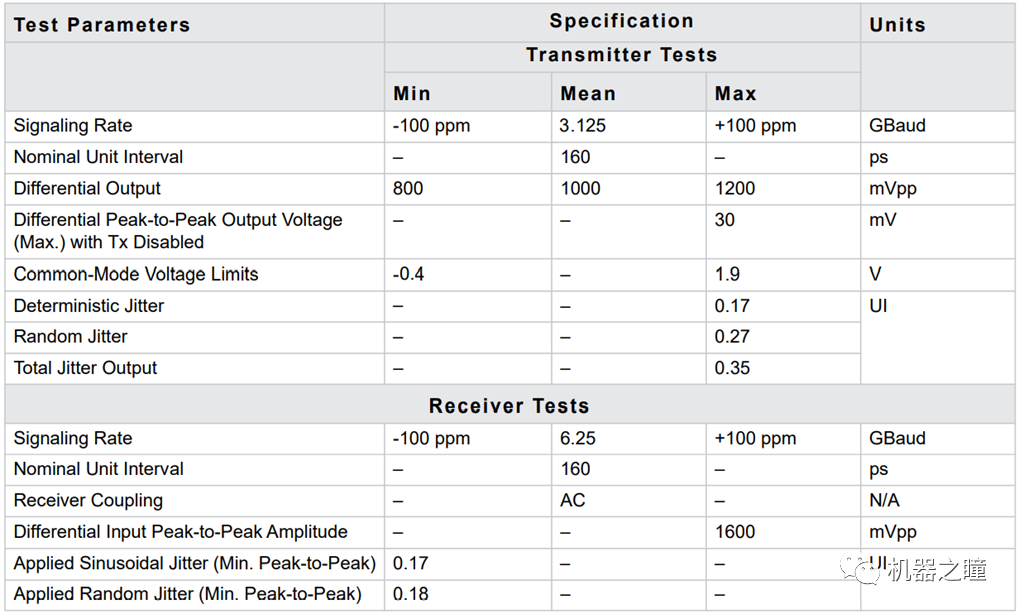

这里只规定了差分信号的幅度最大是1600mVpp,Marvell的88X3310里面使用的typical值是1000mVpp,最大值是1200mVpp,接收端允许的最大输入时1600mVpp,如下图所示。

差分对的阻抗要求是在2.5GHz测试条件下100欧姆±5%。相比于XGMII信号线数量大大减少,差分信号具备更强的抗干扰能力,从而简化了电路的走线设计。FR4 PCB板上,XAUI接口的走线长度可达50cm,而XGMII接口的走线长度只有7cm。XAUI接口的走线比较长,大大方便了PCB板的设计,背板走线成为可能。正如此原因,一般MAC芯片不提供XGMII接口给用户使用。但是,在芯片内部XGMII依旧作为标准接口使用。在MAC芯片内部,集成了XGXS(XGMII ExtenderSublayer)子层,用来实现XGMII接口和XAUI接口之间的双向映射,这就是前面那张图所展示的。

在XGAMII互转的过程是这样的,源端XGMII把收发32位宽度数据流分为4个独立的lane通道,每个lane通道对应一个字节,经XGXS(XGMII Extender Sublayer)完成8b/10b编码后,将4个lane分别对应XAUI的4个独立通道,XAUI端口速率为2.5Gbps×1.25×4=12.5Gbps。在发送端的XGXS模块中,将TXD[31:0]/RXD[31:0],TXC[3:0]/RXC[3:0],TX_CLK/RX_CLK转换成串行数据从TXLane[3:0]/RXLane[3:0]中发出去,在接收端的XGXS模块中,串行数据被转换成并行,并且进行时钟恢复和补偿,完成时钟去抖,经过5b/4b解码后,重新聚合成XGMII。

XAUI接口有如下一系列的变种,RXAUI、XLAUI(40Gb)、CAUI(100Gb)等。

XAUI接口可以直接接光模块,如XENPAK/X2等。也可以转换成一路10G信号XFI,接XFP/SFP+等。

2.2.3 MDIO接口

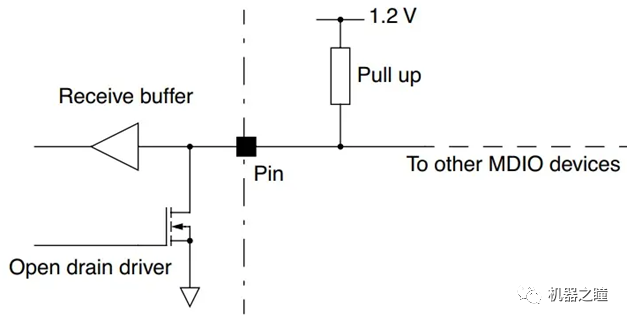

补充说明一下MDIO需要使用一个电阻进行上拉。

2.3编码技术

PCS层是物理编码子层,用来对MAC层通过XGMII或者XAUI发送来的数据进行编码以便通过MDI传输,当然也同样承担着解码任务。编码完成的任务是保证高速的数据能正常通过线缆进行传输。10GBASE-T需要每对双绞线上传输速率高达2.5Gbps的数据,这是极其有挑战的,而编码技术在这里面就起到至关重要的作用。

在车载以太网中也面临着高速传输抗干扰的问题,那里使用PMA3技术。在1000Base-T中使用的PAM5(5级脉冲调幅技术)调制技术。在PAM5模式下,介质中传输的信号不再是简单的0和1,而是分成了5个级别(-2、-1、0、1、2)。这个分为5个级别的电平信号称之为码元,1个码元所能携带的多少个bit的信息取决于码元的特性和编码的方式。比如PAM5,每个PAM5码元最多携带2.32个bit(2^2.32=5),考虑到编码的效率及需要纠错码和同步码,所以最终1000Base-T每个码元携带2个bit的信息。根据奈氏准则,理想低通信道下的最高码元传输速率=2×带宽,我们知道1000Base-T的码元速率为125M/秒,所以要求至少有62.5MHz的传输带宽。

如果沿用1000Base-T的技术,那10GBase-T的码元传输速率为1250M/秒,系统最小传输带宽为625MHz。这对传输系统的性能提出了很高的要求。但如果提高码元的性能,让一个码元携带更多的Bit,降低系统最小带宽,就需要强大的处理器进行编解码处理,那意味着成本的增加,这是一对矛盾。最后经过性能和成本的平衡,10GBase-T使用了PAM16技术(16级脉冲调幅,采用-15、-13、-11、-9、-7、-5、-3、-1、1、3、5、7、9、11、13、15),PAM16调制下,脉冲电压幅度分为16级电平,这样每个电压幅度可以表示4个bit的信息,其中3.125bit是有效数据,另外的0.875位用于辅助和校验等。当然,3.125和0.875都是平均值,800M每秒的码元速率,最小带宽要求400Mhz。

为了让PAM16能够安全的传输10Gbps(BER=10^12),就需要设置一定的编码规则。为了能够提高BER,还要加入校验码进行前向纠错,10GBase-T采用的LDPC码(低密度奇偶校验码)是一种线性分组码,具有优越的纠错性能和巨大的实用价值,被认为是迄今为止性能最好的纠错码。LDPC码的性能能够逼近香农极限,同时这种逼近又是在不太高的译码复杂度下实现的,硬件实现简单,同样兼顾性能和成本。

在10GBase-T编码过程中。每64个bit信息,加上控制/数据的标志位组成一个65bit的块(block),50个块编成一个组(Group),每个组加上8bit CRC校验码。一共生成65×50+8=3258个bit,再附加上一个通道附加码一共是3259个bit。3259个bit分成2个部分,3×512bit(含通道附加码)通过无保护方式传输,另外1723bit再加上325个校验码,通过LDPC(1723、2048)保护方式传输,这样共需要512个128DSQ编码(3×512+4×512),也就是1024个PAM16符号。最终相当于每个PAM16携带3.125个bit信息(64×50/1024=3.125),传输速率=3.125×800M×4=10Gbps。10G以太网PHY芯片的内部框图如下所示。

2.4MDI接口

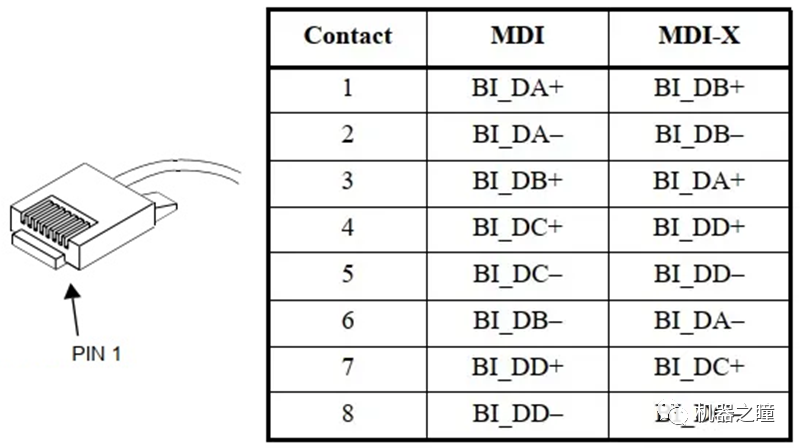

10GBASE-T使用的是RJ45和CAT-6以上规格的线缆进行传输,里面有四对双绞线线进行全双工通信。线序定义如下图所示。

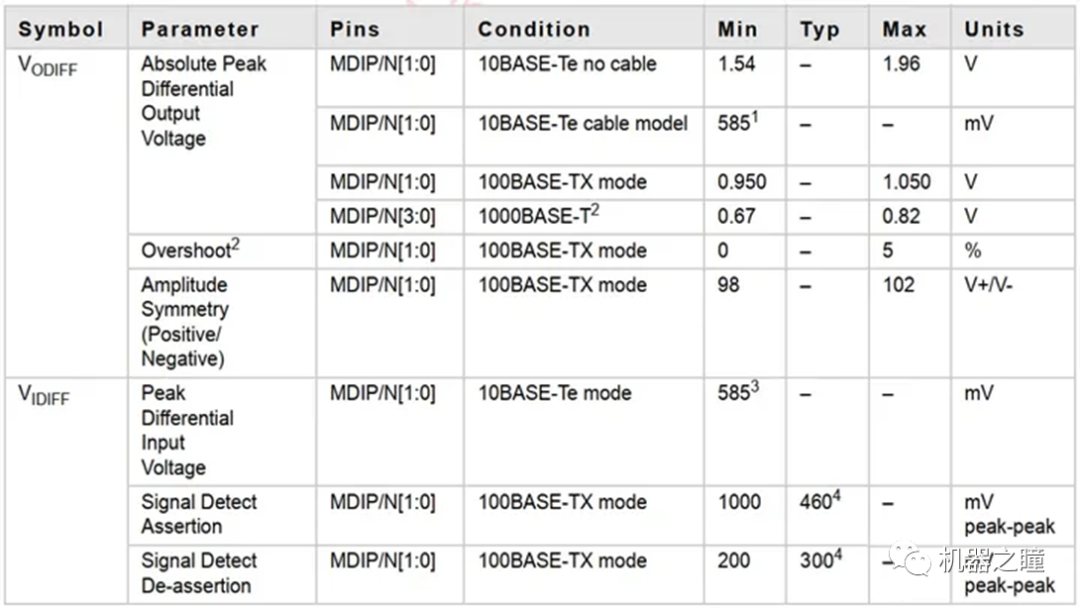

下图为某款芯片MDI接口差分对的spec。

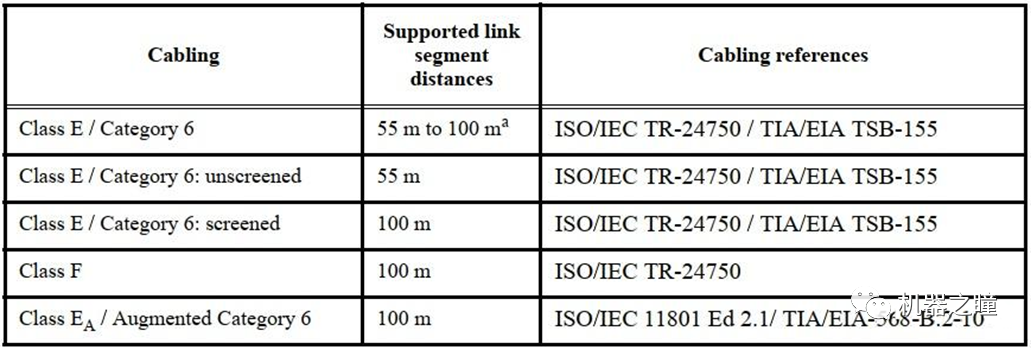

下图给出了不同规格的网线能达到的传输距离以及其对应的标准。

三、扩展

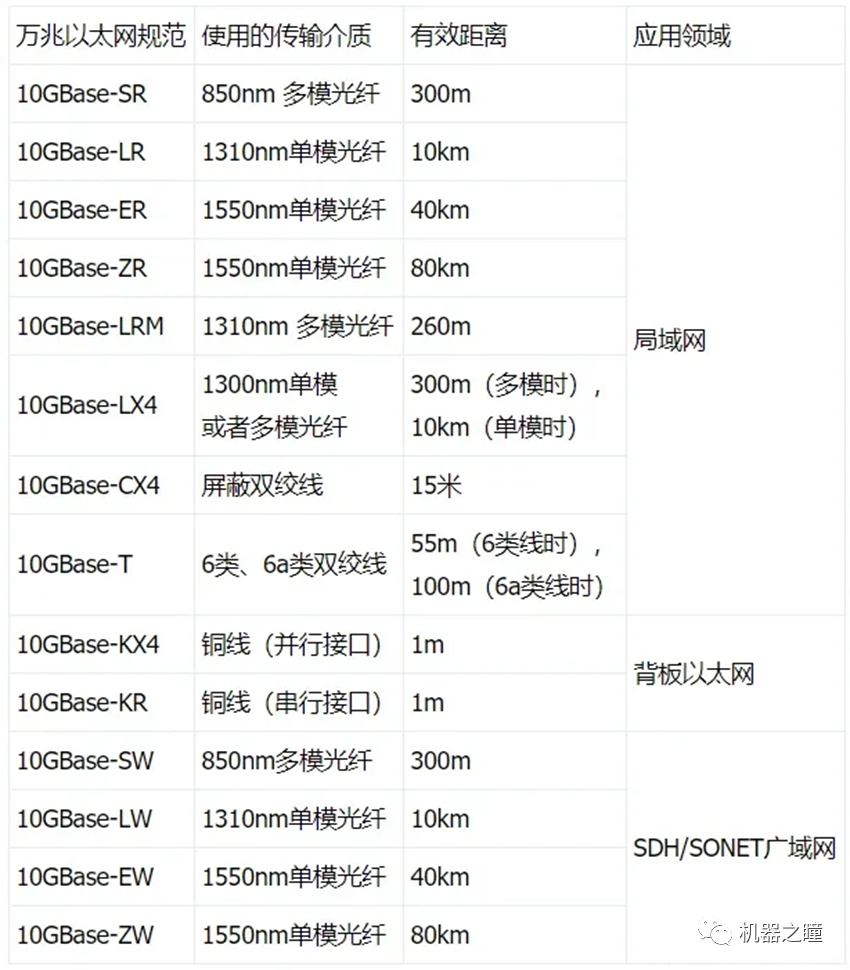

3.1命名规则

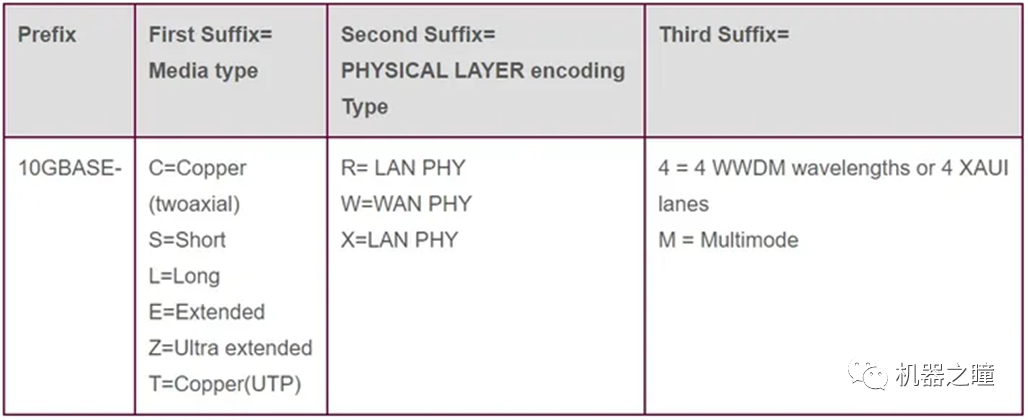

10G以太网采多种光纤媒介。光纤媒介的型号具体表示方法为10GBASE-[媒介类型][编码方案][波长数],或更加具体10GBASE-[E/L/S][R/W/X][4]。在媒介类型中S为短波长(850nm),用于多模光纤在短距离(约为35m)传送数据。L为长波长(1310nm),用于在校园网的建筑物之间或大厦的楼层间进行数据传输,当使用单模光纤时可支持10km的传输距离,而在使用多模光纤时,传输距离为300m。E为特长波长(1550nm),用于广域网或城域网中的数据传送,当使用1550nm波长的单模光纤时,传输距离可达40km。

在编码方案中,X为局域网物理层中的8B/1OB编码,R为局域网物理层中的64B/66B编码,W为广域网物理层中的64B/66B编码(简化的SONET/SDH封装)。最后的波长数可以为4,使用的是宽波分复用(WWDM)。在进行短距离传输时,WWDM要比密集波分复用(DWDM)便宜得多。如果不使用波分复用,则波长数就是1,并且可将其省略。

3.2IEEE802.3ae端口类型

来源:机器之瞳

审核编辑:汤梓红

-

以太网

+关注

关注

40文章

5419浏览量

171583 -

接口

+关注

关注

33文章

8573浏览量

151006 -

双绞线

+关注

关注

2文章

241浏览量

23671 -

物理层

+关注

关注

1文章

148浏览量

34354

发布评论请先 登录

相关推荐

一文了解万兆网技术

一文了解万兆网技术

评论