在高速信号传输中,信号传输线上的反射是一个重要的问题。当信号从信号源发送到终端设备时,信号在传输线上会遇到线路特性不连续的变化,如端口、接口或连接器的变化。这种变化导致信号的部分能量被反射回传输线中,形成反射波。这种反射波可能会干扰原始信号,引发信号完整性问题,如时序错误、眼图闭合不良等。

如何进行高速信号反射仿真

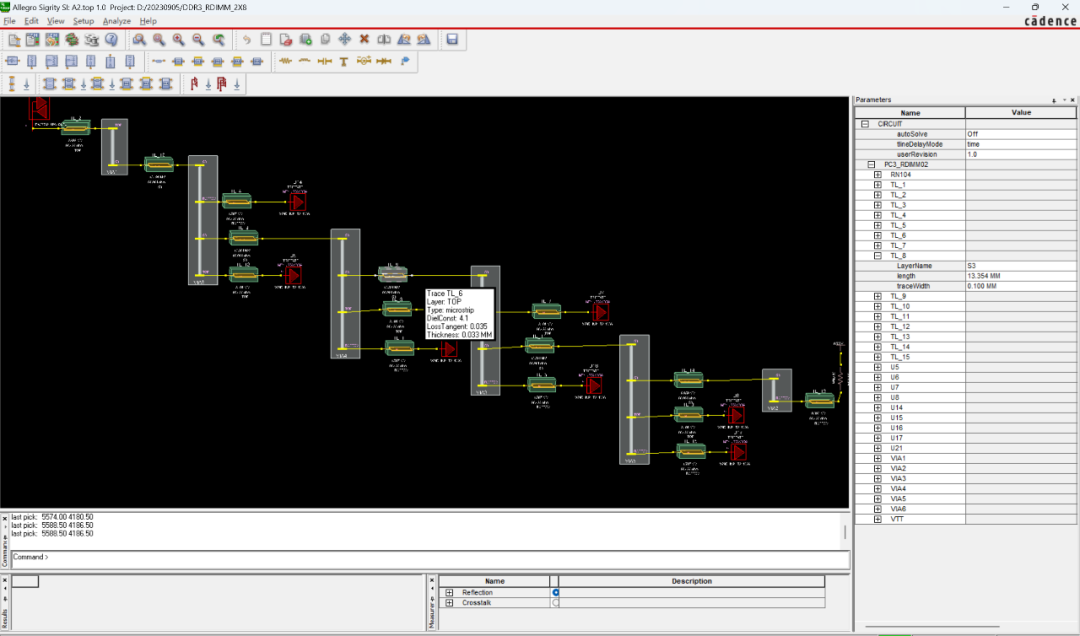

接下来我们使用SigXplorer来学习如何进行高速信号反射仿真。

Cadence SigXplorer软件是一种用于高速信号完整性分析和信号完整性的解决方案。它主要用于设计和验证电子产品中的高速信号传输线路,以确保信号的可靠性和稳定性。

SigXplorer可以对高速信号传输线路进行电磁仿真分析,包括考虑反射、传输线损耗、散射参数等因素。通过仿真,可以分析信号的传输特性,如延迟、振幅、眼图、时域波形等,帮助设计师评估信号完整性。

SigXplorer可以帮助设计师分析和优化信号传输线路的工程参数,例如线路几何、终端阻抗匹配、负载和驱动器配置等,以降低反射、串扰、眼图闭合等问题的风险。通过对不同设计方案进行仿真和比较,设计师可以选择最优的方案来提高信号完整性。

在高速信号传输时,传输线非理想线,包含分布参数如电容、电感和电阻,此时对于信号来讲这些参数形成的阻抗就是瞬时阻抗值。当信号在传输过程中遇到阻抗突变时,会导致部分能量返回,形成反射。

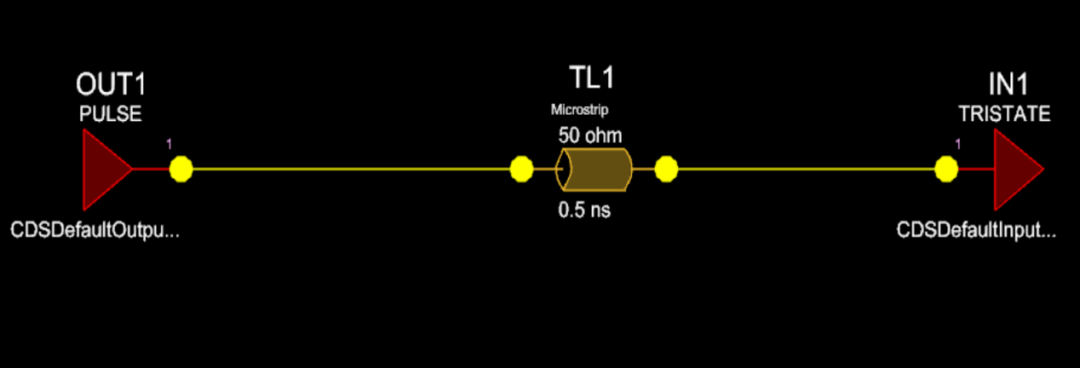

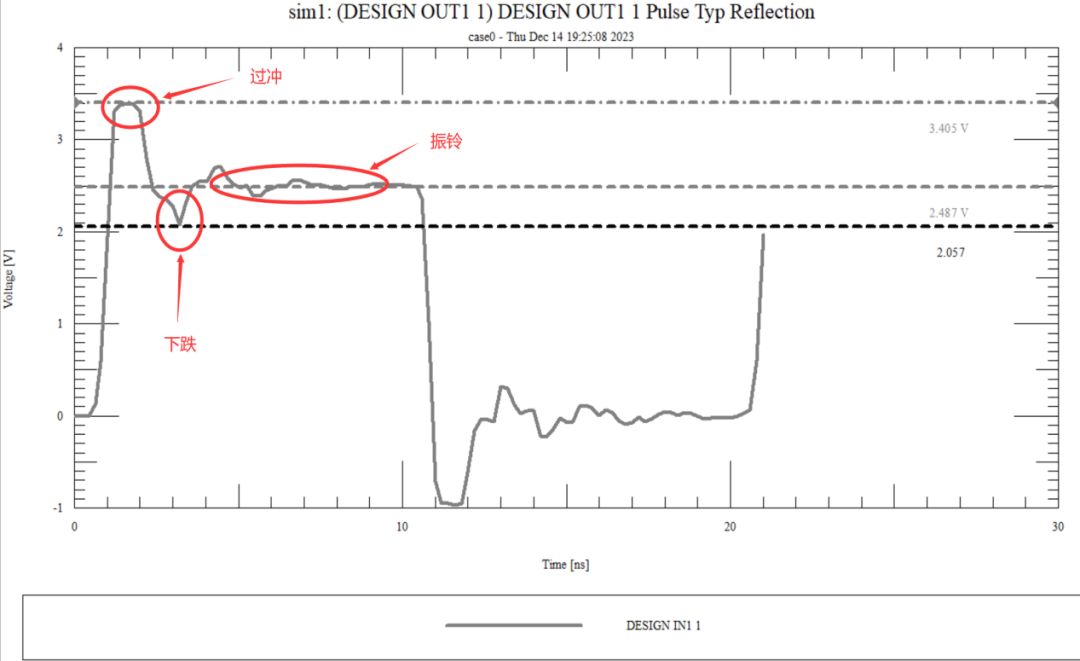

图 1

反射会造成过冲、过跌、振铃(信号来回反射)等问题。严重的过冲、过跌问题会导致信号传输错误。

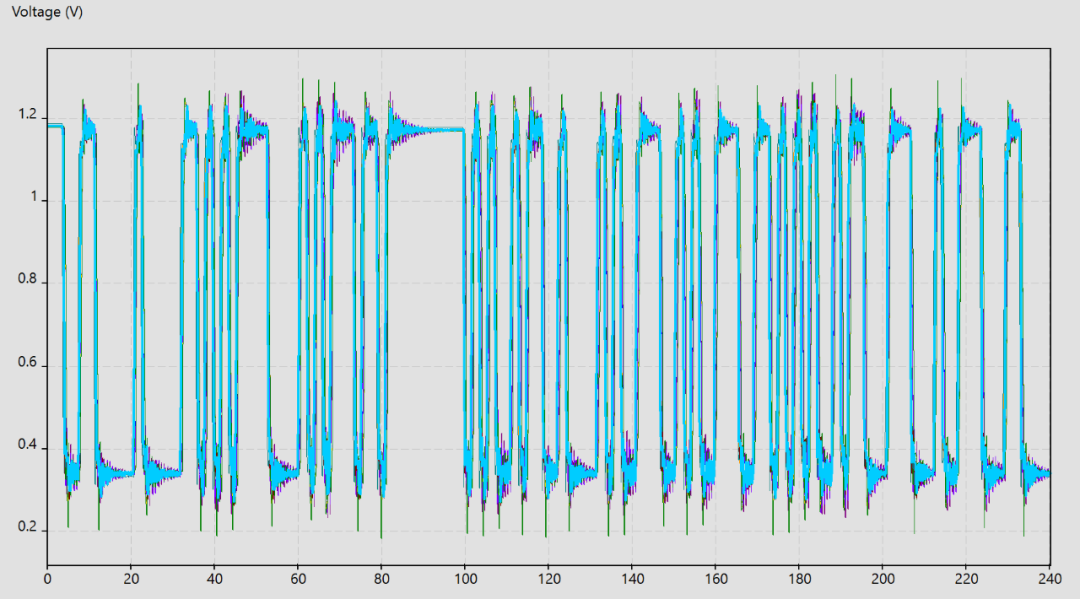

图 2

在图1的传输链路中,OUT1输入,内阻约10 Ohm,IN1端输出,内阻无穷大,传输线TL1阻抗50 Ohm。当发射端激励为2.5v,50MHz的方波时,接收的信号波形如图2所示。信号过冲到3.4V,然后下跌到2v,再经过反复震荡后稳定在2.5v。

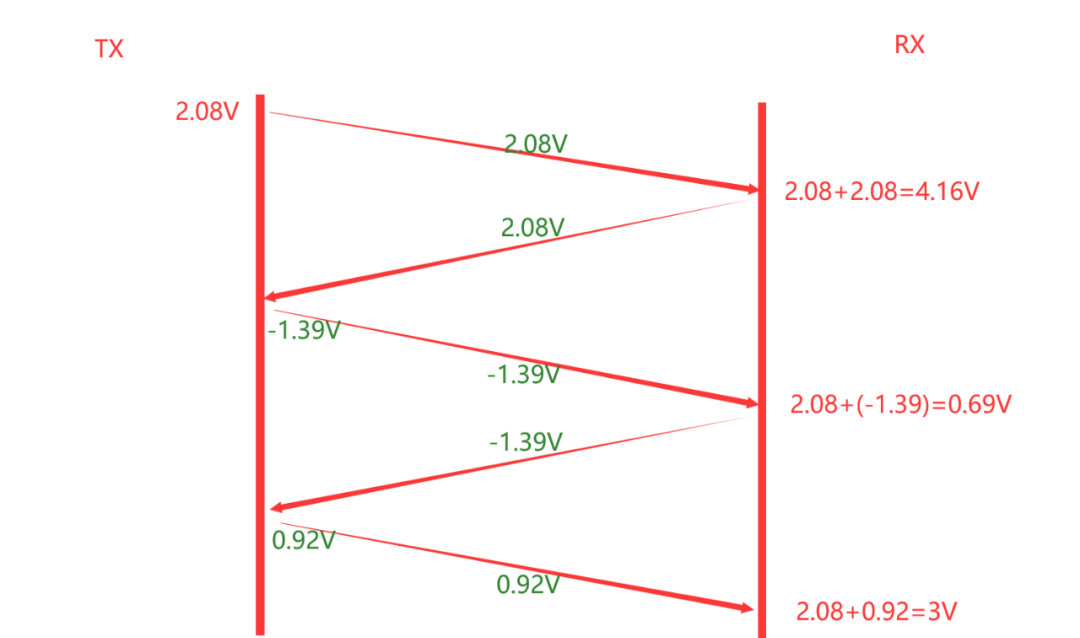

反射系数为(末端阻抗-始端阻抗)/(末端阻抗+始端阻抗),初始电压为发射端内阻10 Ohm与传输线50 Ohm的分压,即2.08V。具体反射过程如图3所示。(由于传输线损耗问题,理想情况下的理论计算与实际会有偏差)

图 3

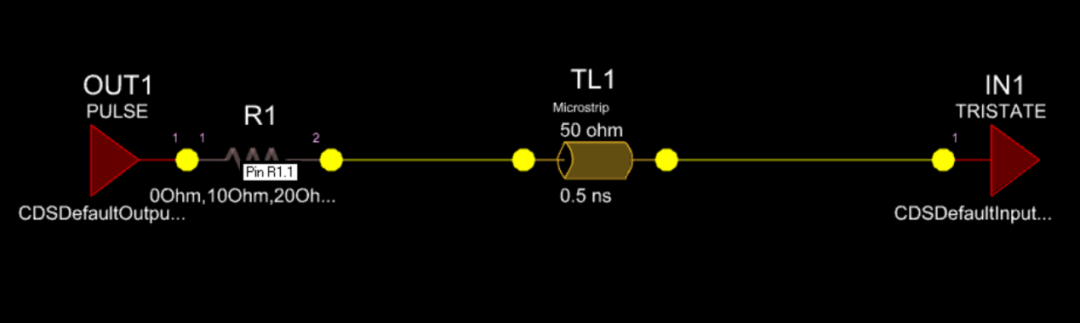

为了减少信号反射,可以采取一些措施,例如使用串联端接电阻。如图4所示。

图 4

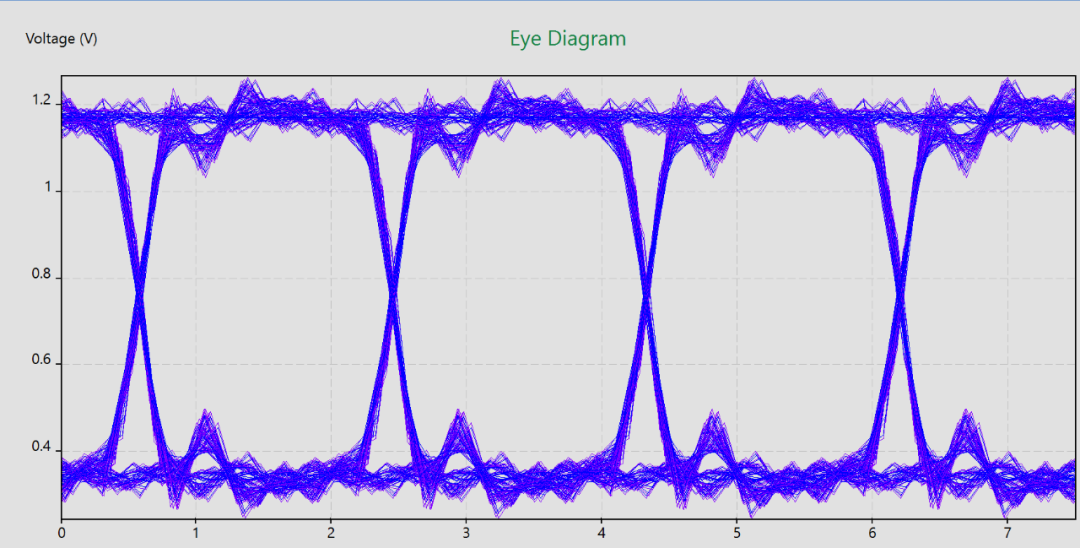

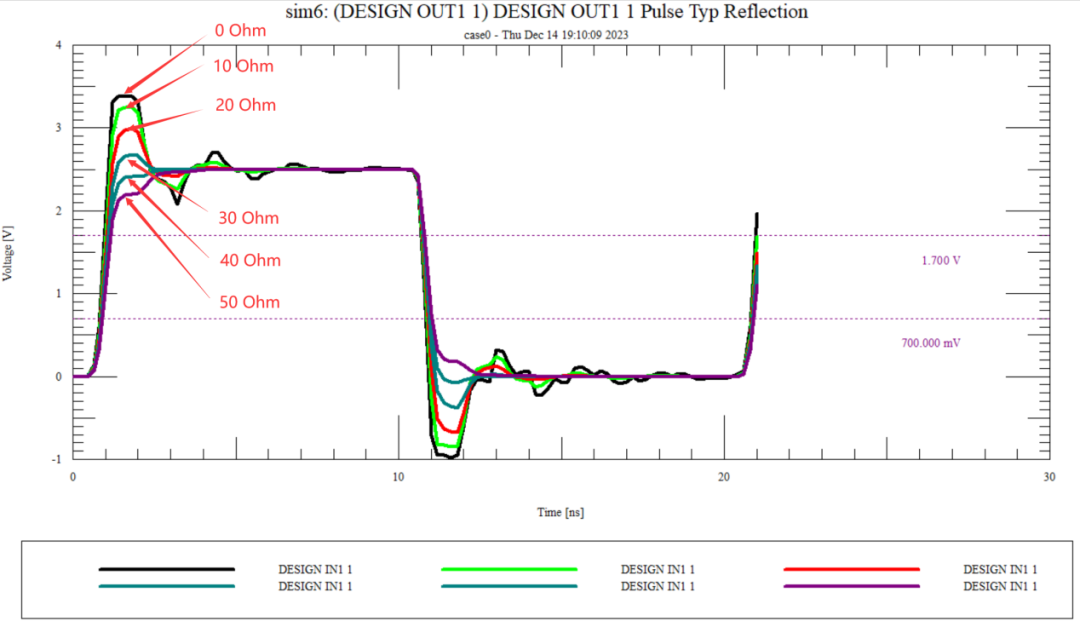

当串联的电阻阻值从0 Ohm到50 Ohm之间变化时,信号的反射也会相应变化,接收端的信号波形如图5所示。可以看出,当串联电阻为40 Ohm时,发射端内阻与40 Ohm电阻之和约等于传输线阻抗50 Ohm,从上述反射系数的计算方法可知,发射端一侧反射系数为0,而接收端一侧的反射系数仍然是1,所以,信号在接收端全部反射回来,在发射端不在反射,信号只经历一次反射,从而使信号的传输更稳定。

图 5

图 5

通常,发射端的输出阻抗较低,接收端的输入阻抗远高于传输线特性阻抗,如果不做任何处理,信号就会产生反射,影响信号传输质量。阻抗突变是产生反射的主要原因,在PCB设计过程中,需要尽可能避免阻抗突变,来提高信号传输质量。

SigXplorer软件主要用于高速信号完整性分析和优化。它帮助设计师评估和改进信号传输线路的性能,确保信号的可靠性和稳定性,以满足高速系统设计的要求。进行高速信号反射仿真分析可以帮助设计师更好地了解信号的传输特性和反射问题,从而优化设计,提高信号的完整性和可靠性。

上述过程是在SigXplorer中实现的仿真过程,目前Sigrity 2021最新版本的最新工具SigrityTopology Explorer不仅具有SigXplorer的拓扑自动提取、仿真与规则管理器集成等功能,还使用了与Sigrity SystemSI相同的模块设计和交互方式,IO model也可以直接使用IBIS模型,大大优化了SigXplorer的使用体验。

-

仿真

+关注

关注

50文章

4070浏览量

133550 -

传输线

+关注

关注

0文章

376浏览量

24021 -

高速信号

+关注

关注

1文章

225浏览量

17694

发布评论请先 登录

相关推荐

高速设计与PCB仿真流程

请教关于利用simulink进行脉冲反射法仿真研究的问题

信号反射的几个基本问题分析

【转载】Allegro SI 高速信号完整性仿真连载之三(附详细流程)

如何让信号反射仿真分析更加便捷高效?

避雷!高速信号和高速PCB理解误区

千兆SFP光信号收发卡高速电路PCB仿真设计

高速电路信号完整性分析与设计|—高速信号的反射分析

基于Hyperlynx的反射仿真与分析

如何使用SigXplorer进行高速信号反射仿真

如何使用SigXplorer进行高速信号反射仿真

评论