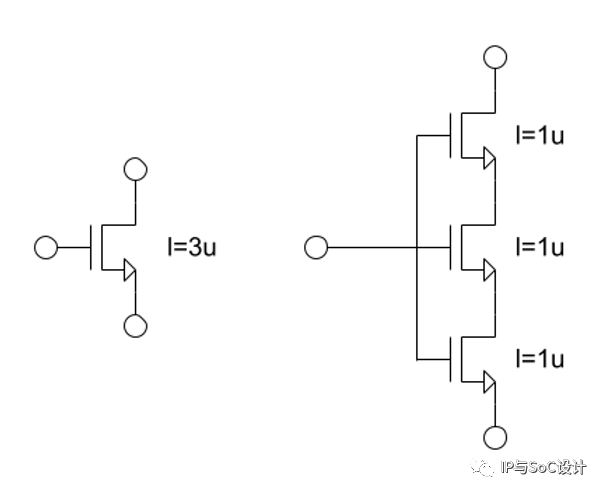

在28nm以下,最大器件长度限制意味着模拟设计者通常需要串联多个短长度MOSFET来创建长沟道器件。这些串联连接的器件通常被称为堆叠MOSFET或堆叠器件。例如,将三个1um MOSFET串联堆叠可产生沟道长度为3um的有效器件。

堆叠MOSFET在现代模拟设计中非常常见,但并非没有问题。主要问题是电容增加和面积增大。电容的增加很大程度上是由于器件周围互连的增加。总体栅极面积和栅极电容与非堆叠等效物保持相似,但在互连上存在额外的寄生电容。与单个长通道器件相比,堆叠中器件的物理分离增加了整体设计面积。

当在电路中使用堆叠的MOSFET时,布局质量变得比平时更加关键。糟糕的布局显著增加了寄生电容和设计面积,并可能导致电路不能满足所需的性能特性。布局工程师必须非常小心地设计此类设备的布局。在这些较小的流程节点上工作的大多数设计师都经历过布局前和布局后模拟非常不同的情况。通常,这是由于堆叠器件上的互连寄生效应造成的。

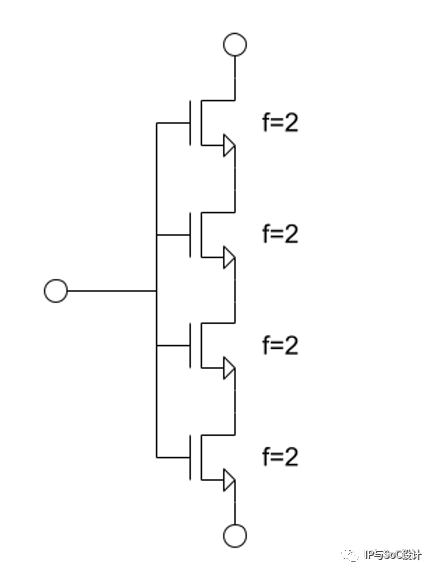

让我们来看看为堆叠MOSFET实现高质量布局的几种方法。下面的子电路显示了四个nmos MOSFET,它们堆叠在一起形成了一个长沟道器件。

在这个电路中,你可以看到所有的栅极引脚都连接在一起(所有四个体连接也是如此);你还可以看到MOSFET已经串联连接,其中一个的漏极连接到下一个的源极。因为在这种情况下,每个器件都是一个简单的单指MOSFET,所以在设计这种结构的布局时,我们可以使用简单的扩散共享布局模式。

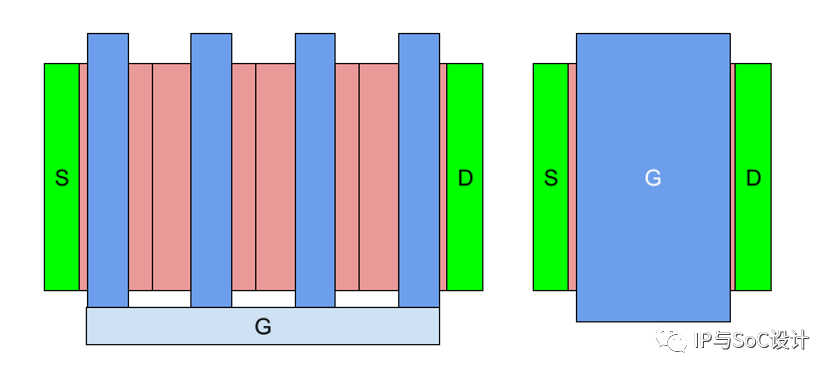

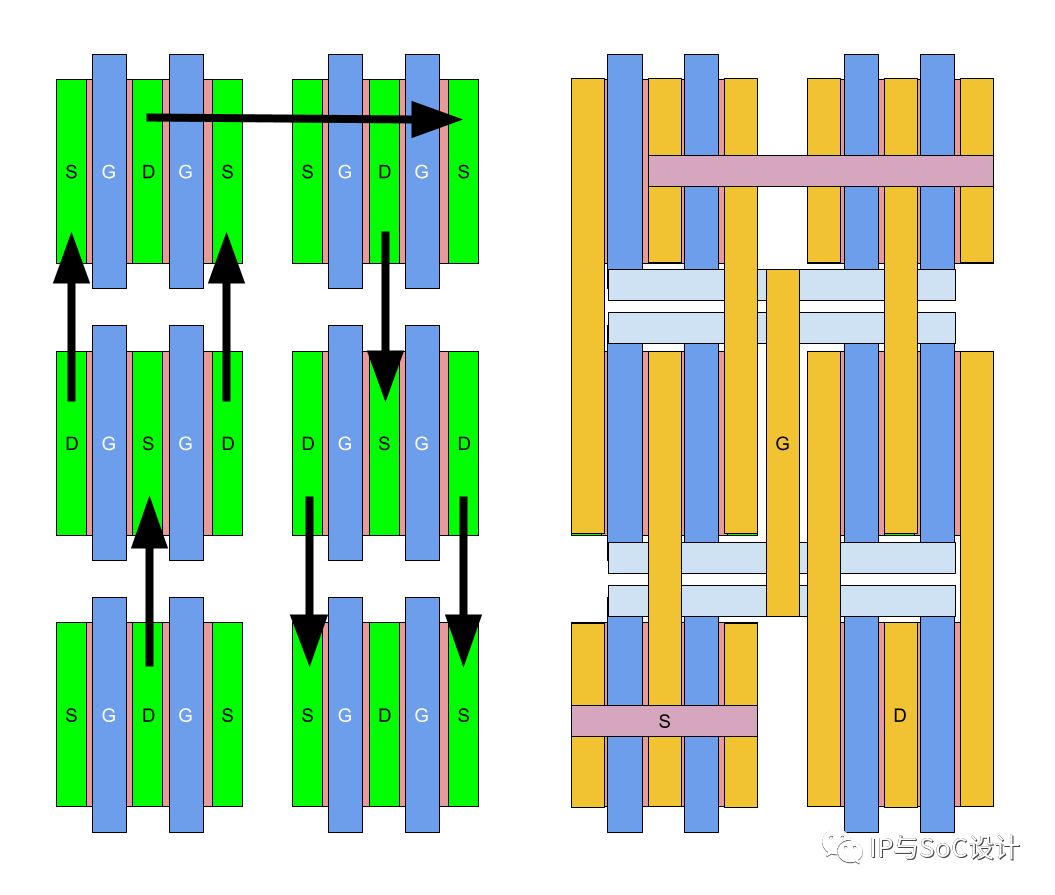

简单堆叠案例的布局如上图左侧所示;您可以看到,几乎没有额外的互连,因为等效的长沟道器件(右侧)也需要多晶接触。在这种情况下,面积惩罚是显著的,但这是不可避免的,并由poly-min间距规则决定。

这种方法的另一个问题是,非常长的有效器件可能导致长的扩散共享链。但是,可以将长链折叠成多行,如下所示。折衷的是,这增加了额外的互连,并进一步增加了堆叠器件的电容。

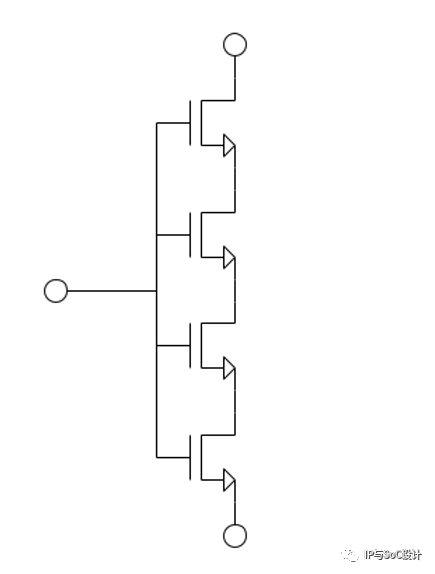

下面的电路显示了电路设计者想要在电路中使用两个指状MOSFET以实现更好匹配的情况。

两个手指设备不能通过扩散共享连接,因此我们必须使用不同的放置和路由方法。为了实现紧凑的布局,设备按列连接,而不是前面示例中所示的基于行的模式。

左边的图像显示了连接模式,一个器件的漏极垂直连接到下一个器件源极。正如你所看到的,连接是按列运行的,交替的器件具有不同的参数,可以在MOSFET的漏极中心和源极中心变体之间交换。交换的触点允许在列中的设备之间进行直线布线,避免了弯曲和额外的过孔。

您可以在右侧看到此基于列的模式的布线模式。存在额外的互连,但并不明显多于通常用于接触增强所需的互连。

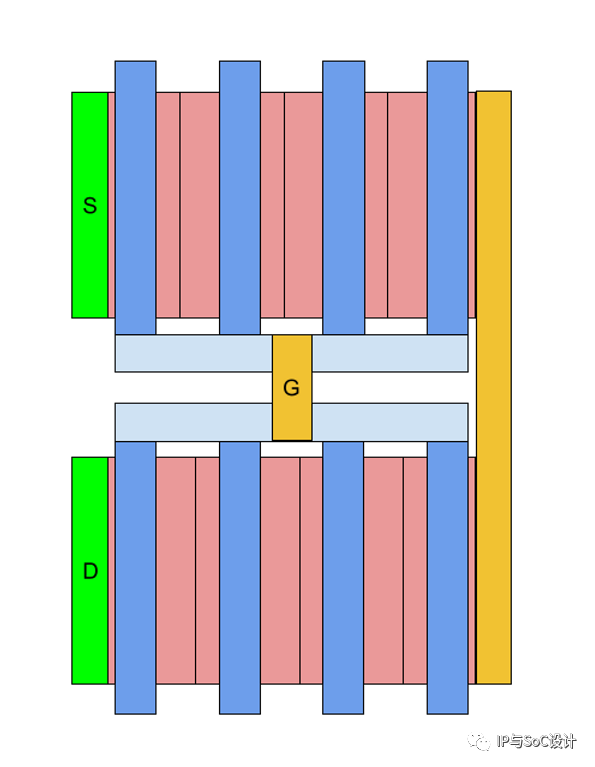

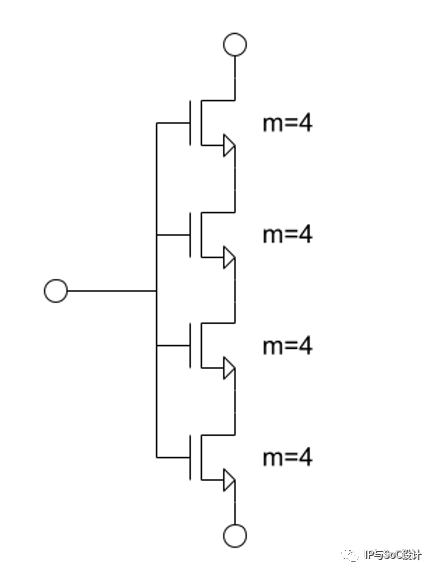

电路设计者还可以为堆叠的器件指定m因子。堆叠和m因子拓扑允许电路设计者使用许多小型MOSFET构建具有长沟道和宽沟道的器件。该示例示出了具有m因子4的单指堆叠器件。

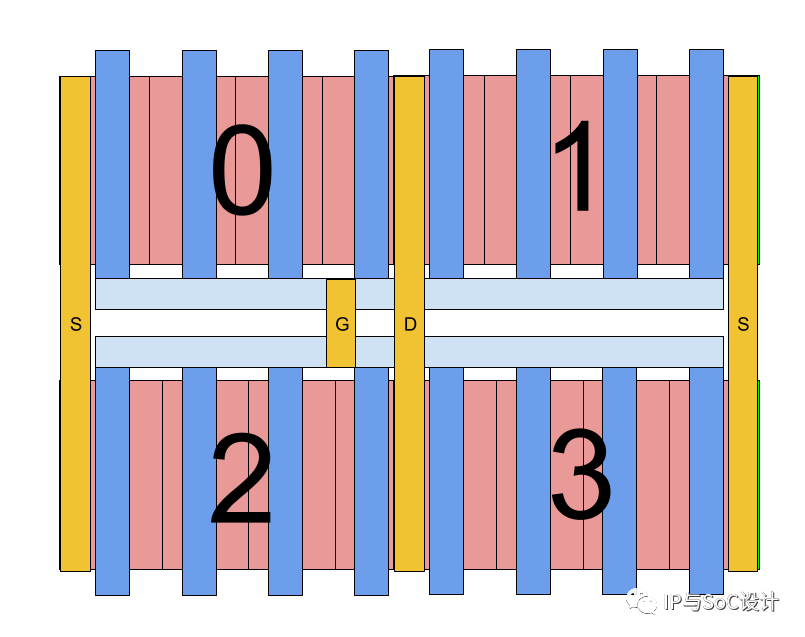

在下面的布局中,您可以看到该模式具有上一个基于行的模式的四个副本,这些副本的排列确保设备之间的额外路由量最小。

在本文中,我展示了一些可以与堆叠MOSFET一起使用的基本模式。在所有这些例子中,器件的放置和布线对于实现高质量布局至关重要。

Pulsic新的动画预览工具中的技术将放置和布线结合在一个操作中。这允许动画预览实现上面显示的堆叠设备的最佳布局模式类型。必须优化每个设备的确切位置、方向和参数化,以获得所需的结果。同时,该工具必须考虑通过每个设备的电流,以使互连复杂性和长度最小化。模拟布局总是需要仔细平衡多个相互竞争的优先级;没有一种做事方式在任何情况下都能奏效。

审核编辑:刘清

-

MOSFET

+关注

关注

147文章

7156浏览量

213132

原文标题:博文速递:Stacked MOSFETs in analog layout

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MOSFET和封装技术的进步使得TI能够成功应对挑战

驱动功率MOSFET,IBGT,SiC MOSFET的PCB布局需要考虑哪些因素?

CAD入门学习:CAD文字堆叠的样式

HarmonyOS Java UI 之 StackLayout 布局示例

转:HarmonyOS Java UI 之 StackLayout 布局示例

在模拟版图设计中堆叠MOSFET

什么是堆叠设计

关于模拟布局中MOSFET差分对寄生效应的平衡问题探讨

平衡MOSFET差分对中的模拟布局寄生效应

基于序列对和模拟退火算法的布局问题研究

浅谈PCB布局设计的层堆叠规划

采用高侧N-MOSFET的堆叠式BQ769x2设计注意事项

MOSFET并联在高功率设计中的应用

模拟布局中的堆叠MOSFET设计

模拟布局中的堆叠MOSFET设计

评论