栅氧化层的厚度挑战

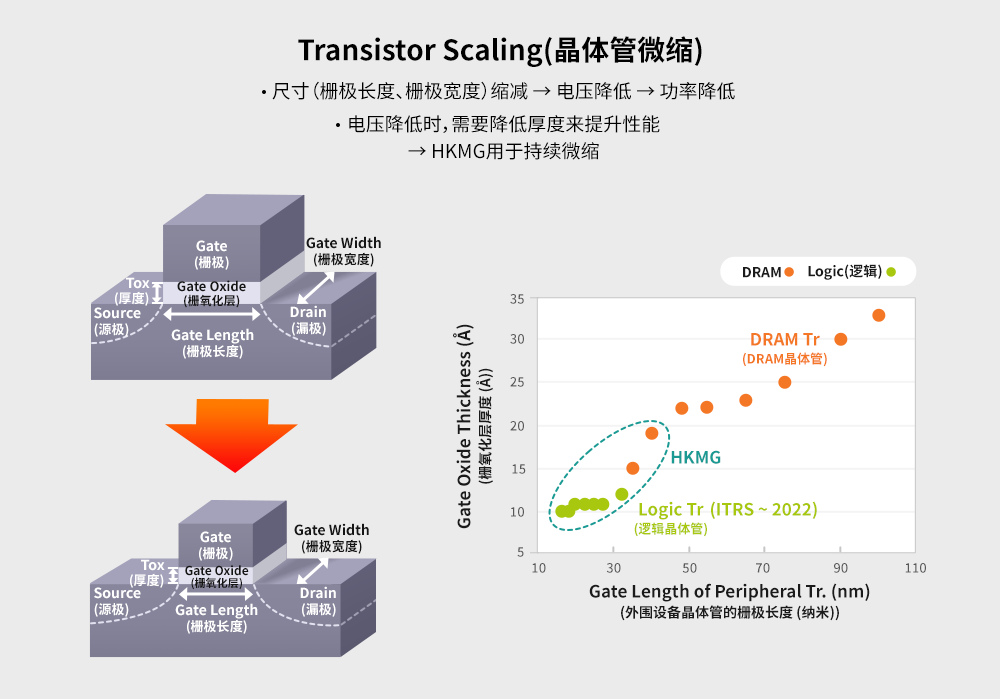

随着集成电路工艺技术不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,集成电路器件的特征尺寸不断按比例缩小,工作电压不断降低。为了有效抑制短沟道效应,除了源漏的结深不断降低和沟道的掺杂浓度也不断增加外,栅氧化层(Gate oxide)的厚度也在不断降低,从而提高栅电极电容,达到提高栅对沟道的控制能力,同时调节阈值电压。栅氧化层的厚度是随着栅极长度的减小而近似线性降低的,每一代大概是前一代的0.7倍左右,从而获得足够的栅控能力。另外,随着栅氧化层厚度的不断降低,MOS管的驱动能力也会相应提高。

▲图1. 晶体管微缩

当集成电路器件的特征尺寸进入0.18μm时,栅氧化层的厚度小于3nm,半导体业界利用氮氧化硅(SiON)代替纯二氧化硅(SiO2)作为栅氧化层的介质层材料。SiON具有三方面的优点:一是SiON具有较高的介电常数,在相同等效栅电容的情况下,SiON会具有更厚的物理氧化层;二是SiON具有较高的电子绝缘特性,在相同物理厚度的情况下,利用SiON作为栅氧化层的栅极漏电流大大降低;三是SiON中的氮元素对多晶硅栅极(Poly-Si Gate)掺杂的硼离子具有较好的阻挡作用,SiON可以防止硼离子在热退火处理的过程中扩散并穿越过栅氧化层到达衬底的沟道中影响器件的阈值电压。

早期生长栅氧化层SiON材料主要是利用炉管预先淀积一层纯二氧化硅薄膜,然后再利用原位和非原位热处理氮化SiO2薄膜形成SiON薄膜,氮化用气体是N2O、NO和NH3中的一种或几种。这种工艺技术简单,缺点是掺杂氮元素的含量太少,对硼离子的阻挡作用有限,并且SiON中的氮元素不是均匀分布在栅氧化层中,它主要分布在靠近SiO2和Si衬底的界面,造成SiO2和Si衬底之间的界面缺陷,会导致沟道的载流子散射,降低载流子的迁移率。用炉管热处理氮化得到的SiON主要应用于特征尺寸在0.11μm及以上的工艺技术。

高k栅介质层

随着器件尺寸不断缩小,栅极介质层SiON的厚度会降低到2nm以下,栅极多晶硅耗尽,衬底量子效应和栅极漏电流变得越来越严重。而栅极漏电流对集成电路的影响尤为重要,它会严重影响集成电路的功耗和可靠性。选用高k材料(High-k material)代替SiON作为栅介质层,可以在相同等效栅氧化层厚度的情况下,得到物理厚度更大的栅介质层,从而改善栅极漏电流。

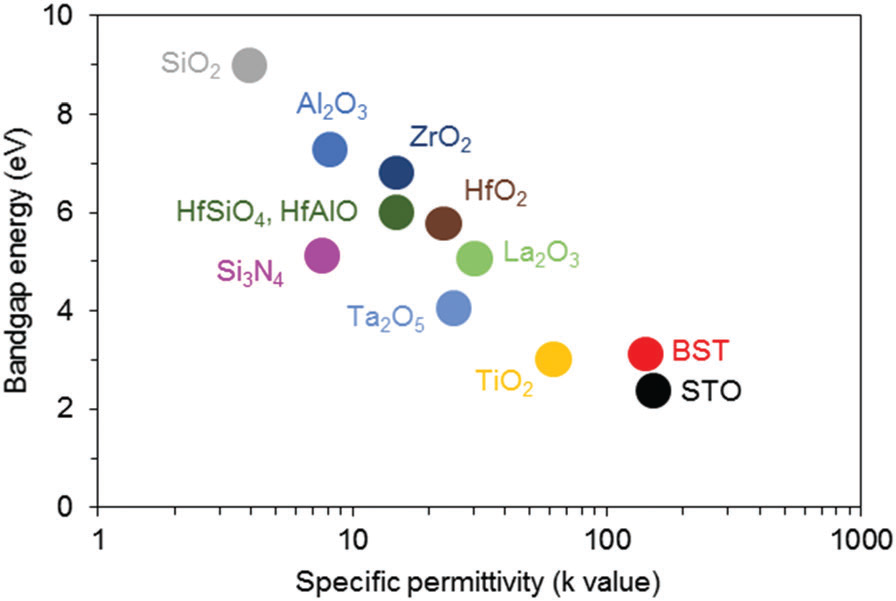

▲图2.材料禁带宽度与介电常数

长期以来,研究人员在高k材料领域进行了大量的基础研究,发现了很多高k材料。例如从早期的Si3N4,Al2O3到后期的Ta2O5、TiO2、La2O3和HfO2等。但是这些高k材料都不能很好地与目前的工艺兼容,它们只能满足工艺的某一方面的特定要求。

Si3N4与Si的晶格匹配得很好,Si3N4自身以及与硅衬底形成的界面具有良好的热稳定性,并且Si3N4中氮元素的存在可以有效地阻挡p-MOS栅极硼杂质向衬底扩散,但是Si3N4会引起载流子迁移率下降且介电常数较低(均值在7左右)。它无法满足先进CMOS工艺栅介质层厚度逐渐缩小的要求。

Al2O3的禁带宽度为8.9eV,其热力学稳定性非常好,结晶温度高,并且能与Si衬底形成良好的界面,但是它的相对介电常数也较低,仅为9左右。它也无法满足先进CMOS工艺栅介质层厚度逐渐缩小的要求。

TiO2的介电常数高达80,但是其禁带宽度仅为3.5eV,并且结晶温度较低,只有400℃,在后续高温退火处理时产生结晶化,并将引起栅极漏电流显著增大且TiO2与硅衬底及多晶硅栅极之间存在界面反应问题。所以它与硅工艺存在不兼容问题。

Ta2O3的介电常数约在25左右,但其结晶温度只有700℃且禁带宽度很小,Ta2O3与Si的导带偏移量只有0.38eV,如此低的势垒高度,载流子很容易越过势垒形成栅极漏电流。另外,Ta2O3在Si上的热稳定性极差,在界面处易生成SiO2/硅酸盐,导致界面存在大量缺陷,这些缺陷电荷中心会造成载流子散射,严重影响了反型层中载流子的迁移率。所以它也不适用于CMOS工艺制程栅介质层。

HfO2的介电常数25左右,其禁带宽度为5.9eV,并且HfO2与Si的导带偏移量1.5eV,载流子不足以越过1.5eV的势垒高度形成栅极漏电流。HfO2与Si直接接触会显著降低载流子迁移率,其结晶温度低于600℃,不过可以对HfO2掺杂Si,N等可以使其结晶温度提高到1000℃,但是对HfO2掺杂后形成的HfSiO或者HfSiON的介电常数会降低,HfSiO4的介电常数比较低,只有7~15,而HfSiON的介电常数会随着N元素的含量变化而增大,最高可达16。对HfO2掺杂N离子可以提高结晶温度,减小栅极漏电流,抑制硼穿通效应。对HfO2掺杂Si离子可以改善界面态,提高载流子迁移率。

通过改变工艺流程和利用金属栅极可以使HfO2与目前的硅工艺兼容。另外,通过对栅极嵌入金属材料也可以使HfSiON与目前的硅工艺兼容。所以目前HfO2和HfSiON是最适合用作高k栅介质层材料。

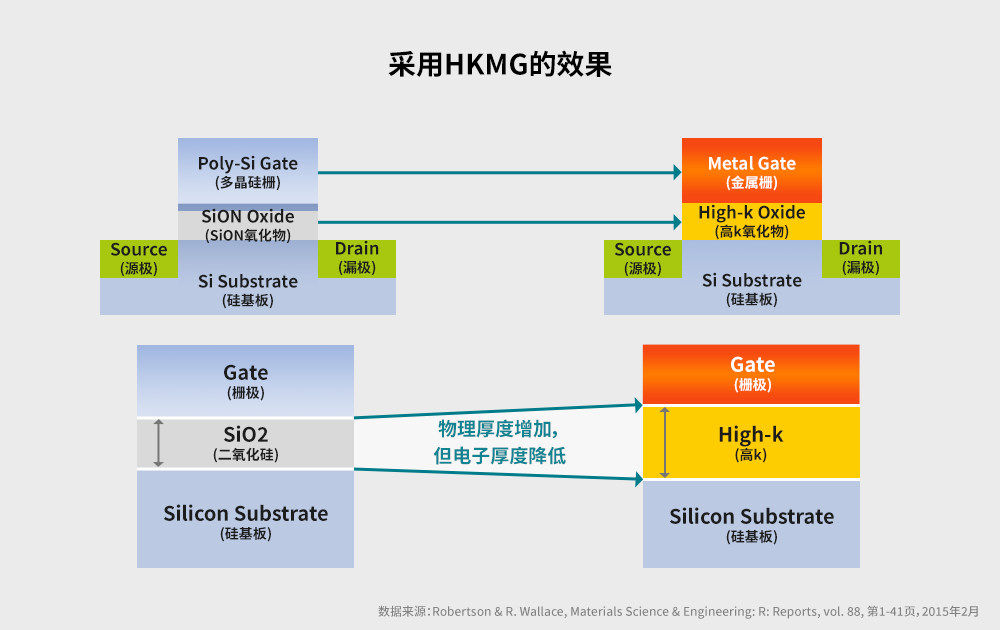

HKMG:微缩与性能的突破

随着器件尺寸不断缩小到45nm及以下工艺技术,栅极介质层SiON的厚度降低到2nm以下,为了改善栅极漏电流,半导体业界利用高k材料HfO2和HfSiON取代SiON作为栅氧化层。HfO2和HfSiON介质材料有两方面的优点:一是HfO2和HfSiON介质材料具有很高的电子绝缘性;二是HfO2和HfSiON介质材料的介电常数是15~25,而SiON的介电常数在4~7之间,在相同的等效氧化层厚度(EOT)条件下,HfO2和HfSiON介质材料的物理厚度是SiON的3~6倍多,这将显著减小栅介质层的量子隧穿效应,从而有效的改善栅极漏电流及其引起的功耗。

▲图3.采用HKMG的效果

但是利用HfO2和HfSiON介质材料代替SiON也会引起很多问题,例如由于HfO2和HfSiON介质材料与衬底之间会形成粗糙的界面,并存在缺陷中心,缺陷中心会造成载流子散射,导致载流子迁移率降低。HfO2和HfSiON介质材料中的Hf原子会与多晶硅的硅原子发生化学反应形成Hf-Si键,从而形成缺陷中心,导致无法通过离子掺杂来改变多晶硅的功函数,造成费米能级钉扎效应(Femi Level Pinning Effect),该效应会造成器件的阈值电压发生漂移,并且无法通过多晶硅栅的离子掺杂来调节器件的阈值电压。另外,高k材料的高介电常数值得益于内部偶极子结构,但是在栅介质层下表面附件的偶极子会发生振动并传递到沟道的硅原子,造成晶格振动,形成载流子声子散射,也会导致器件沟道中载流子的迁移率降低,从而降低器件的速度。

由于多晶硅栅与HfO2和HfSiON介质材料结合会产生许多问题,为了解决这些不兼容问题,半导体业界利用金属代替多晶硅作为器件栅极(Gate electrode)材料,利用金属栅代替多晶硅栅可以改善费米能级钉扎效应,同时金属栅极具有极高的电子密度,可以有效解决多晶硅栅极耗尽问题。另外,在高k材料与衬底之间的界面插入一层极薄的SiON薄膜,利用SiON薄膜作为过渡层可以得到理想的SiON与Si的界面,这样可以有效改善高k材料与衬底之间的界面,也可以改善偶极子的振动对载流子迁移率的影响。SiON薄膜是利用Si的高温热氧化技术形成的。利用高k材料代替常规栅氧化层SiON和金属栅代替多晶硅栅的工艺称为HKMG工艺技术,HK是High-k的缩写,MG是Metal Gate的缩写,也就是金属栅。

虽然HKMG利用金属栅极和高k栅介质层解决了多晶硅耗尽问题和栅极漏电问题,但是它也在硅衬底和高k栅介质层引入了SiON界面层。SiON的介电常数比较低,引入的SiON界面层物理厚度在0.6nm左右,所以SiON界面层的削弱了高k栅介质层对先进工艺中栅极电容的贡献。由于目前在技术上没有办法实现移除SiON界面层,SiON界面层的问题将一直存在,未来工艺方向是仅仅只通过提高工艺技术把SiON界面层的物理厚度从0.6nm降低到0.3nm左右。另外,衬底量子化效应的问题也会一直存在,在技术上也没办法改善它,只能在新材料的方向上继续努力。

文章来自:微信公众号“ICPMS冷知识”

审核编辑:汤梓红

-

集成电路

+关注

关注

5387文章

11530浏览量

361612 -

半导体

+关注

关注

334文章

27286浏览量

218037 -

MOS管

+关注

关注

108文章

2410浏览量

66755 -

晶体管

+关注

关注

77文章

9682浏览量

138073

原文标题:高k金属栅(HKMG)工艺

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

GLOBALFOUNDRIES德累斯顿工厂出货第25万枚32纳米HKMG晶圆

深入赛灵思Kintex-7 FPGA内部:透视HKMG技术

高介电常数栅电介质/金属栅极的FA CMP技术

IMEC发布后栅极HKMG制式细节,英特尔、三星受益

专访格罗方德Subramani Kengeri:28nm量产致胜关键在于HKMG

基于主流的体硅高κ/金属栅FinFET工艺,提出了一种利用拐角效应

高k金属栅(HKMG)工艺详解

高k金属栅(HKMG)工艺详解

评论