先给大家出一个题目:当x为5时,y=x << 6 + x <<3 + x << 2 + x的结果为多少,即y的值是多少?

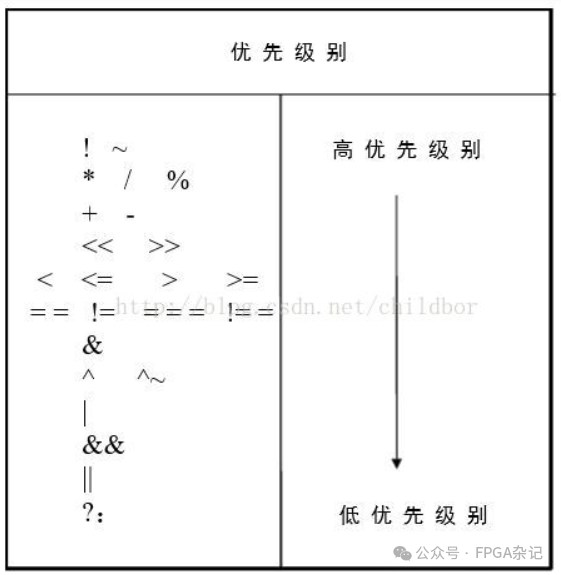

我先不给出答案,先贴上正确的运算符优先级顺序,如下图所示:

俗话说温故而知新,今天回顾一下verilog的运算符的优先级。

说一下回顾这个原因:今天打算用verilog实现一个乘法器,即:y=77*x。为了加快运算时间,将77转换为二级制(1001101),然后使用了移位寄存器来实现乘法运算,具体代码如下:y=x << 6 + x <<3 + x << 2 + x。但是仿真结果不对,仿真结果为0的概率比较大。之前还以为是x的位宽太小导致的,但是修改位宽之后还是不行,所以又重新审视了一下这段代码,怀疑是运行操作符的优先级有问题导致的,查阅书籍发现确实是这样的:加法的优先级高于左移运算,导致先进行加法运算再进行移位运算,所以结果和预期不一致。

实际上,要实现y=77*x运算,正确的verilog代码如下:y=(x << 6)+(x <<3)+(x << 2)+ x。

所以说,刚开始给出题目的答案不是我不给出,实际上按照正确优先级计算的结果没有太多的意义。

审核编辑:汤梓红

-

Verilog

+关注

关注

28文章

1351浏览量

110073 -

乘法器

+关注

关注

8文章

205浏览量

37039 -

运算符

+关注

关注

0文章

172浏览量

11078

原文标题:考题

文章出处:【微信号:FPGA杂记,微信公众号:FPGA杂记】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

verilog运算符的优先级

verilog运算符的优先级

评论