首先需要指出本文题目所指的仿真指的是功能仿真,即不带时序信息的仿真。

每个FPGA developer都会做功能仿真验证RTL代码功能的正确性。我们知道在功能仿真中是没有考虑延迟的,组合逻辑是零延迟,寄存器也是在时钟跳变沿瞬时完成采样。

对于同步电路来说,功能仿真完成后,再加上静态时序分析,我们基本能确保设计的电路能正确工作(有一些情况例外,比如综合的结果和仿真的结果不同)。但是对于异步电路,功能仿真的零延迟特性没法很好vwin 跨时钟域时的情况,在静态时序分析时我们一般也是false path,不做后仿真(时序仿真)则很难确保跨时钟域电路设计的正确性。

那么我们在做仿真时有没有办法更好得模拟跨时钟域的情况?

先看看跨时钟域有什么特性?一是亚稳态导致采样到的信号出现随机值,二是跨时钟域不是瞬时结束的,而是会持续一段时间。

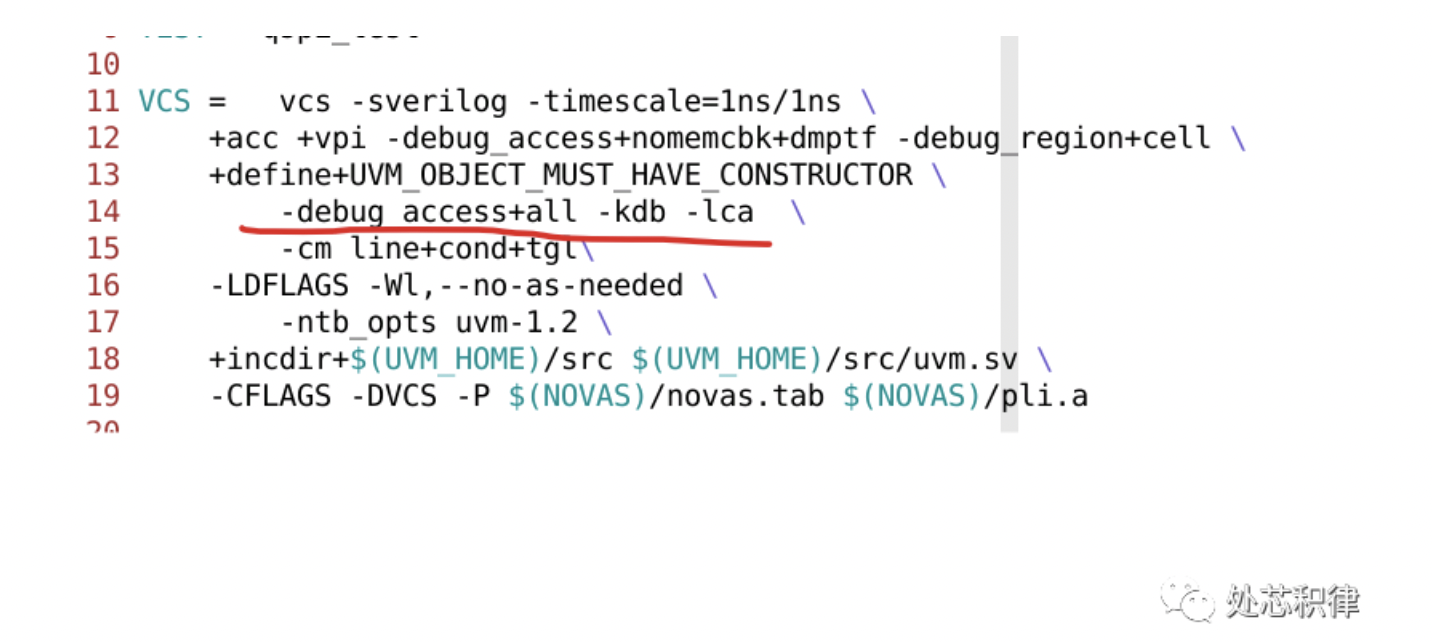

依据此特性,我们在功能仿真时可以手动给跨时钟域信号加延迟。延迟的大小可以是random的一个值来更好得模拟随机采样值,而且最好是能在真实延迟的大概范围。

举个例子。

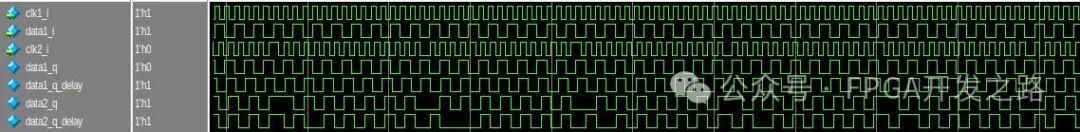

假设我们是跨时钟域采样一个bit的信号,输入信号不停在0和1之间跳变。如下图所示,data1_q是输入单bit信号的寄存器输出,data1_q_delay则是对data1_q添加延迟后的信号。data2_q是在目的时钟域clk2对data1_q的采样,data2_q_delay则是在目的时钟域对data1_q_delay的采样。

从图中可以看到,data2_q在跨时钟域时只有一个cycle采到错误的值,data2_q_delay则较好的模拟出了采样值的随机性,而且会持续多个cycle出现“随机”值。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5336浏览量

120229 -

静态时序分析

+关注

关注

0文章

28浏览量

9586 -

时钟信号

+关注

关注

4文章

448浏览量

28542

原文标题:跨时钟域如何仿真?

文章出处:【微信号:FPGA开发之路,微信公众号:FPGA开发之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IGBT驱动波形负压关断时有上升尖峰,请问有没有办法可以抑制?

gpio0有没有办法切换复位以防止获取时钟输出?

有没有办法模拟FET的大信号时域

TCL有没有办法在没有重新运行模拟的情况下获得HDL对象的值?

有没有办法在不清洁ZMK的情况下更换新电池?

AT+HTTPCLIENT有没有办法打断命令?

如何利用FPGA设计一个跨时钟域的同步策略?

有没有办法像debug RTL代码一样将UVM中变量拉到波形上看呢?

跨时钟域电路设计:单位宽信号如何跨时钟域

在做仿真时有没有办法更好得模拟跨时钟域的情况?

在做仿真时有没有办法更好得模拟跨时钟域的情况?

评论