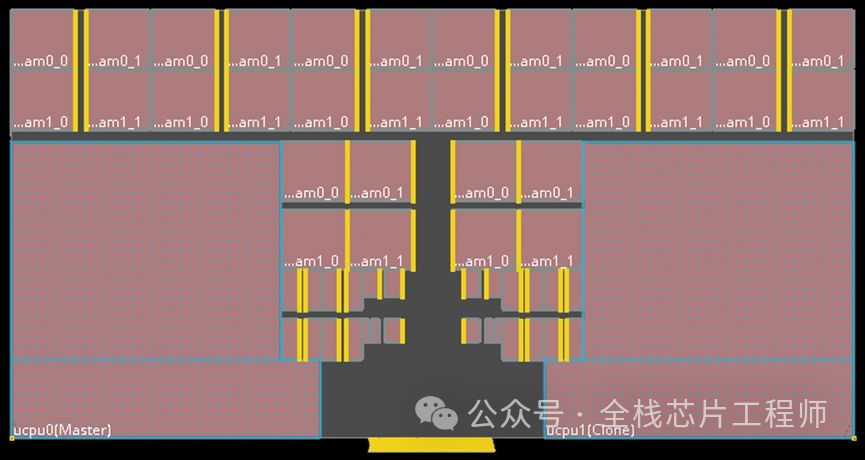

下面Cortex-A72培训营VIP学员问:单核CPU PR做完后,怎么输出数据到TOP去做多核的hierarchy集成?

答:单核CPU做好后,需要输出SDC、DEF、LEF、GDS、Netlist、LIB等库文件,然后做TOP的hierarchy设计。

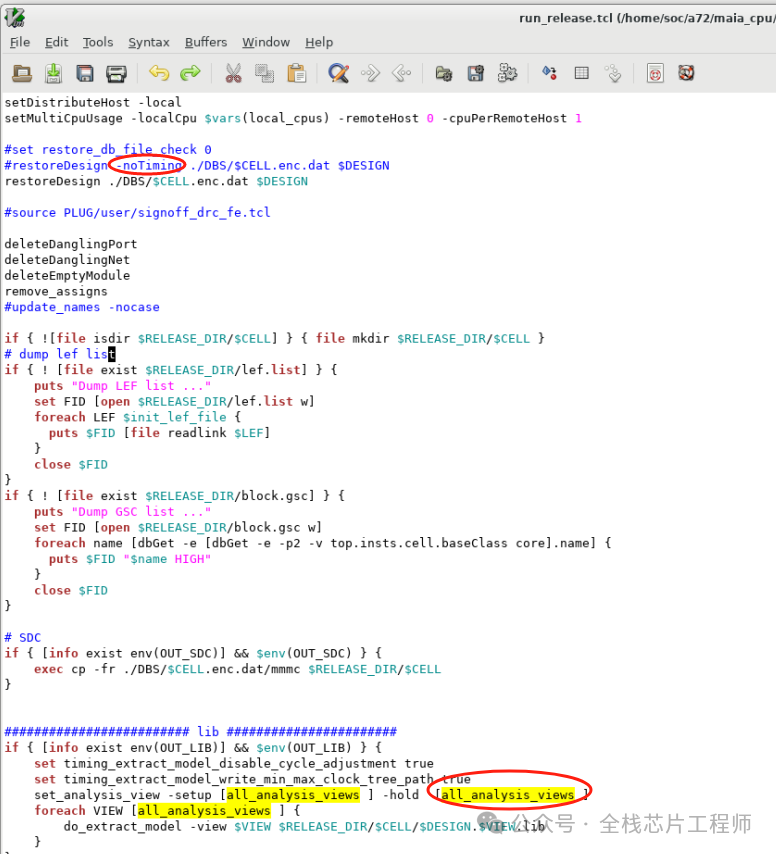

比如抽取lib命令如下:

do_extract_model -view $VIEW ./$DESIGN.$VIEW.lib

其他命令请参考服务器脚本!

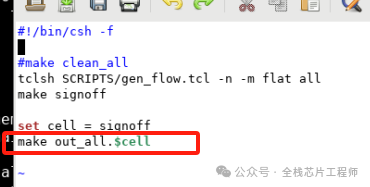

Cortex-A72培训营VIP学员问:我想让invs出lib,但是release的时候。view全被remove了。不清楚怎么回事?

答:analysis_view是空的原因是-noTiming造成的,如下图:

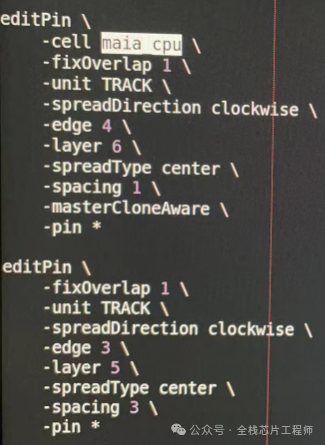

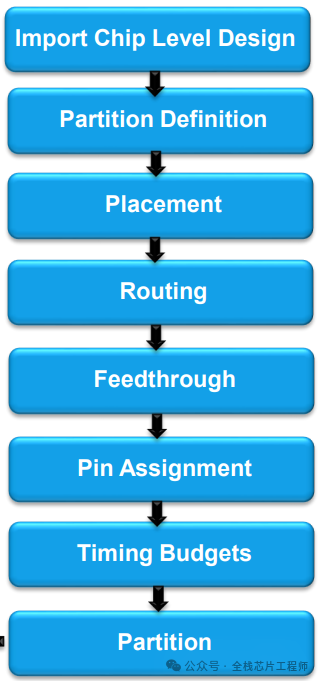

Cortex-A72培训营VIP学员问:partition时,pin在哪个步骤assign的?

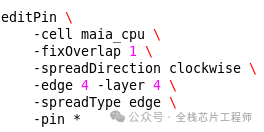

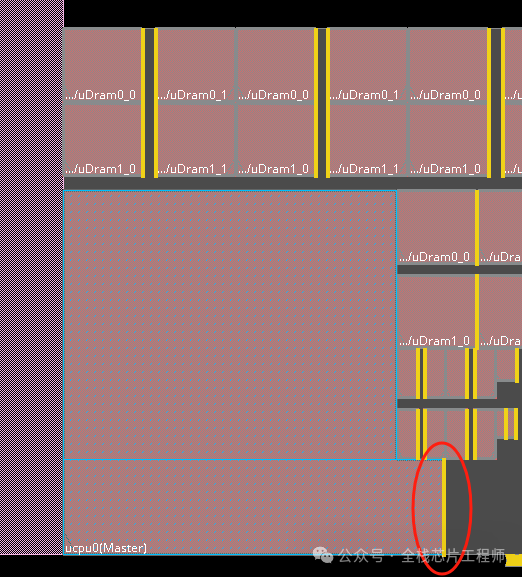

答:partition时候加如下脚本即可editPin:

比如:

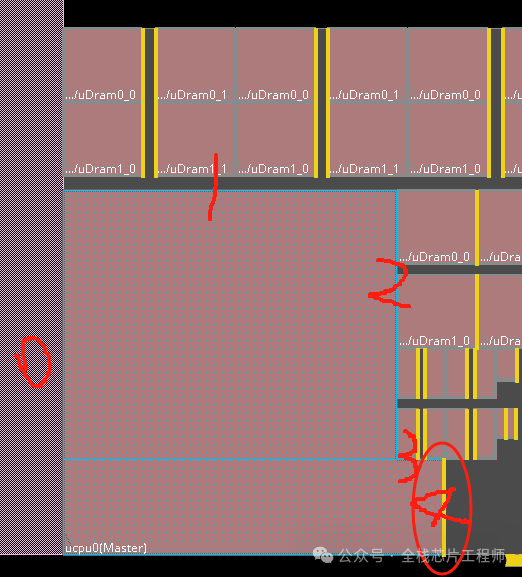

clockwise是pin的顺序

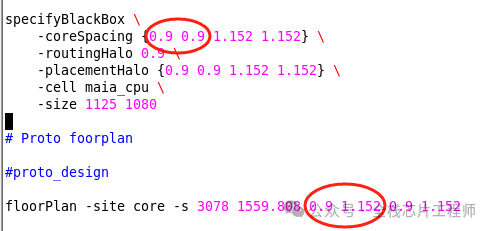

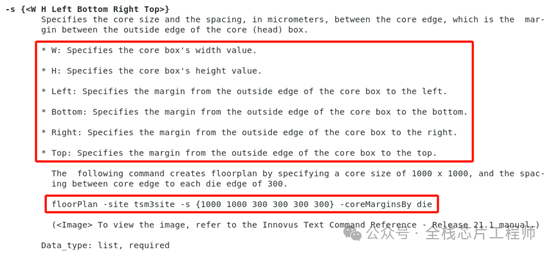

Cortex-A72培训营VIP学员问:下面坐标写错了?

答:floorplan时的格式如下图,左下右上,但是specifyBlackBox的-coreSpacing顺序是左右上下!

Cortex-A72培训营VIP学员问:0.9 1.152是基于什么考虑来确定的数值啊?

答:1.152 是上下两个site的高度,0.9应该也是左右site的宽度倍数 或者met pitch倍数。

“12nm工艺,2.5GHz频率,Cortex-A72处理器中后端实战培训”

01 —Cortex-A72处理器—数字后端实战

本项目是真实项目实战培训,低功耗UPF设计,后端参数如下:

工艺:12nm

频率:2.5GHz

资源:2000_0000instances

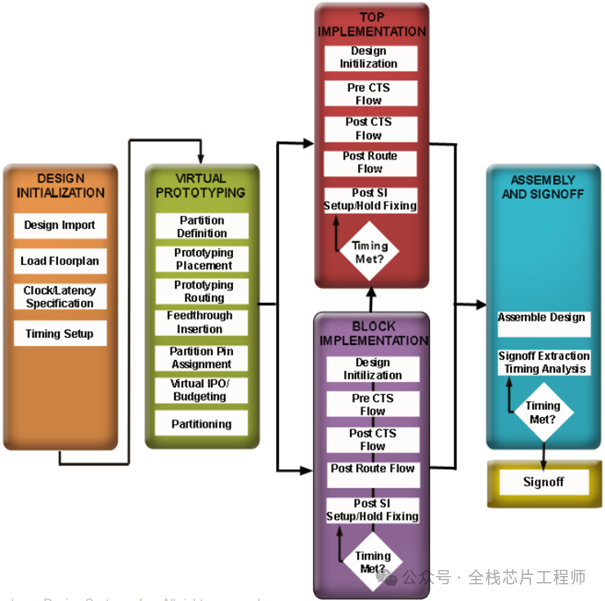

Flow:PartitionFlow

Partition步骤:

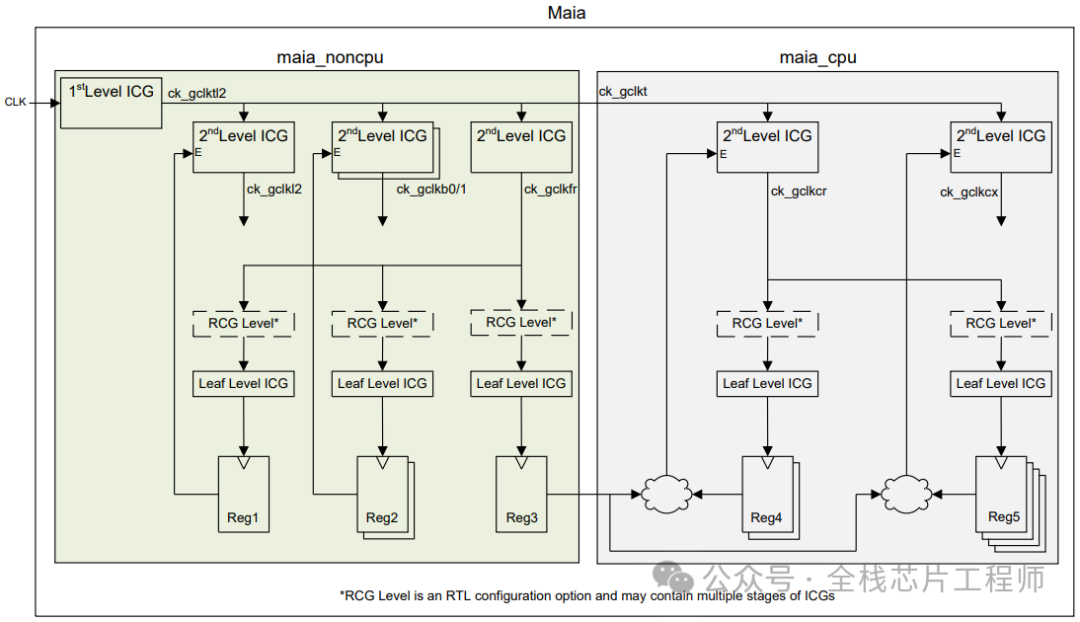

时钟结构分析:

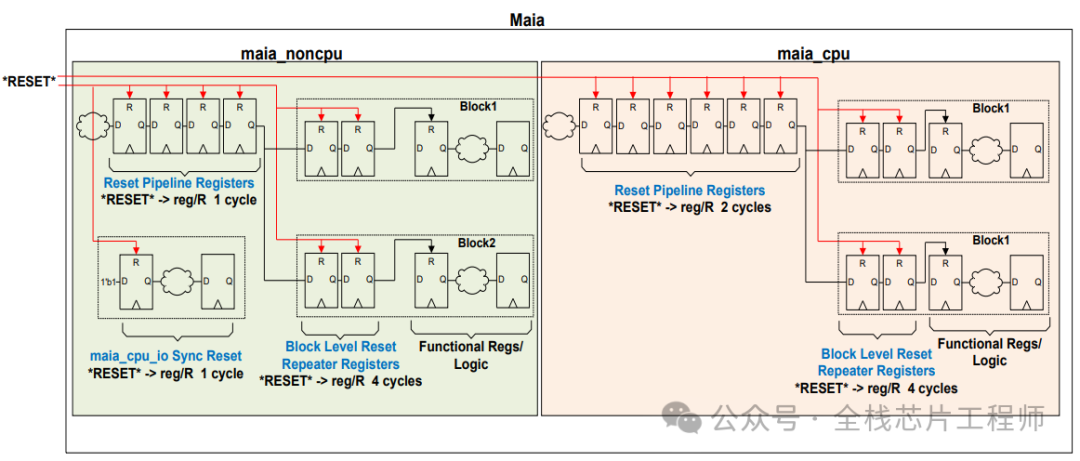

复位结构分析:

我们来对比下A72与A7的资源。A72Gate数目是A7的13倍!如果都采用28nm制程,A72的面积应该是1180790um^2,实际A72采用12nm制程面积是486100um^2,1180790/486100=2.4,符合摩尔定律。

Cortex-A7单核:

Gates=240291Cells=118421

Cortex-A72单核:

Gates=3125649Cells=1207766

28nmCortex-A7单核:

Area=90830.1um^2

12nmCortex-A72单核:

Area=486100.9um^2

审核编辑:汤梓红

-

cpu

+关注

关注

68文章

10854浏览量

211563 -

命令

+关注

关注

5文章

683浏览量

22011 -

脚本

+关注

关注

1文章

389浏览量

14858

原文标题:12nm工艺,2.5GHz频率,Cortex-A72实战

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ARM最新Cortex-A72架构剑指PC,英特尔麻烦了?

ARM Cortex-A72性能狂飙:要超越Intel的节奏?

如何利用64位的RK3399去实现裸机的启动与中断呢

ARM Cortex-A72 MPCore处理器加密扩展技术参考手册

将GICv2中断控制器与ARM Cortex-A5x和Cortex-A72处理器集成

ARM Cortex®-A72 MPCore处理器技术参考手册

Cortex-A72 MPCore软件开发人员勘误表

联发科MT8173芯片详解:两个Cortex-A53核心和两个Cortex-A72

fireflyEC-A3399C主控芯片介绍

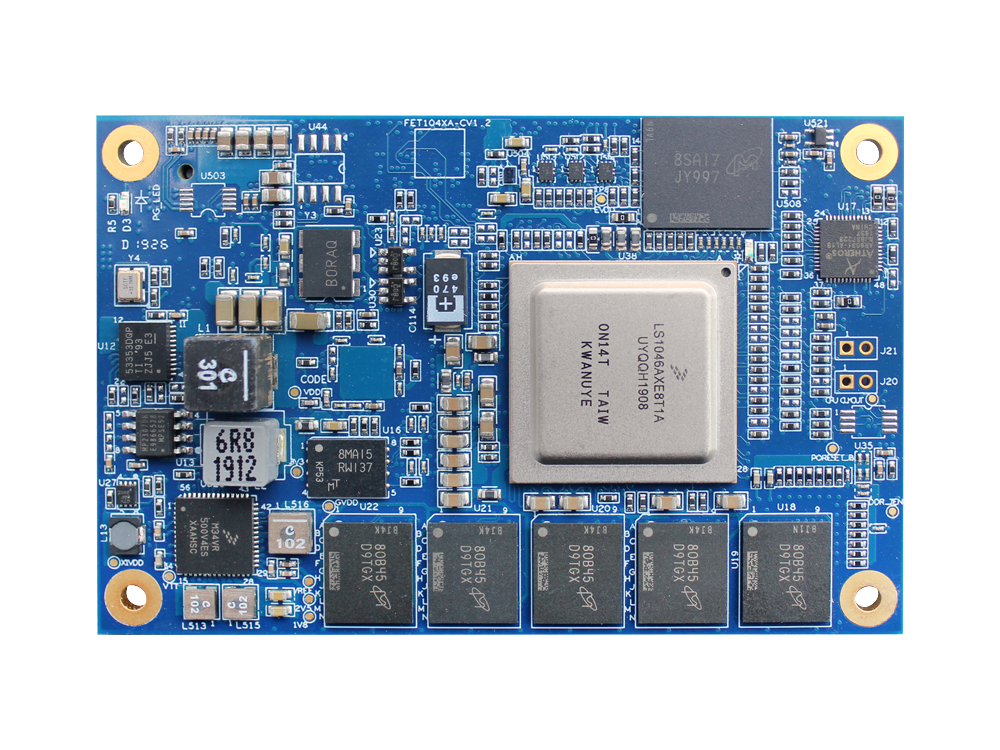

飞凌嵌入式FET1046A-C核心板简介

Versal ACAP,APU - 当有逐出传输事务处于暂挂状态时,外部数据嗅探可能导致数据损坏

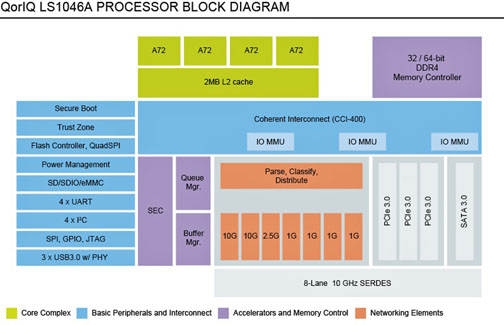

基于四核Cortex-A72的CPU QorIQ LS1046A 64 位处理器

Cortex-A72核心板 | RK3399六核

特斯拉fsd芯片技术怎么样 第一代FSD的NPU部分拓扑图解析

Cortex-A72应用实战

Cortex-A72应用实战

评论