简介

在 FPGA 上实现了 JPEG 压缩和 UDP 以太网传输。从摄像机的输入中获取单个灰度帧,使用 JPEG 标准对其进行压缩,然后通过UDP以太网将其传输到另一个设备(例如计算机),所有这些使用FPGA(Verilog)实现。

本文是常春藤盟校Cornell University 康奈尔大学的FPGA项目,仅供参考学习~

理论背景

JPEG 图像压缩是一种有损压缩标准,它使用 DCT 变换及其相关属性来减少用于表示图像的位数。编码过程涉及许多步骤,在我们的设计中将其分解为几个独立模块。此外,为了验证压缩的正确性,还为系统设计了UDP以太网传输。

离散余弦变换

离散余弦变换 (Discrete Cosine Transform, DCT)类似于傅里叶变换将周期函数表示为不同频率的正弦之和,其可以将有限长度的数字序列表示为不同频率的余弦项的总和。DCT,更具体地说是DCT-II,由于其高能量压缩特性而被用于图像压缩。简而言之,大部分数据(或原始信息)可以被压缩为更少的比特数。

JPEG 压缩的第一步是将相关图像分割成 8x8 的像素块。然后将 2D-DCT 应用于每个 8x8 块。2-D DCT 的结果表示原始块在与矩阵索引相对应的离散频率处的空间频率信息。变换后,左上系数给出空间DC信息,右下系数给出最高空间频率(水平和垂直方向)信息。

注意,左上元素在水平和垂直方向上的空间频率较低,而右下元素的频率较高。使用 DCT,大多数原始信息可以从较低频率系数(靠近左上角的系数)重建,因为这些系数中的高能量压缩。此外,人类视觉系统对高频空间内容中的错误的感知能力较差。这两个原因叠加在一起意味着低频系数中的误差比高频元素中的误差对人类来说更加明显。

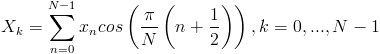

2-D DCT 运算是可分离的,意味着它可以通过对正在分析的块(8x8)应用两次 1-D DCT 来获得。首先对块的每一行执行一维变换,然后对行变换结果的列再执行一维变换。一维 DCT 系数可以使用以下等式获得:

其中 k 是系数的索引。对于 JPEG 变换的情况,因为变换应用于图像的 8x8 像素块,所以 N 始终等于 8。

量化

DCT 应用于 8x8 块时,量化因子会应用于系数。简而言之,此步骤使用与能量密度相关的步长对系数进行离散化。低频系数以较小的步长量化,因此比以较大步长量化的误差更小。频率越高,步长越大,从而降低了不太重要元素的精度。这是压缩过程中的有损步骤。

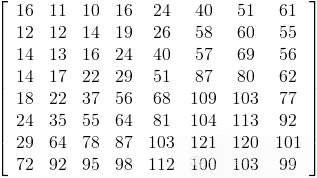

尽管 JPEG 压缩标准没有指定要使用的量化矩阵,但上面建议的矩阵之一。为了量化 2-D DCT 的结果,每个系数除以上面矩阵中的适当值,并四舍五入到最接近的整数。

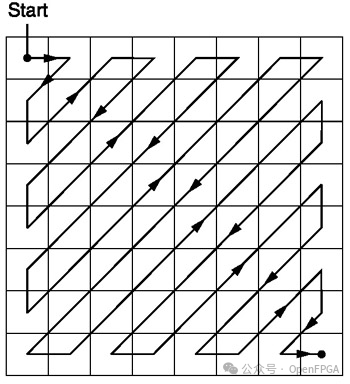

Zig-Zag 测序

量化后,二维矩阵被重新排列成一维数组。以给出具有高能量密度的系数的方式读取元素。排序以之字形方法完成,使得系数以递增的空间频率顺序排列。使用这种方法,更重要的系数出现在序列中较早的位置,而不太重要的系数则出现在较晚的位置。

可变大小、行程长度编码

假设高频系数使用较大的步长进行量化,这些系数为零的可能性比低频系数高得多。这对零值系数的候选进行了分组,使我们能够假设一系列零的可能性。

JPEG 标准压缩的主要来源是可变大小和行程长度编码。压缩中的此步骤使用霍夫曼编码和可变长度编码的组合。每个非零系数都被转换为可变长度的位串或代码。该代码包含其数量和长度信息(即 0 与 00 不同)。

如前所述,之字形组织增加了连续零的可能性,尤其是在数组末尾附近。为了避免发送连续的零,前面的零的行程长度被编码到每个非零系数的转换中。每个非零系数都被编码为可变长度代码,以及指示前面的零游程的“标头”霍夫曼代码以及 VL 代码的长度。链接(https://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/f2009/jl589_jbw48/jl589_jbw48/trans_tables.html)显示了像素转换表和霍夫曼表 。这些转换表仅适用于图像的亮度值。由于我们的系统处理灰度图像,所以无需改变方案,但是对于彩色图像使用的色度值有不同的转换方案。

无论长度如何,霍夫曼码都是唯一可识别的,因此在不知道长度的情况下始终可以识别新非零值的零行程和大小。然后,使用霍夫曼给出的大小,可以提取以下 VL 位并将其转换回适当的非零系数。除非事先知道代码的长度,否则 VL 代码无法唯一识别。

DC与AC系数

DC 系数的编码与 AC 系数略有不同。由于 DC 系数不会有前面的零(这些零不会在块之间传递),因此霍夫曼码仅反映 VL 码的长度。

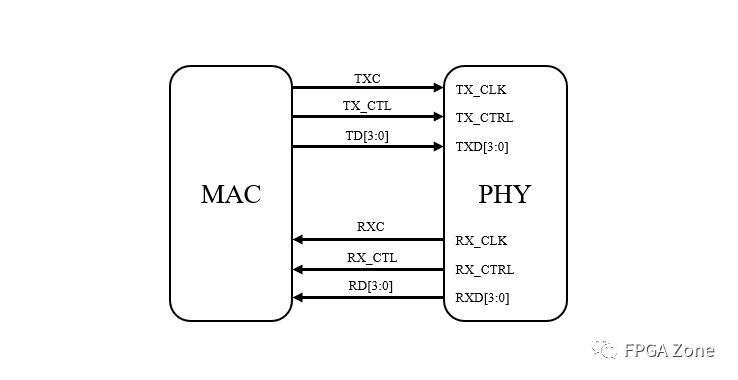

以太网

在开放系统互连参考模型(Open System Interconnection Reference Model,OSI 模型)中,以太网位于链路层和物理层。在物理层,以太网描述了线路如何互连。在链路层,以太网指定以太网帧应如何格式化以及帧应如何传送。

由于以太网本质上是一种广播协议,可能有许多设备连接到同一物理线路,因此一次只能有一个设备进行广播。如果线路发生冲突,以太网控制器能够检测到冲突并执行随机退避。随机退避仅仅意味着在检测到冲突时,在尝试另一次发送之前等待随机的时间。以太网帧由前导码、帧起始定界符、MAC 目标、MAC 源、以太网类型、有效负载和校验和组成。

关于以太网的介绍可以查看《基于FPGA的网口通信实例设计总结》。

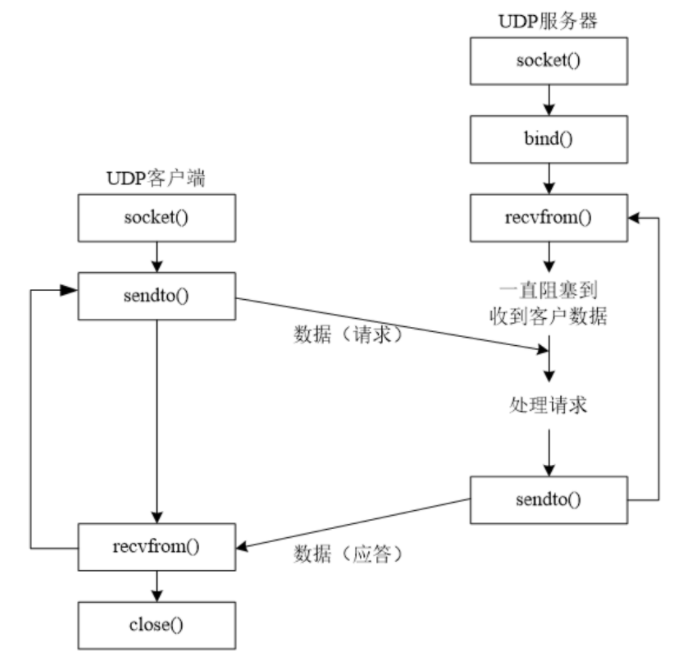

用户数据报协议/互联网协议

用户数据报协议 (UDP) 和互联网协议 (IP) 分别位于 OSI 模型的接下来两层:传输层和网络层。UDP/IP 协议与以太网一样,不保证可靠的数据包接收,只能保证尽力传送。IP 协议的主要目的是在链路层之上提供一个抽象层。这样,如果底层链路层不是以太网,则不需要更改应用层软件。IP 协议通过另一对源地址和目标地址、分段偏移、标头校验和以及有效负载中使用的协议来提供此抽象。

设计

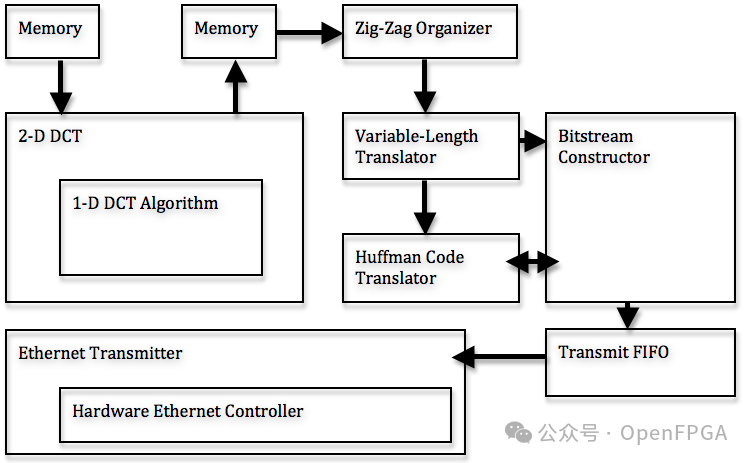

代码高度模块化,输出馈送到successive模块的输入中。编码步骤分为以下步骤(每个步骤都在单独的模块中实现):1-D DCT、2-D DCT/量化、zig-zag 组织、VL 转换、Huffman 转换和比特流构建。该系统目前可以实现 256x256 图像,但可以扩展分析更多像素。数据架构图如下所示:

因为仅涉及灰度成像,所以只需要彩色系统所需的三分之一的内存和处理能力。对于处理彩色图像的系统,需要将上述整个压缩过程单独应用于每个颜色通道。该项目通过选择每个像素的绿色值来获得灰度图像,而不是从 RGB 到 YUV 的转换。这种简化虽然并不完全正确,但该项目的重点不是图像,而是压缩,因此没有必要在转换操作上浪费额外的计算。

1-D DCT

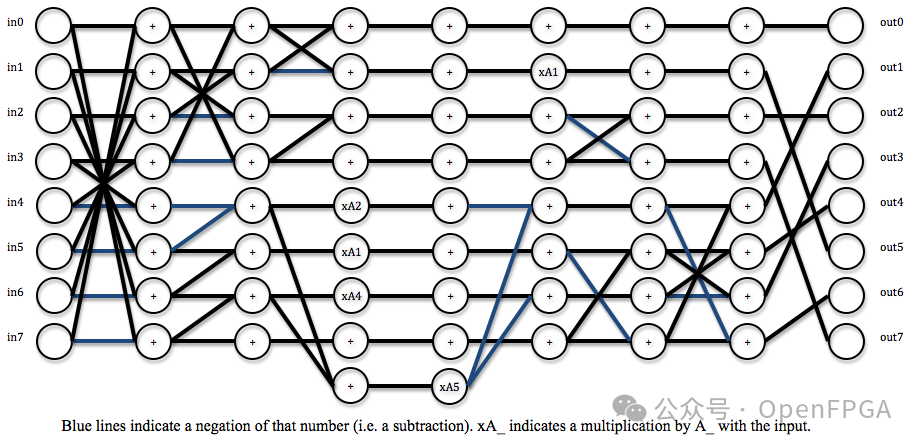

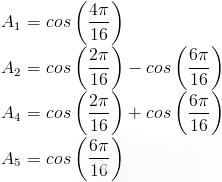

1-D DCT 使用快速算法实现,需要八个周期才能完成。该算法主要需要输入和结果总和的连续相加,其中三个中间步骤期间发生五次乘法。该算法产生 DCT 结果,结果是根据实际 DCT 结果按某个因子缩放的。然而,可以在量化步骤中考虑比例,从而产生正确的量化变换矩阵。系数的比例因子如下:

算法数据流如下图所示。

该模块是按照流水线设计,所以每个时钟周期都可以输入新的输入值,并在八个周期后输出新的输出。这使得模块能够更快地进行数据处理。

2-D DCT

2-D DCT 是可分离运算,意味着它可以通过对 8x8 块的每一行应用 1-D DCT,然后再将其应用于 8x8 块的列来获得最终结果。使我们能够使用流水线 1-D DCT 非常快速地执行 2-D DCT,方法是将块的行馈送到 1-D 模块中 8 个周期,然后获取结果并将这些列反馈回同一模块。

在将结果写回内存之前,也会在此 2D 模块中执行量化。由于算法的缩放与量化相结合的方式,整个操作仅需要对二维算法结果进行移位。

Zig-Zag

通过适当的顺序从内存中读取值来实现Zig-Zag。块的元素存储在直接从图像内像素坐标获得的地址中。存储器的输出以每周期一个像素的速率直接馈送到转换器中。

VL 和 RL

从像素的量化值到可变长度代码的转换是使用查找表完成的。该表包含代码的值和长度(以bit为单位)。然后这两个值被发送到霍夫曼翻译器。霍夫曼转换器采用前面的零数量和系数代码的大小。这两个数字被馈送到另一个查找表,该查找表给出霍夫曼代码作为非零系数的“标头”。

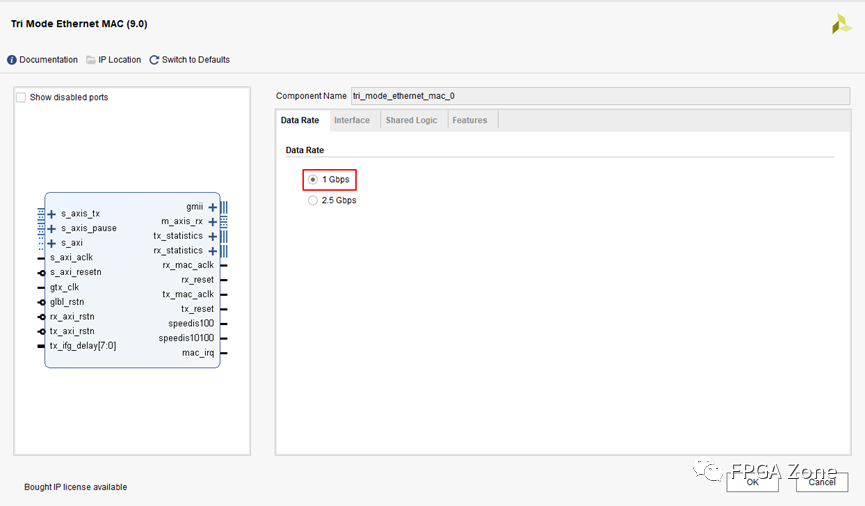

硬件以太网控制器

硬件以太网控制器用于初始化 DM9000A 控制芯片、向 DM9000A 推送数据包、从 DM9000A 抓取接收到的数据以及从 DM9000A 接收中断。

控制器分为两个独立的状态机,一个处理发往 DM9000A 和来自 DM9000A 的命令(包括中断),另一个处理发送和接收序列。

发送序列包括:

等待输入 FIFO 不为空。将第一个值存储为有效负载中的字节数。

告诉硬件控制器将存储多少字节,包括以太网标头。

将以太网帧作为数据发送到DM9000A。

将负载发送到DM9000A。

通过中断等待传输完成。返回空闲状态。

UDP

使用FIFO数据结构,UDP Wrapper 首先获取有效负载中的字节总数,然后一次获取 16 位的有效负载。Wrapper 使用状态机执行以下步骤来发送单个 UDP 数据包:

等待输入 FIFO 不为空。将第一个值存储为有效负载中的字节数。

告诉硬件控制器将存储多少字节,包括 UDP/IP 标头。

将以太网帧作为数据发送到硬件控制器。

将IP 标头作为数据发送到硬件控制器。IP 校验和是在发送标头之前计算的。

将UDP 标头作为数据发送到硬件控制器。

将所有数据发送到硬件控制器。

由于 UDP Wrapper 的目的是让 FPGA 能够与通过以太网直接连接的单台计算机进行通信,因此许多值都被硬编码到 Verilog 中。硬编码值包括目标和源 MAC 地址、目标和源 IP 地址以及目标端口。这四个硬编码值均设置为广播地址,MAC 地址为 FFFFFF:FF,IP 地址为 255.255.255.255。目标端口被硬编码为 31373。其他值(例如 IP 标头校验和)是动态计算的,因为标头值不一定每次都相同。完成后,控制寄存器复位并返回等待状态。

结论

尽管我们无法让最终所需的系统运行,但我们确实创建了可以与各种其他应用程序相关的可用功能模块。UDP 包装器和硬件以太网控制器在任何网络通信项目中都非常有用。流水线式一维 DCT 算法可用于信号和图像处理项目。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

以太网

+关注

关注

40文章

5419浏览量

171590 -

计算机

+关注

关注

19文章

7488浏览量

87847 -

UDP

+关注

关注

0文章

325浏览量

33931

原文标题:FPGA 通过 UDP 以太网传输 JPEG 压缩图片

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA通过UDP以太网传输JPEG压缩图片

FPGA通过UDP以太网传输JPEG压缩图片

评论