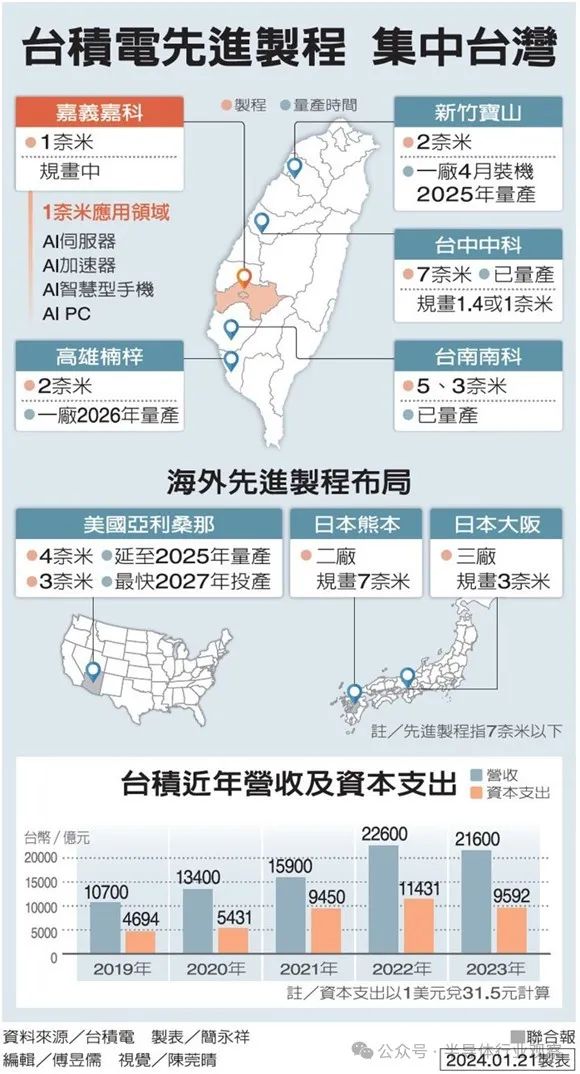

投资金额逾兆元的台积电一纳米建厂计划,拟在嘉义县太保市的科学园区设厂。这是台积电继日前法说会宣布在高雄厂增建第三座二纳米晶圆厂。

消息人士透露,台积电已向主管嘉义科学园区的南科管理局提出一百公顷用地需求,其中四十公顷设先进封装厂,后续六十公顷将作为一纳米建厂用地。由于台积电用地需求超出嘉义科学园区第一期规划的八十八公顷面积,预期将加速第二期扩编,以利台积电进驻。

台积电表示,设厂地点选择有诸多考量因素,台积电以台湾作为主要基地,不排除任何可能,也持续与管理局合作评估在适合半导体建厂用地。台积电指出,一切资讯请以公司对外公告为主。

嘉义县长翁章梁指出,尊重台积电设厂地点决定,相信会有最佳评估,诚挚欢迎台积电投资嘉义、更欢迎优秀的人才来嘉义,相信嘉县未来几年将成为西部走廊最具竞争力和发展潜力城市。他也说,嘉义科学园区目前绿电充足,也拟兴建海水淡化厂,为产业打造发展好基地,优渥条件绝对是首选。

据了解,台积电建厂小组在嘉义科学园区去年八月编定纳入南科管理局管辖的科学园区前,即派人前往进行厂勘,这也是在进驻桃园龙潭科学园区第三期扩建遭激烈抗争后,台积电建厂小组启动备案计划,最后决定放弃在龙科三期扩建案内的设厂计划。

台积电放弃龙潭建厂后,立即引来包括高雄、台中、彰化、嘉义、云林、台南及屏东等各县市首长争相拉拢前去投资,各地方政府也都表明将在土地和供水供电全力协助。翁章梁当时即表态,若台积电要到嘉义评估,他将担任召集人,并组专业小组全力协助,并强调该县有很多台糖土地,未来征收不会有太大问题。

不过,台积电长期向国科会主管的管理局租地,双方建立单一窗口,最后择定落脚嘉义科学园区,主要是因为此科学园区地理位置佳、 土地面积完整,并具可扩充性。这与翁章梁说法吻合。

一纳米制程落脚嘉科,可分散区域风险,也有利嘉义县城市发展,缩小城乡差距。再者,嘉义科学园区离嘉义高铁站车程仅七分钟,往北串起台积电中科、竹科厂,往南串连南科厂及高雄厂,均符合台积电创办人张忠谋先前所提可在一日内动员上千名工程师支援各厂区运作,让台湾西部科技廊带更完整。

业界人士分析,台积电进来宣布高雄扩建第三座2纳米厂、美国二厂踩煞车、1纳米落脚嘉义,宣示了台积电将先进制程根留台湾的决心。

此举不仅向全球芯片商表达「你要最具性价比且最先进的芯片代工,就是要来台湾生产」,也向三星及英特尔展现台积电拥有全球最完善的晶圆代工生态系,加上政策强力支持,要撼动台积电全球晶圆代工龙头地位,套句台积电总裁魏哲家的话「门都没有!」

台积电2nm工厂,也规划了两座

当台积电 (TSMC) 准备推出全新工艺技术时,通常会建造一座新晶圆厂来满足其 alpha 客户的需求,然后通过升级现有晶圆厂或建造另一座工厂来增加产能。对于 N2(2 纳米级),该公司似乎采取了略有不同的方法,因为它已经建造了两座具备 N2 能力的晶圆厂,并正在等待政府批准第三座晶圆厂。

我们还准备从 2025 年开始量产 N2,”台积电即将离任的董事长刘马克在与财务分析师和投资者举行的公司财报电话会议上表示。“我们计划在新竹和高雄建设多个晶圆厂或多期 2nm 技术科学园,以支持客户强劲的结构性需求。[…]“在台中科学园区,政府审批程序正在进行中,也已步入正轨。”

台积电正准备在台湾建设两家能够生产 N2 芯片的制造工厂。第一个晶圆厂计划选址新竹县宝山附近,毗邻 R1 研发中心,该中心是专门为开发 N2 技术及其后续技术而建造的。该工厂预计将于 2025 年下半年开始大批量制造 (HVM) 2 纳米芯片。第二个具有 N2 能力的制造工厂将位于高雄科学园区,该园区是高雄附近的南台湾科学园区的一部分。该工厂 HVM 的启动预计会稍晚一些,可能在 2026 年左右。

此外,该代工厂正在努力获得政府批准,在台中科学园区建造另一座具有 N2 能力的晶圆厂。如果该公司在 2025 年开始建设该工厂,该工厂最快可在 2027 年投产。

台积电拥有三个能够使用其 2nm 工艺技术制造芯片的晶圆厂,准备在未来几年提供巨大的 2nm 产能。

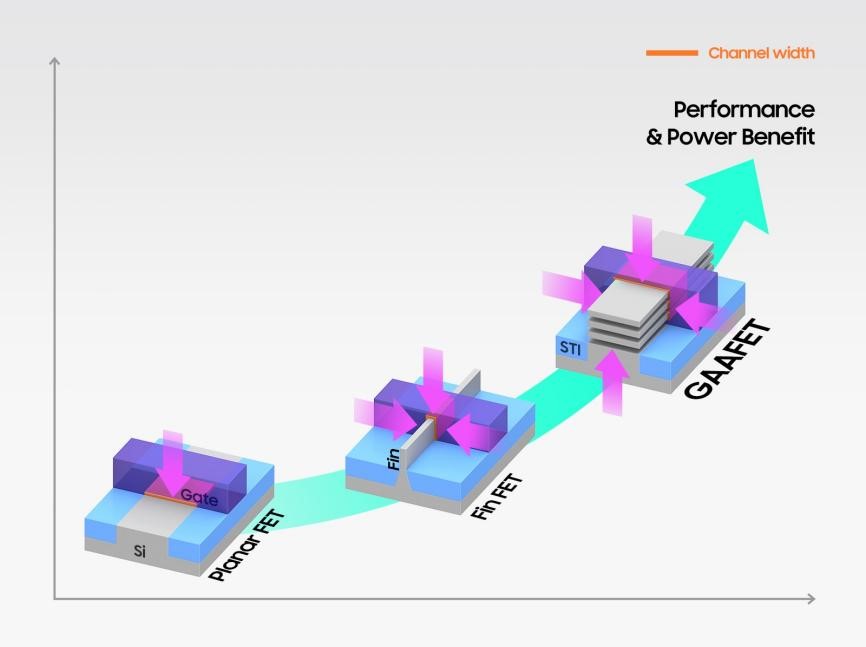

台积电预计在 2025 年下半年左右启动使用其 N2 工艺技术的 HVM,该技术采用环栅 (GAA) 纳米片晶体管。台积电的第二代2纳米级工艺技术 - N2P - 将增加背面功率传输。该技术将于2026年实现量产。

1nm后的芯片,靠什么?

毫无疑问,下一代的CMOS逻辑将迈入1nm时代,在即将举行的IEDM上,。有不少关于“下一代 CMOS”的著名讲座。因此,我们将它们分为“互补FET”、“2D材料”和“多层布线”子类别。

在本文中,按顺序进行介绍。

将构成 CMOS 的两个 FET 堆叠起来,将硅面积减少一半

第一个是“下一代 CMOS 逻辑”领域中的“互补 FET (CFET)”。CMOS逻辑(逻辑电路)由至少两个晶体管组成:一个n沟道MOS FET和一个p沟道MOS FET。晶体管数量最少的逻辑电路是反相器(逻辑反相电路),由1个n沟道MOS和1个p沟道MOS组成。换句话说,它需要相当于两个晶体管的硅面积。

CFET 是这两种类型 MOSFET 的三维堆叠。理论上,可以使用一个 FET 占用的硅面积来创建 CMOS 逻辑。与传统CMOS相比,硅面积减半。但制造工艺相当复杂,挑战重重,打造难度较大。

在IEDM 2023上,CFET研发取得了重大进展。台积电和英特尔均推出了单片堆叠下层 FET 和上层 FET 的 CMOS 电路。TSMC 演示了一个 CFET 原型,该原型将 n 沟道 FET 单片堆叠在 p 沟道 FET 之上。所有 FET 均具有纳米片结构。栅极间距为48nm。制造成品率达90%以上。目前的开/关比超过6位数。

Intel 设计了一个 CFET 原型,将三个 n 沟道 FET 单片堆叠在三个 p 沟道 FET 之上 (29-2)。所有 FET 均具有纳米带结构(与纳米片结构基本相同的结构)。我们制作了栅极间距为 60nm 的 CMOS 反相器原型并确认了其运行。

采用二维材料制成GAA结构的纳米片通道

下一代 CMOS 逻辑晶体管的另一个有希望的候选者是通道是过渡金属二硫属化物 (TMD) 化合物的二维材料(单层和极薄材料)的晶体管。当 MOSFET 的沟道尺寸缩短时,“短沟道效应”成为一个主要问题,其中阈值电压降低且变化增加。减轻短沟道效应的一种方法是使沟道变薄。TMD很容易形成单分子层,原则上可以创建最薄的通道。

TMD 沟道最初被认为是一种用于小型化传统平面 MOSFET 的技术(消除了对鳍结构的需要)。最近,选择TMD作为环栅(GAA)结构的沟道材料的研究变得活跃。候选通道材料包括二硫化钼(MoS2)、二硫化钨(WS2)和二硒化钨(WSe2)。

包括台积电等在内的联合研究小组开发了一种具有纳米片结构的n沟道FET,其中沟道材料被单层MoS2取代。栅极长度为40nm。阈值电压高,约为1V(常关操作),导通电流约为370μA/μm(Vds约为1.0V),电流开关比为10的8次方。

imec和 Intel 的联合研究团队使用二维沟道候选材料在 300mm 晶圆上制造了原型 n 沟道 MOS 和 p 沟道 MOS,并评估了它们的特性。候选材料有 MoS2、WS2和 WSe2。MoS2单层膜适用于n沟道FET,WSe多层膜适用于p沟道FET。

包括台积电等在内的联合研究小组开发出一种二维材料晶体管,其电流-电压特性与n沟道FET和p沟道FET相同。MoS2(一种 n 沟道材料)和 WSe2(一种 p 沟道材料)在蓝宝石晶圆上生长,并逐个芯片转移到硅晶圆上。此外,英特尔还原型制作了具有GAA结构的二维材料沟道FET,并在n沟道和p沟道上实现了相对较高的迁移率。

石墨烯、钌和钨将取代铜 (Cu) 互连

多层布线是支持CMOS逻辑扩展的重要基础技术。人们担心,当前流行的铜(Cu)多层互连的电阻率将由于小型化而迅速增加。因此,寻找金属来替代 Cu 的研究非常活跃。候选材料包括石墨烯、钌 (Ru) 和钨 (W)。

台积电将宣布尝试使用石墨烯(一种片状碳同素异形体)进行多层布线。当我们制作不同宽度的互连原型并将其电阻与铜互连进行比较时,我们发现宽度为15 nm或更小的石墨烯互连的电阻率低于铜互连的电阻率。石墨烯的接触电阻率也比铜低四个数量级。将金属离子嵌入石墨烯中可以改善互连的电性能,使其成为下一代互连的有前途的材料。

imec 制作了高深宽比 (AR) 为 6 至 8、节距为 18 nm 至 26 nm 的 Ru 两层精细互连原型,并评估了其特性。制造工艺为半镶嵌和全自对准过孔。在AR6中原型制作宽度为10 nm(对应间距18 nm至20 nm)的Ru线测得的电阻值低于AR2中模拟的Cu线的电阻值。

应用材料公司开发了一种充分利用 W的低电阻互连架构。适用于2nm以上的技术节点。我们充分利用 W 衬垫、W 间隙填充和 W CMP(化学机械抛光)等基本技术。

将存储器等元件纳入多层布线过程

一种有些不寻常的方法是研究多层互连过程(BEOL)中的存储器等构建元件。多层布线下面通常是 CMOS 逻辑电路。因此,理论上,BEOL 中内置的元件不会增加硅面积。它是提高存储密度和元件密度的一种手段。

斯坦福大学和其他大学的联合研究小组将提出在多层逻辑布线工艺中嵌入氧化物半导体 (OS) 增益单元晶体管型存储元件的设计指南。操作系统选择了氧化铟锡 (ITO) FET。我们比较了 OS/Si 混合单元和 OS/OS 增益单元。

imec 开发了MRAM技术,可将自旋轨道扭矩 (SOT) 层和磁隧道结 (MTJ) 柱减小到大致相同的尺寸。它声称可以将功耗降低到传统技术的三分之一,将重写周期寿命延长10的15次方,并减少存储单元面积。

加州大学洛杉矶分校率先集成了压控 MRAM 和 CMOS 外围电路。MRAM的切换时间极短,为0.7ns(电压1.8V)。原型芯片的读取访问时间为 8.5ns,写入周期寿命为 10 的 11 次方。

将计算功能纳入传感器中

我还想关注“传感器内计算技术”,它将某种计算功能集成到传感器中。包括旺宏国际在内的联合研究小组将展示基于 3D 单片集成技术的智能图像传感器。使用 20nm 节点 FinFET 技术,将类似于 IGZO DRAM 的存储层单片层压在 CMOS 电路层的顶部,并在其顶部层压由二维材料 MoS2制成的光电晶体管阵列层。光电晶体管阵列的布局为 5 x 5。

西安电子科技大学和西湖大学的联合研究小组设计了一种光电神经元,由一个光电晶体管和一个阈值开关组成,用于尖峰神经网络。对连续时间内的传感信号(光电转换信号)进行压缩编码。

在硅晶圆上集成 GaN 功率晶体管和 CMOS驱动器

对于能带隙比 Si 更宽的化合物半导体器件(宽禁带器件),在 Si 晶圆上制造氮化镓 (GaN) 基 HEMT 的运动十分活跃。英特尔在 300mm 硅晶圆上集成了 GaN 功率晶体管和 CMOS 驱动器。CMOS驱动器是GaN增强型n沟道MOS HEMT和Si p沟道MOS FET的组合。用于GaN层的Si晶片使用面。对于 Si MOS FET,将另一个面的硅晶片粘合在一起,只留下薄层,用作沟道。

CEA Leti 开发了用于 Ka 波段功率放大器的 AlN/GaN/Si MIS-HEMT (38-3)。兼容200mm晶圆Si CMOS工艺。通过优化SiN栅极绝缘膜原型制作的HTMT的ft为81GHz,fmax为173GHz。28GHz 时的 PAE(功率负载效率)极高,达到 41%(电压 20V)。假设我们已经实现了与 GaN/SiC 器件相当的性能。

6400万像素、像素尺寸为0.5μm见方的小型CMOS图像传感器。

在图像传感器中,显着的成果包括像素数量的增加、像素尺寸的减小、噪声的减少以及自动对焦功能的进步。三星电子已试制出具有 6400 万像素、小像素尺寸为 0.5 μm 见方的高分辨率 CMOS 图像传感器。

使用铜电极混合键合堆叠三个硅晶片,并为每个像素连接一个光电二极管和后续电路。与传统型号相比,RTS(随机电报信号)噪声降低了 85%,FD(浮动扩散)转换增益提高了 67%。

OmniVision Technologies 开发了一款 HDR 全局快门 CMOS 图像传感器,其像素间距为 2.2μm。它是通过将两片硅片粘合在一起而制成的。FPN(固定模式噪声)为1.2e-(rms值),时间噪声为3.8e-(rms值)。

佳能已经推出了双像素交叉 CMOS 图像传感器原型,其中一对光电二极管以 90 度扭转排列。通过全方位相位差检测执行自动对焦 (AF)。AF 的最低照度低至 0.007 lux。

-

台积电

+关注

关注

44文章

5631浏览量

166402 -

晶圆厂

+关注

关注

7文章

620浏览量

37852 -

光电二极管

+关注

关注

10文章

402浏览量

35931

原文标题:台积电,1nm

文章出处:【微信号:jbchip,微信公众号:电子元器件超市】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

台积电1nm进展曝光!预计投资超万亿新台币,真有必要吗?

1nm后的芯片,靠什么?

1nm后的芯片,靠什么?

评论