在PCB设计中,如何避免串扰?

在PCB设计中,避免串扰是至关重要的,因为串扰可能导致信号失真、噪声干扰及功能故障等问题。

一、了解串扰及其原因

在开始讨论避免串扰的方法之前,我们首先需要了解什么是串扰及其常见原因。串扰是指一个信号电路中的电流或电磁场对周围其他电路产生干扰的现象。常见的原因包括电磁辐射、电磁感应、信号反射、互连线长度不匹配等。

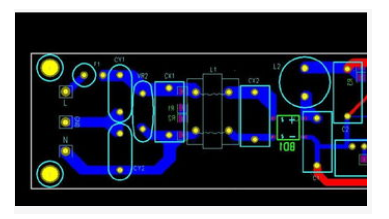

二、正确的布局设计

1.分离敏感信号与噪声源:尽量分离敏感信号线和噪声源,使它们物理上保持足够的距离。这可以减少噪声来源对敏感信号的干扰。

2.地线规划:合理规划地线,保持地线的连续性和低阻抗。通过增加地面平面的面积,可以减少地线回路的自感和电阻。

3.隔离vwin

和数字信号:模拟信号和数字信号的电路应该尽量分离放置,以减少彼此之间的串扰。如果不得不相互交叉布线,可以采用地隔离设备来隔离信号。

4.层次布局:尽量将不同类型的信号布置在不同的层次上。例如,模拟信号可以布置在底层,而数字信号可以布置在顶层。这种布局方式可以减少模拟和数字信号之间的耦合。

三、综合考虑信号走线和电源线

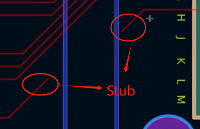

1.信号线走向:合理规划信号线的走向,避免平行布线和交叉布线。如果信号线必须平行走线,可以通过增加地间隔或引入绕组间隔来减小串扰。

2.绕组间距:对于高频信号线,应考虑增加绕组间的距离以减少串扰。较高的绕组间距可以降低电磁耦合,减少相邻线路之间的互感。

3.电源线布线:电源线是一个常见的串扰源。在布线时,应尽量将电源线与其他敏感信号线隔离,并远离高速信号线。

四、噪声抑制技术

1.滤波器:在PCB上适当布置滤波器可以抑制一部分噪声。例如,可采用电源线上的滤波电容来过滤高频噪声。

2.屏蔽:在设计中采用屏蔽材料或屏蔽罩可以有效地减少电磁辐射和感应,从而降低串扰。

3.电磁兼容性设计:在设计信号电路时,应该遵循电磁兼容性(EMC)原则,包括合理选用元器件、合理布局和阻抗匹配等。

五、仿真与调试

1.电磁场仿真:通过使用电磁场仿真软件,可以在设计阶段模拟和分析电磁场的分布情况,从而更好地了解并优化布局。

2.工程验算:在PCB设计完成后,进行工程验算是非常重要的。通过测量和分析实际电路的性能,可以识别并解决可能存在的串扰问题。

3.故障排除:如果在实际应用中发现了串扰问题,需要进行逐步的故障排除。可以通过排查布线、检查接地情况、减少元器件布线长度等方法来消除或减小串扰。

结论

串扰是PCB设计中常见的问题,可能导致信号失真和噪声干扰。为了避免串扰,我们需要在设计和布局阶段充分考虑并采取适当的措施。合理的布局设计、信号线和电源线的走线规划、噪声抑制技术以及仿真和调试等方法都可以帮助我们避免串扰问题的发生。只有在实践中不断改进和优化,才能够设计出高品质的PCB电路板。这些措施都是为了确保PCB电路板的正常运行并提高系统的可靠性。

-

PCB设计

+关注

关注

394文章

4683浏览量

85534 -

电磁兼容性

+关注

关注

6文章

424浏览量

33702 -

信号失真

+关注

关注

0文章

73浏览量

11369

发布评论请先 登录

相关推荐

pcb设计中如何设置坐标原点

嵌入式开发中引起串扰的原因是什么?

PCB设计中的串扰是什么意思?如何减少PCB设计中的串扰呢?

PCB产生串扰的原因及解决方法

如何使用SigXplorer进行串扰的仿真

怎么样抑制PCB设计中的串扰

在PCB设计中,如何避免串扰?

在PCB设计中,如何避免串扰?

评论