如何用异或门实现反向功能

要使用异或门实现反向(即将输入信号的逻辑电平反转)功能,可以按照以下步骤进行操作:

1. 将输入信号连接到两个异或门的一个输入端,分别命名为 A。

2. 将一个确定的信号引线(常常称为控制信号或使能信号)连接到另一个异或门的另一个输入端,分别命名为 B。这个确定的信号在反向功能处于活动状态时应为高电平状态,否则为低电平状态。

3. 将两个异或门的输出端连接在一起,作为最终的反向输出。

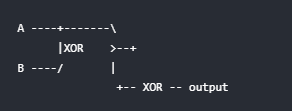

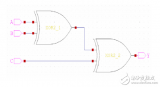

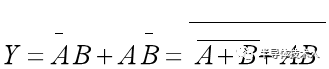

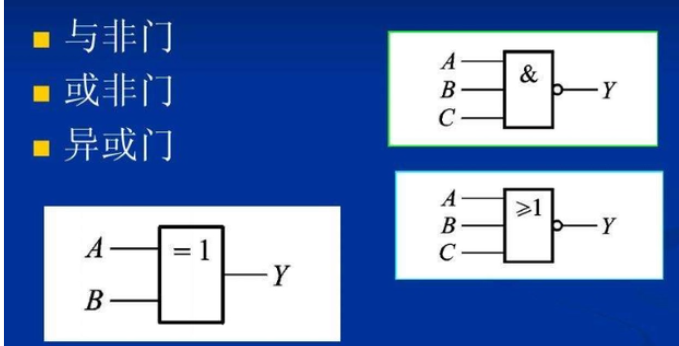

逻辑电路符号表示如下:

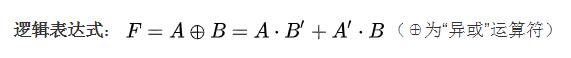

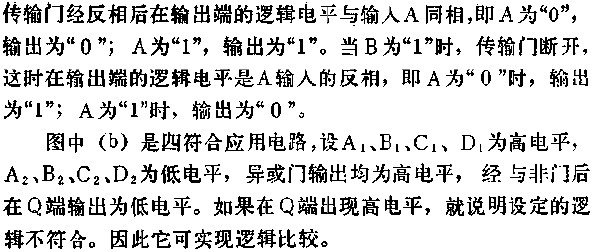

在这种实现中,当控制信号 B 为高电平时,异或门的输出将反转输入信号 A 的逻辑电平。如果 A 是高电平,则输出是低电平;如果 A 是低电平,则输出是高电平。而当控制信号 B 为低电平时,异或门的输出与输入信号 A 保持一致。

通过这样的连接和逻辑关系,我们可以使用异或门来实现反向功能,即将输入信号的逻辑电平反转。这个方法在数字逻辑电路设计中经常被使用,以实现信号的反转或选通操作。

异或门当做反相器使用怎么连接

如果要使用异或门作为反相器(Inverter)来反转输入信号的逻辑电平,可以按照以下连接方式进行操作:

1. 将输入信号连接到一个异或门的一个输入端,分别命名为 A。

2. 将另一个输入端连接到一个确定的信号引线,使其保持固定的逻辑电平,可以是高电平或低电平。假设选择高电平,将其命名为 B。

3. 将这个异或门的输出端连接到最终的反转输出。

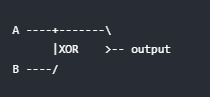

逻辑电路符号表示如下:

在这种连接方式中,异或门的一个输入端连接到输入信号 A,而另一个输入端连接到固定的逻辑电平 B。当输入信号 A 是高电平时,异或门的输出会反转为低电平;当输入信号 A 是低电平时,异或门的输出会反转为高电平。

这样,异或门就起到了反相器的作用,可以将输入信号的逻辑电平反转输出。

需要注意的是,使用异或门作为反相器时,控制信号 B 必须保持固定的逻辑电平。如果控制信号 B 是可变的或需要动态控制的,那么这种连接方式将无法实现预期的反转功能。在这种情况下,可以考虑使用其他类型的逻辑门或具备反相器功能的特殊器件。

异或门如何连接输入端实现求反

要使用异或门来实现求反(求输入信号的反码)功能,可以按照以下连接方式进行操作:

1. 将输入信号连接到两个异或门的一个输入端,分别命名为 A。

2. 将另一个输入端连接到一个确定的信号引线(常常称为使能信号)上,使其保持固定的逻辑电平,可以是高电平或低电平。假设选择高电平,将其命名为 B。

3. 将两个异或门的输出端连接在一起,作为最终的求反输出。

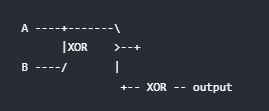

逻辑电路符号表示如下:

在这种连接方式中,当使能信号 B 为高电平时,两个异或门的输出将取决于输入信号 A。如果 A 是高电平,则输出是低电平;如果 A 是低电平,则输出是高电平。而当使能信号 B 为低电平时,两个异或门的输出都是固定的,并不受输入信号 A 的影响。

因此,通过这样的连接和逻辑关系,我们可以使用异或门来实现求反功能,即求输入信号的反码。

需要注意的是,使能信号 B 必须保持固定的逻辑电平,以确保输出始终是输入信号 A 的反码。如果使能信号 B 是可变的或需要动态控制的,那么这种连接方式将无法实现预期的求反功能。在这种情况下,可以考虑使用其他类型的逻辑门或具备求反功能的特殊器件。

审核编辑:黄飞

-

反相器

+关注

关注

6文章

311浏览量

43288 -

异或门

+关注

关注

1文章

32浏览量

17796 -

逻辑电平

+关注

关注

0文章

152浏览量

14411

发布评论请先 登录

相关推荐

【数字电路】关于逻辑异或门基础知识点总结教程

异或门的逻辑功能解析

三输入异或门逻辑图及表达式解析

异或门基础知识(逻辑表达式_真值表_符号_应用)

如何用异或门实现反向功能 异或门如何连接输入端实现求反

如何用异或门实现反向功能 异或门如何连接输入端实现求反

评论