什么是复位同步电路reset synchronizer?

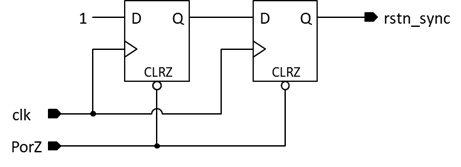

下图是一个最简单的复位同步电路。这个电路的输出rstn_sync用作后续电路中D flip flop的复位信号。

这个电路的工作原理是:

-PorZ低电平,复位同步电路里的两个D flip flop都被复位。电路的输出rstn_sync为0,后续电路被复位。

-PorZ由低变高。clk上升沿到来时,第一个D flip flop先变1。过一个周期,第二个D flip flop变1,rstn_sync变1,后续电路离开复位状态,开始正常工作。

-如果PorZ由低变高和clk上升沿离得很近,第一个D flip flop可能进入亚稳态(metastability)。不过没关系,第二个D flip flop的输出rstn_sync还是稳定的。复位同步电路的主要功能就是保障rstn_sync是稳定的0或1,在芯片的有生之年不发生亚稳态(或亚稳态的机率小到忽略不计)。同时,保障rstn_sync相对于clk有一个固定的时序关系。下面详细讨论。

为什么需要复位同步电路reset synchronizer?

这和D flip flop一个比较隐蔽的timing指标有关– removal/recovery time。D flip flop对时钟沿active edge和复位的release edge是有时序要求的。通常,D flip flop复位端的release edge必须要滞后时钟active edge一段时间(removal time),而且还要超前下一个时钟active edge一段时间(recovery time)。如果有违例,那这个D flip flop就会进入亚稳态,在后仿中显示为X。

复位同步电路reset synchronizer的输出rstn_sync相对于时钟clk有一个固定的时序关系。在PnR (place & route)中,工具构造buffer tree去buffer rstn_sync,并算出buffer后rstn_sync到后续每个D flip flop复位端的时间,通过插入或调整buffer,保障后续电路中每一个D flip flop的复位端都满足removal/recovery要求。反之,如果rstn_sync相对于时钟clk没有有一个固定的关系,那工具就无从下手了,也就无法保障removal/recovery要求了。

顺便说一下,综合工具是不查removal/recovery time的。如果复位电路上有错,通常会在设计流程很后面才发现,改起来代价也会高一些。所以一定要在一开始就重视复位电路。

为什么复位同步电路reset synchronizer自己不会进入亚稳态?

前面讲了,第一级的D flip flop是有可能进入亚稳态。关键在于第二级。第二级的D输入端在第一个clk到来的时刻仍是稳定的低电平(第一级的输出此时尚未变成亚稳态X),第二级的的状态不需要改变,仍旧保持原来复位后的0状态。等到第二个clk到来的时候,如果第一级已经不在亚稳态了,第二级的D输入就是一个稳定的1,那第二级的输出rstn_sync自然就变成稳定的1了。即使第一级在第二个clk到来的时候没有完全走出亚稳态,只要第一级的输出不在中间值附近,第二级仍会把第一级的输出当成0或1,第二级的输出rstn_sync也就因此为稳定的0或1。这也就是为什么有时候复位同步电路reset synchronizer的latency是在1-3个时钟之间。

有条件的同学,不妨跑一下Spectresim,观察一下D flip flop内部的信号,加深removal/recovery time的理解。眼见为实。

如果两个D flip flop还不够MTBF指标(发生亚稳态的概率仍不够小),可以再加第三级。

有些标准元库中有专门的同步电路,synchronizer cell。应该尽量使用这种synchronizer cell,比自己用两个D flip flop搭更可靠。专门的synchronizer第二级是高增益的,大大降低第二级进入亚稳态的可能性。

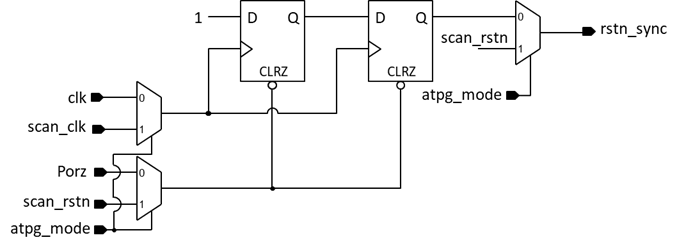

复位同步电路reset synchronizer能加到扫描链里吗?

这里加了两个MUX,这样可以让工具把同步复位电路的两个D flip flop连到scanchain里,增加test coverage。

使用复位同步电路reset synchronizer需要注意的地方

一个复位同步电路reset synchronizer只能用到一个时钟域。如果有几个不同步的时钟域,就要考虑使用多个复位同步电路。同步的时钟域可以考虑复用一个复位同步电路reset synchronizer,但要做得仔细一些。

复位同步电路reset synchronizer有什么弊病吗

复位同步电路reset synchronizer其实只在复位信号release的时候派上用场。复位结束后,这个电路其实就没用了。但这个电路的时钟还在switch,这个电路还在耗电。如果是高速时钟,这个耗电就可观了。低功耗设计,就要考虑是否可以关掉时钟。这个根据不同场景,就非常复杂了,需要非常小心。

复位同步电路reset synchronizer是必须的吗?

很多人通常不加思索一上来就加上同步复位电路reset synchronizer。这种条件反射本身是好习惯。

如果精益求精,那就要多思考一下了。有些场景是不需要复位同步电路reset synchronizer的。

复位的目的是让电路有个明确的起始状态。如果不需要明确的初始状态,而且电路跑一段时间后能清除所有不确定状态,进入正常状态,那就可以考虑不用复位同步电路。例如FIR。如果使用场景中可以容忍初始输出为垃圾,异步复位是可以的。

还有一个被99%的设计者忽略的场景。如果复位信号release的时候,时钟还没有启动,那就根本不需要复位同步电路reset synchronizer。很多时候,芯片是内部oscillator, PLL提供时钟的。而oscillator, PLL启动都需要时间的。如果复位在这段时间内release,那就不需要同步复位电路reset synchronizer了。在低功耗设计中,尤其是多个内部时钟域的场景,省下的功耗就可观了。当然,设计要做得非常仔细。

还有一个场景就是内部产生的复位信号。做得精妙的设计,可以保证在内部复位release的时候没有时钟,也就不需要什么复位同步电路reset synchronizer了。内部产生复位信号是一个很有效的设计技巧。这个技巧复用现成的reset network同时将很多D flip flop清零,省去了在D flip flop的D输入逻辑(D inputlogiccone)加上清零条件,可以节省很多门。

复位同步电路reset synchronizer在RTL里的实现

通常做成一个单独的module,在主设计中例化这个module。

好了,希望复位同步讲全面了。

审核编辑:黄飞

- pll

+关注

关注

6文章

766浏览量

134809 - 复位电路

+关注

关注

13文章

314浏览量

44421 - 低电平

+关注

关注

1文章

108浏览量

13158 - 复位信号

+关注

关注

0文章

52浏览量

6257

发布评论请先登录

相关推荐

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

同步复位sync和异步复位async

同步复位和异步复位的比较(转载)

HT66Fx0系列MCU的Reset复位电路应用介绍

复位稳定放大器:TheResetStabilized A

STM32下载后无法自动复位,需手动复位下载程序时,勾选resetand run后仍不可自动复位

什么是复位同步电路 reset synchronizer?

什么是复位同步电路 reset synchronizer?

评论