01

12nm Cortex-A72后端实战

本项目是真实项目实战培训,低功耗UPF设计,后端参数如下:

工艺:12nm

频率:2.5GHz

资源:2000_0000instances

低功耗:DVFS

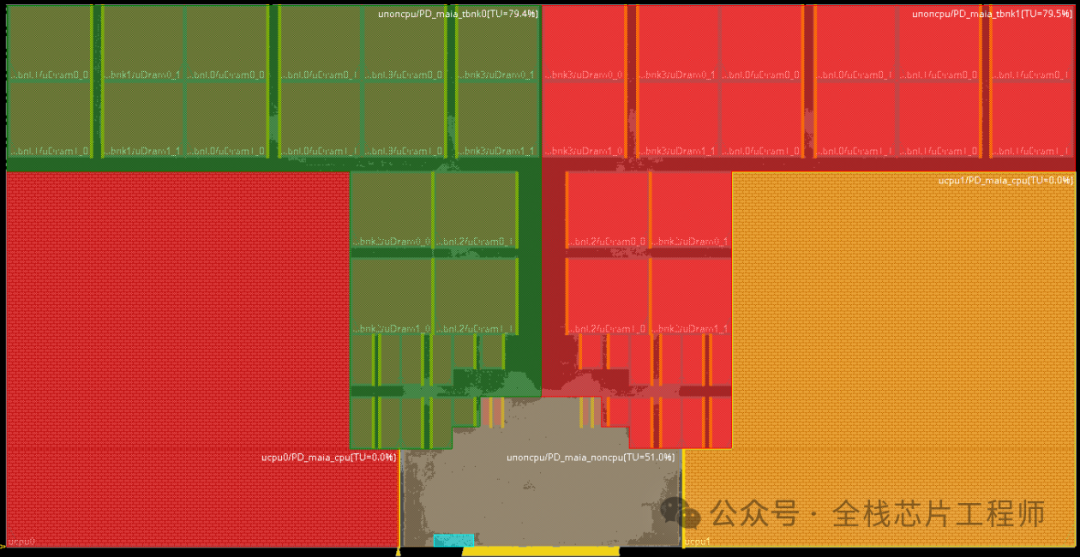

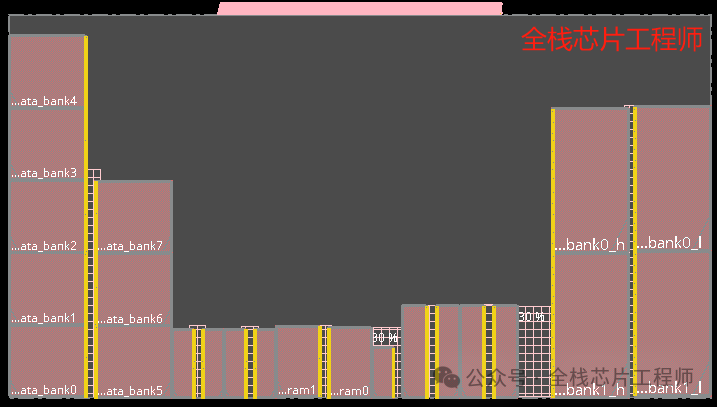

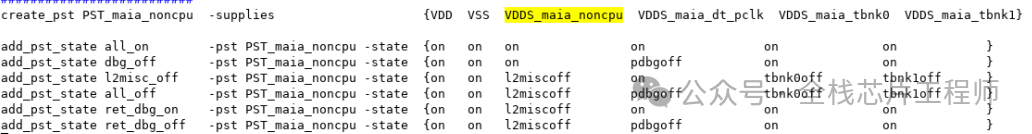

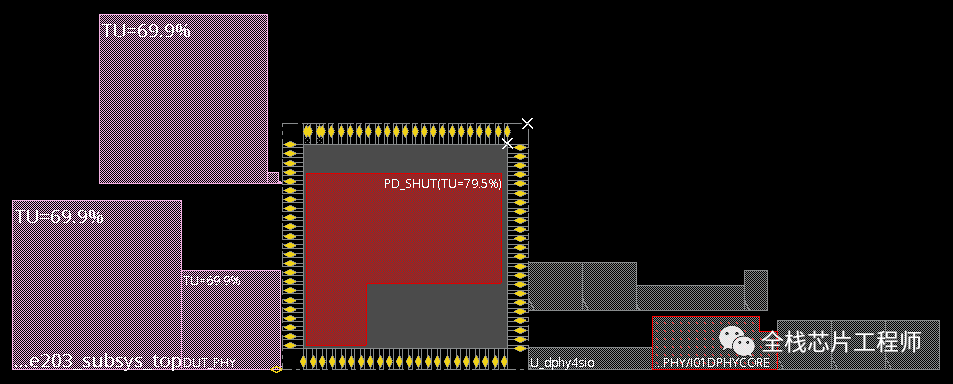

进阶版本的低功耗设计如下:7个power domain

Stampling打起来真是高级手工艺术,全网唯一:

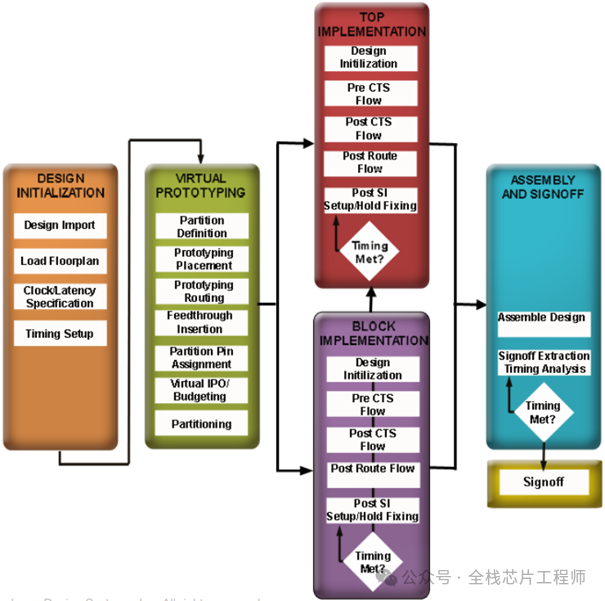

Flow:PartitionFlow

时钟结构分析:

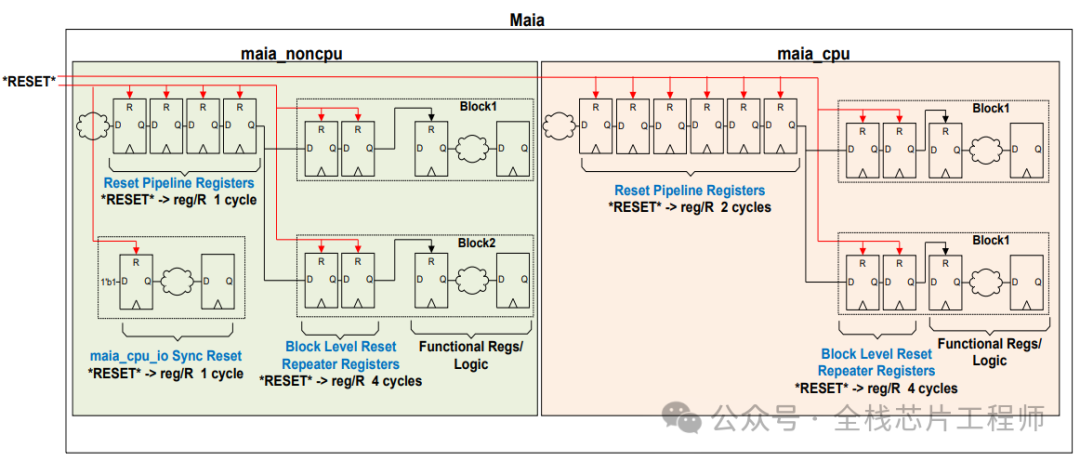

复位结构分析:

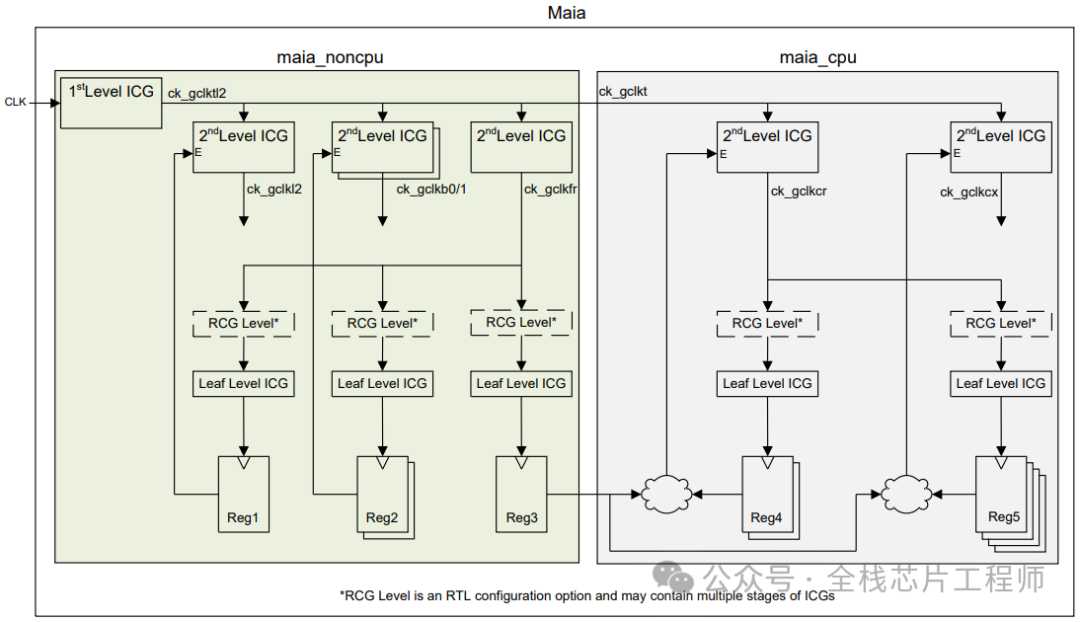

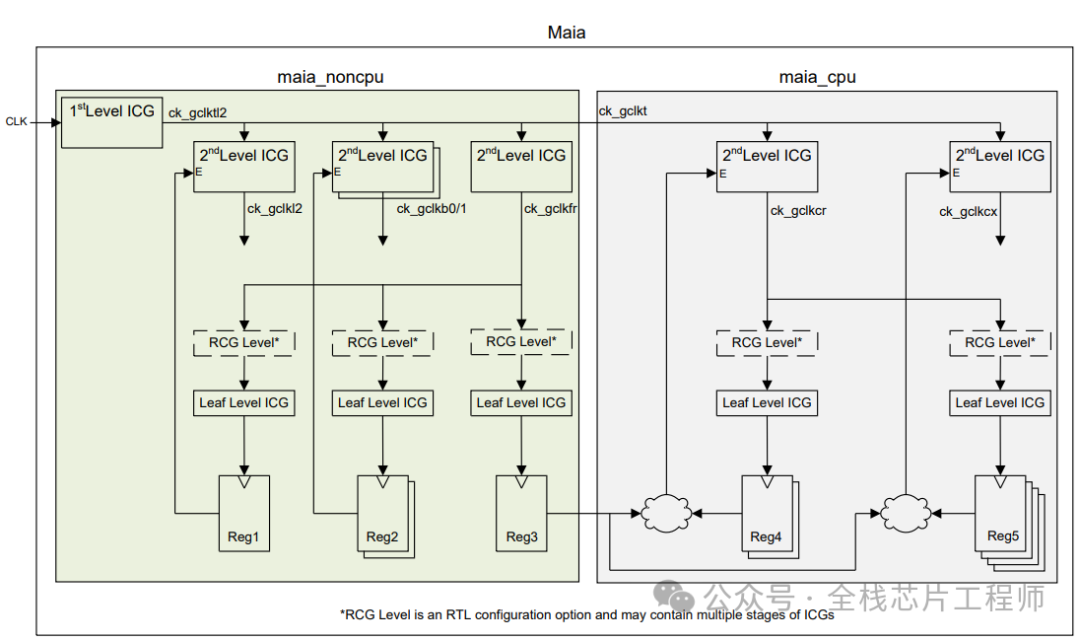

12nm 2.5GHz的A72实战训练营需要特别设置Latency,TOP结构如下,参加过景芯SoC全流程训练营的同学都知道CRG部分我们会手动例化ICG来控制时钟,具体实现参见40nm景芯SoC全流程训练项目,本文介绍下12nm 2.5GHz的A72实战训练营的Latency背景,欢迎加入实战。

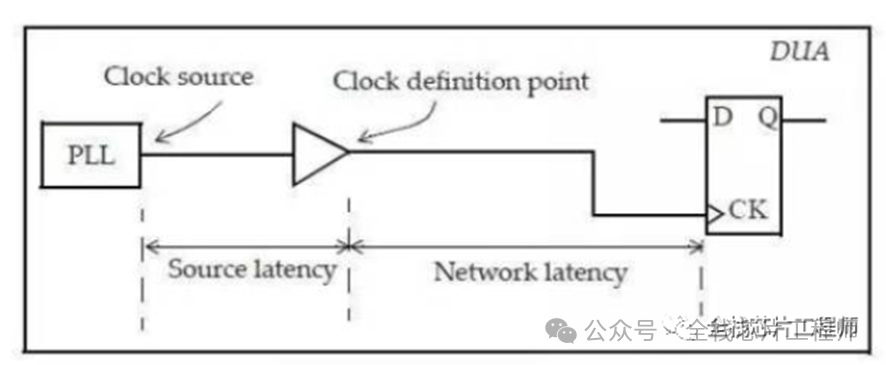

时钟传播延迟Latency,通常也被称为插入延迟(insertion delay)。它可以分为两个部分,时钟源插入延迟(source latency)和时钟网络延迟(Network latency)。

大部分训练营同学表示平时都直接将Latency设置为0了,那latency值有什么用呢?其实这相当于一个target值,CTS的engine会根据你设置的latency值来插入buffer来实现你的latency target值。

下图分为1st Level ICG和2nd Level ICG,请问这些ICG为什么要分为两层?

请问,为什么不全部把Latency设置为0?2nd Level ICG的latency应该设置为多少呢?

latency大小直接影响clock skew的计算。时钟树是以平衡为目的,假设对一个root和sink设置了400ps的latency值,那么对另外的sink而言,就算没有给定latency值,CTS为了得到较小的skew,也会将另外的sink做成400ps的latency。请问,为何要做短时钟树?因为过大的latency值会受到OCV和PVT等因素的影响较大,并有time derate的存在。

02

28nm Cortex-A7后端实战

此外,我们提供全国最低价的28nm A7后端设计,价格惊喜!打垮动辄1.5w-2.5w的后端培训价格!

我们再来对比下A72与A7的资源。A72Gate数目是A7的13倍!如果都采用28nm制程,A72的面积应该是1180790um^2,实际A72采用12nm制程面积是486100um^2,1180790/486100=2.4,符合摩尔定律。

Cortex-A7单核:

Gates=240291Cells=118421

Cortex-A72单核:

Gates=3125649Cells=1207766

28nmCortex-A7单核:

Area=90830.1um^2

12nmCortex-A72单核:

Area=486100.9um^2

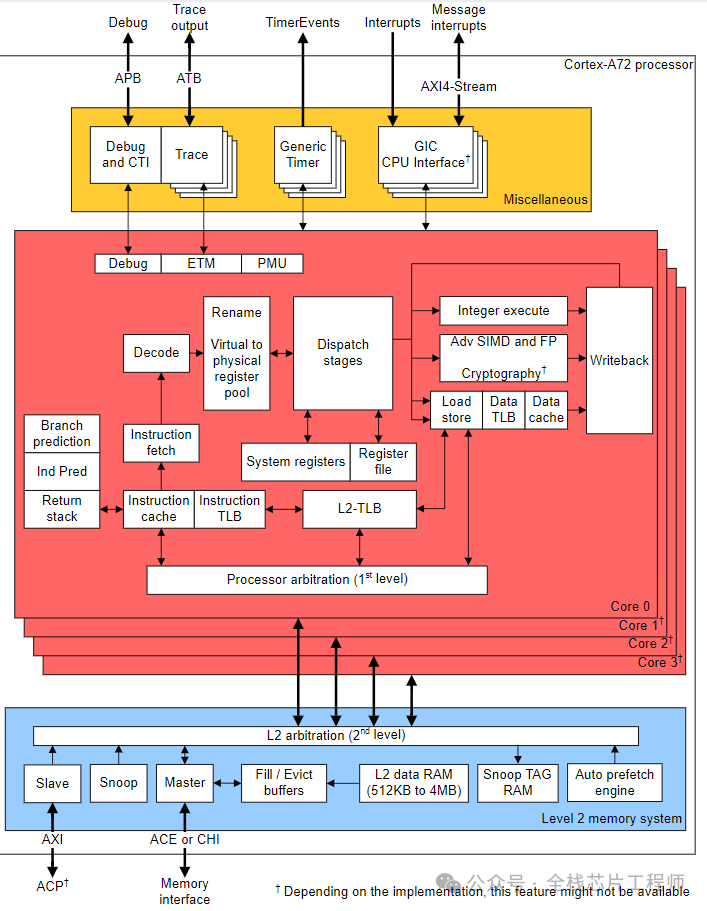

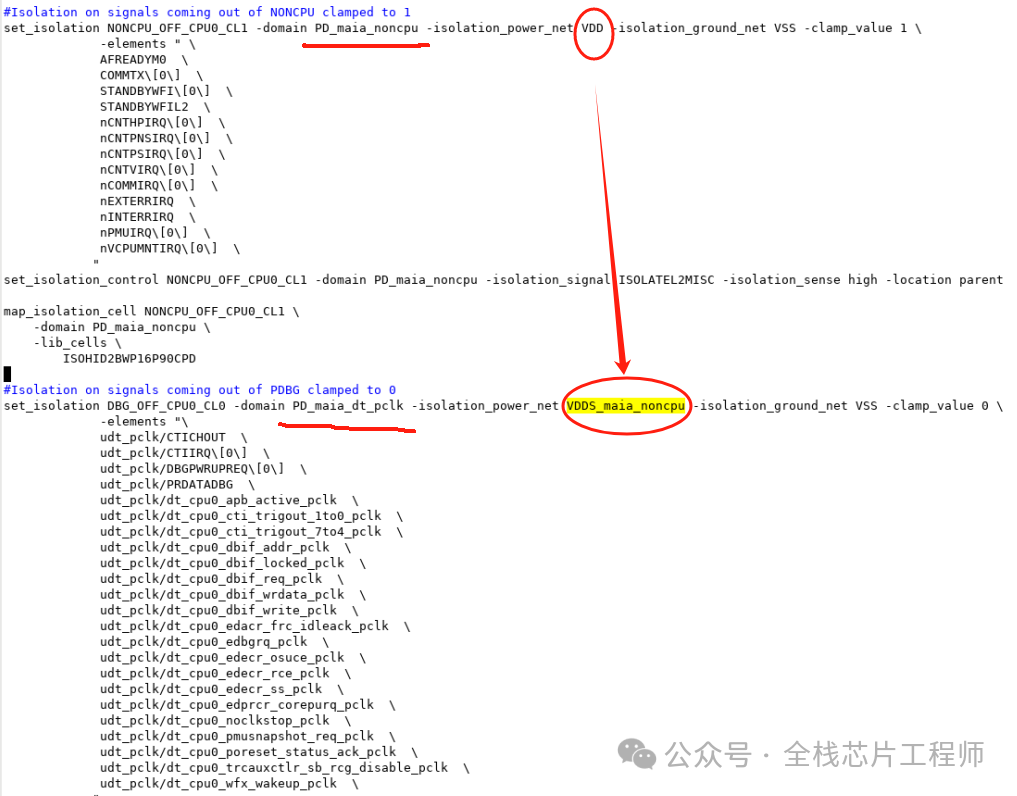

28nm A7后端设计课程采用的全国最低价格来推广,本文不做过多介绍,本文重点介绍下先进的12nm A72进阶版本课程。分享个例子,比如,Cortex-A72低功耗设计,DBG domain的isolation为何用VDDS_maia_noncpu供电而不是TOP的VDD?

答:因为dbg的上一级是noncpu,noncpu下面分成dbg和两个tbnk。

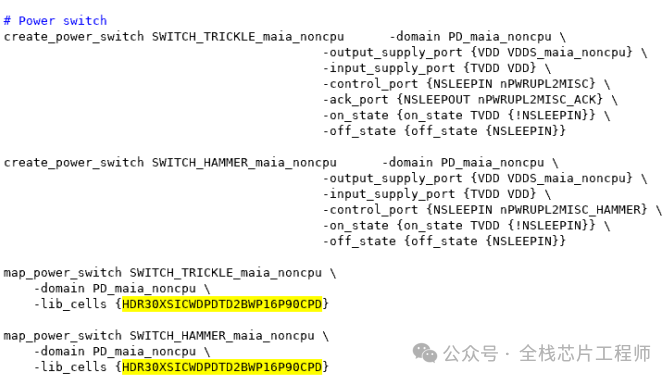

再分享个例子,比如,Cortex-A72低功耗设计,这个switch cell是双开关吗?答:不是,之所以分trickle和hammer,是为了解决hash current大电流,先开trickle,然后再开hammer。

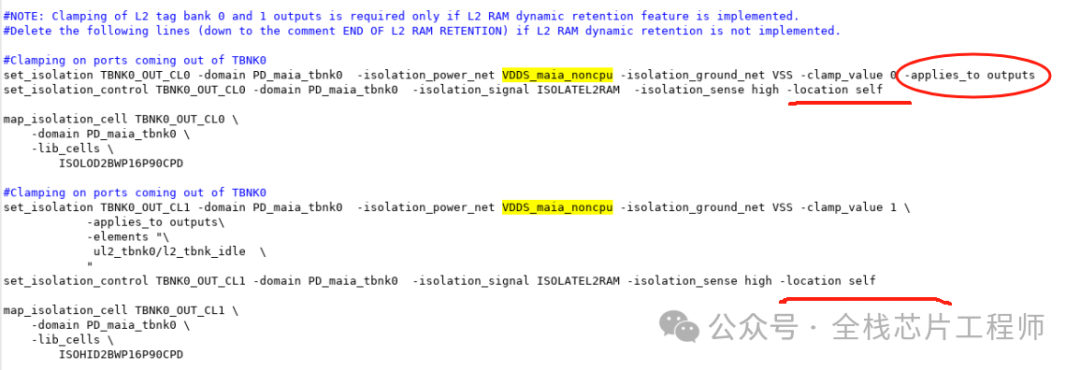

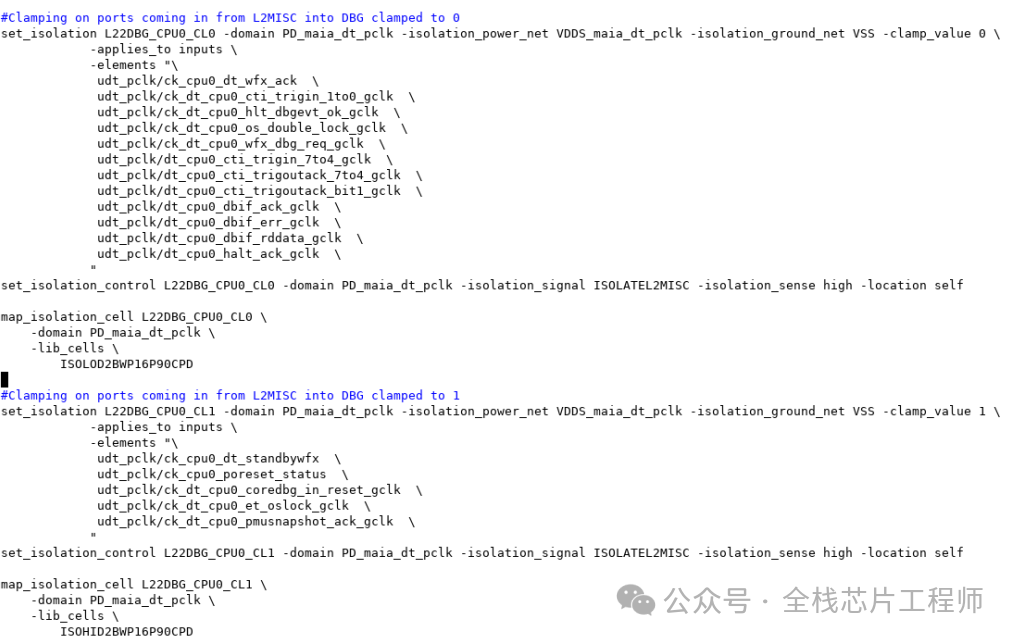

再分享个例子,比如,Cortex-A72进阶版本课程的低功耗例子:请问,如果iso cell输出都要放parent,输入放self,那么下面-applies_to_outputs对应的-location为何是self?

答:这个需要了解CPU的内部设计架构,tbnk掉电 VDDS_maia_noncpu也必然掉电,pst如下,所以-applies_to_outputs对应的-location是可以的,那么注意下debug domain呢?

实际上,没有tbnk到debug domain的信号,因此脚本如下:

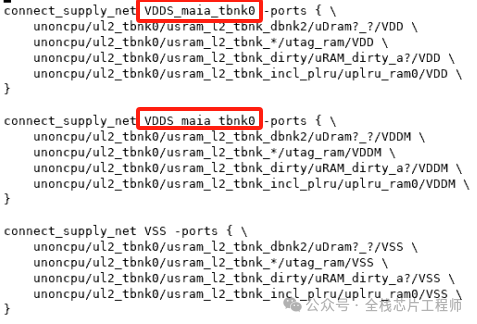

再分享个例子,比如,Cortex-A72进阶版本课程的低功耗例子:为何non_cpu的SRAM的VDD VDDM都接的可关闭电源?SRAM的VDD VDDM分别是常开、和retention电源吧?

答:本来是VDDM作为retention电源设计的,VDD关掉后 VDDM可以供电作为retention使用,但是此处没有去做memory的双电源,sram当成单电源使用,不然sram无法彻底断电。

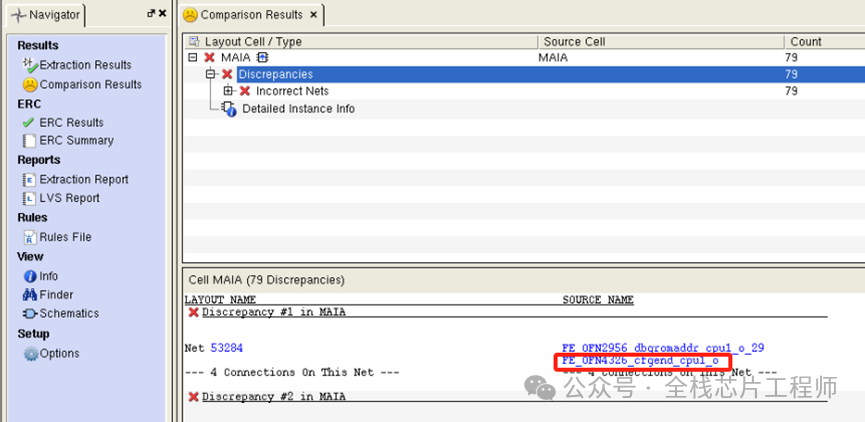

再分享个例子,比如,Cortex-A72基础版课程有学员的Cortex-A72 maia_cpu LVS通过,但是MAIA顶层LVS比对不过,我们来定位一下。

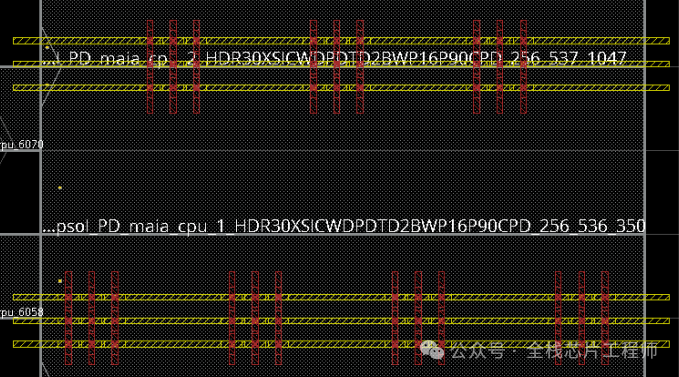

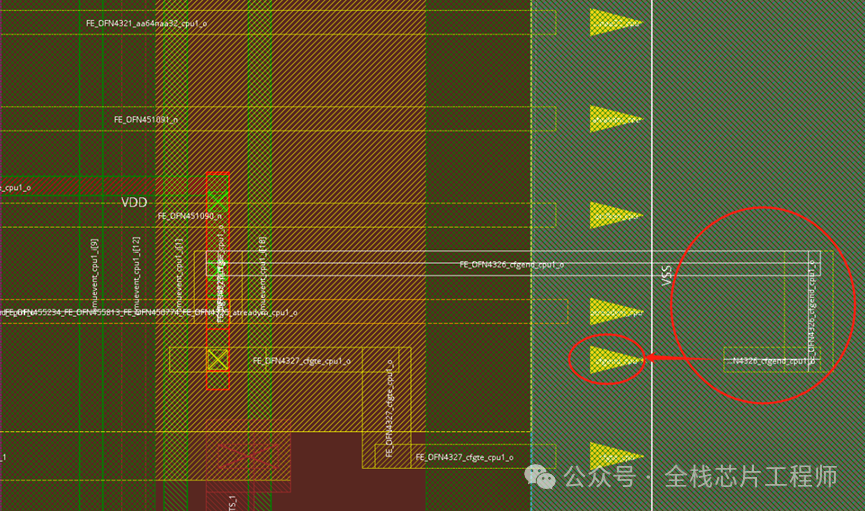

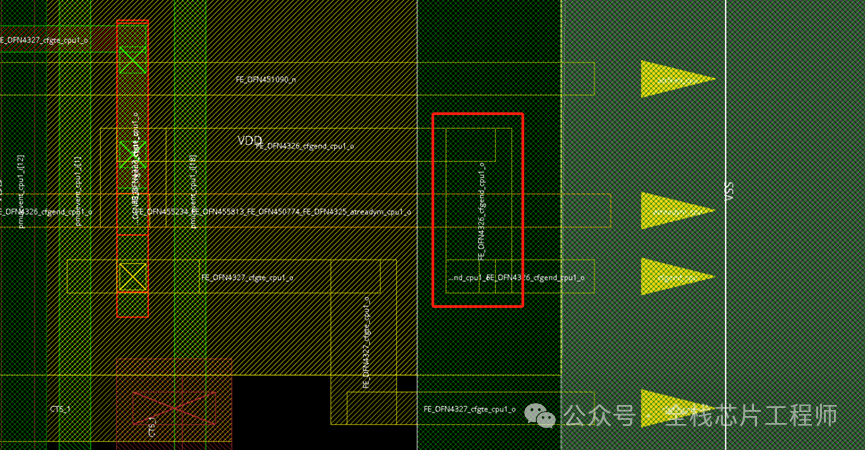

以FE_OFN4326_cfgend_cpu1_o为例,点击下图FE_OFN4326_cfgend_cpu1_o:

找到calibredrv错误坐标:(1949,139)

对应到innovus去看坐标:(1949,139)

看到maia_cpu的pin脚过于密集,造成顶层连接pin脚时候会无法绕线,从而导致innovus从maia_cpu上面走线,形成short。尽管maia_cpu带了blockage,但是invs没有足够的连接pin的routing resource,也就只能在maia_cpu上面去try了。

修改办法很简单,具体操作option参见知识星球。

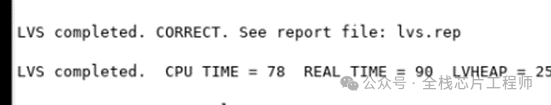

保存db,重新LVS,比对通过。

04

审核编辑:刘清

-

时钟树

+关注

关注

0文章

54浏览量

10741 -

UPF

+关注

关注

0文章

49浏览量

13504 -

Cortex-A72

+关注

关注

0文章

4浏览量

7846 -

DVFS

+关注

关注

1文章

17浏览量

11996

原文标题:玩转12nm工艺,2.5GHz频率,DVFS低功耗

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ARM最新Cortex-A72架构剑指PC,英特尔麻烦了?

ARM Cortex-A72性能狂飙:要超越Intel的节奏?

ARM Cortex-A72 MPCore处理器加密扩展技术参考手册

将GICv2中断控制器与ARM Cortex-A5x和Cortex-A72处理器集成

联发科HelioP60的12nm工艺制程对标高通骁龙660

12nm芯片是什么意思?

7nm芯片和12nm芯片的区别是什么?

有国产12nm芯片吗?

12nm芯片和7nm芯片哪个费电

12nm芯片是什么意思

中芯12nm芯片 终于量产12nm芯片

Cortex-A72核心板 | RK3399六核

12nm Cortex-A72后端实战

12nm Cortex-A72后端实战

评论