对于当今的移动高性能系统而言,低功耗设计至关重要。低功耗设计能够延长电池续航时间、降低能源成本,为消费者打造更出色的无缝体验,具有更好的可持续性。

虽然降低功耗具有许多优势,但这对芯片开发者和验证/RTL开发者来说是一项超具挑战性的任务。下一代SoC的设计规模预计将扩大10倍,一些设计的低功耗签核可能需要数天才能完成。因此,要帮助开发者在合理的周转时间内验证复杂的低功耗结构,先进的低功耗验证解决方案必不可少。

新思科技的VC LP Advanced静态低功耗验证解决方案提供了优异的解题思路,并已成功通过三星晶圆代工厂(以下简称三星)的认证。作为静态检查解决方案,VC LP Advanced技术能够有效应对低功耗设计的验证复杂性,并简化和加快调试过程。

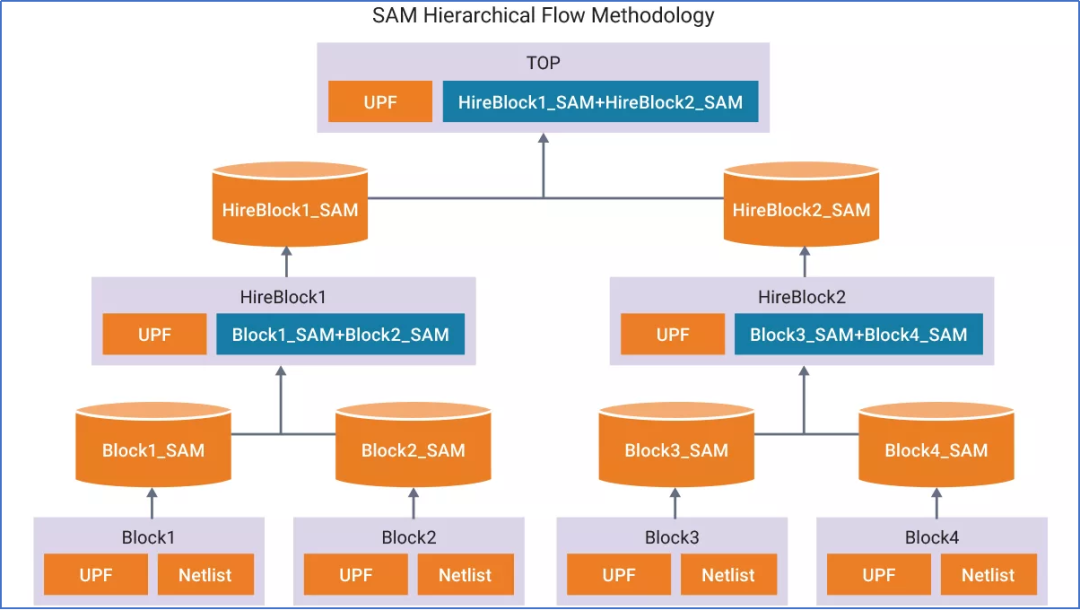

通过在RTL、综合后阶段和布局布线后阶段采用新思科技的VC LP Advanced解决方案,三星实现了十亿门级5nm低功耗移动设计签核,与传统方法相比,能够更早、更高效地发现低功耗错误。得益于多线程技术,仿真过程现在能够更高效地识别动态低功耗问题,从而使运行速度加快大约一倍。此外,签核抽象模型(SAM)流程可显著缩短运行时,实现整个芯片层面的顶层验证。这些优势帮助我们节省了大量开发时间,使验证团队能够专注于更多高价值任务。

Jianfeng Liu

设计技术团队首席工程师

三星

三星的低功耗设计使用了极其复杂的低功耗SoC设计技术,虽然可实现精细的电源管理,但也增加了设计和验证过程的复杂性。以下是三星晶圆代工厂设计中的一些常见低功耗技术:

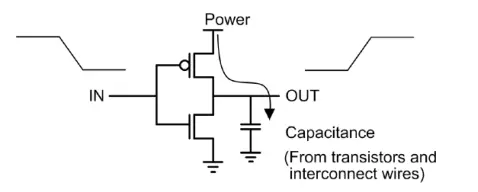

功率门控与隔离单元:功率门控技术用于在IC设计中实现电源开关,需要在电源关闭时使用隔离门将电源域的边界箝位至已知值。电源管理单元通过使能信号来控制电源开关和隔离单元,以确保关断期间,在合适的时间箝位至恰当的值。

保留单元:保留单元是与功率门控一同使用的另一项技术。在每个关断模块中,当模块关闭时,模块中的部分或全部触发器都会保存先前的值。模块通电后,先前保存的值将恢复。这不仅减少了获得已保存状态所需的时间和步骤,还缩短了将模块恢复到先前功能水平所需的整体时间,从而有效节省功耗。

电压转换器:为了实现多电压设计,需要在各个单独的电压岛中进行设计,而岛与岛之间的跨电压可能需要使用“电平转换器”单元,以实现和分析具有不同电压特性的模块。

与始终在线的SoC设计相比,复杂的低功耗SoC设计架构以及上文提到的设计元素给芯片验证和批准带来了更大的挑战。事实上,SoC级低功耗签核的复杂性远超IP级验证,因为牵涉到复杂的设计规模、数百个电源域以及数百万个需要验证的低功耗状态。此外,还存在因IP集成而起的架构复杂性,比如功能贯穿、反馈环路和基于IP所有权的报告分隔。

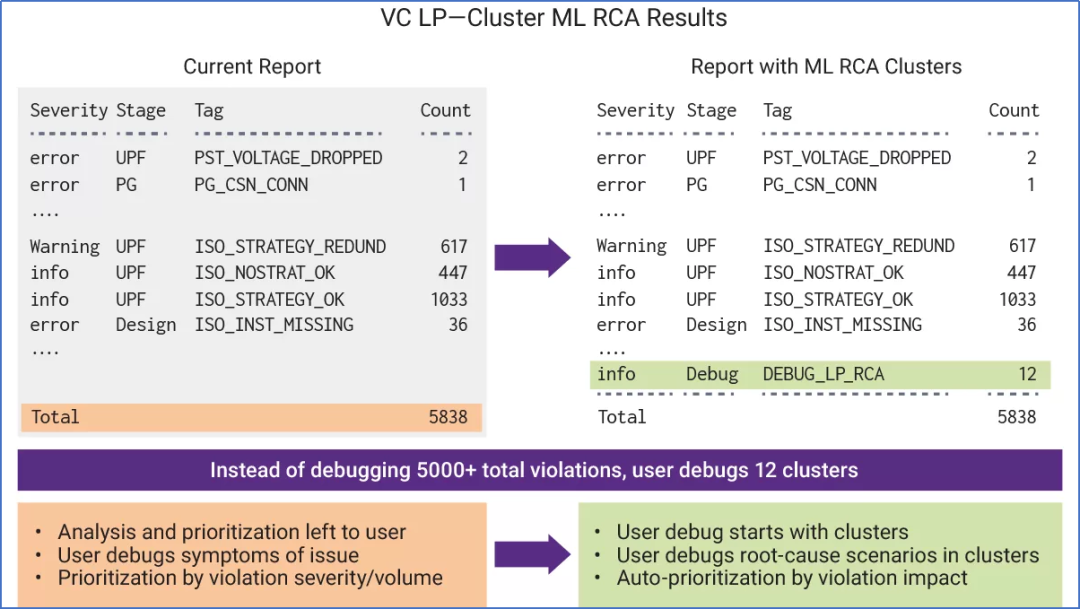

VC LP Advanced技术等静态检查解决方案能够简化并加快调试过程,从而有效降低上述复杂性。新思科技的VC LP Advanced解决方案兼备机器学习根本原因分析(ML-RCA)功能,可通过软件找出问题的根本原因,联动解决报告中其他行的错误,而不是对着一份误报非常多的报告进行调试。ML-RCA功能实际上会将大量违例进行归类,并附上具体的根本原因。在此基础上,用户可以按照类别进行调试,而不必逐一检查每个违例。VC LP可无缝扩展,以满足SoC级的复杂性、容量和性能要求,并加快从RTL到电源网格网表的低功耗签核。

最终,在支持机器学习的大容量VC LP Advanced解决方案的协助下,三星实现了高度复杂的十亿门级5nm移动低功耗芯片的一次性流片成功,并按时交付产品。

审核编辑:汤梓红

-

新思科技

+关注

关注

5文章

796浏览量

50334 -

低功耗芯片

+关注

关注

0文章

25浏览量

7926 -

三星

+关注

关注

1文章

1521浏览量

31203

原文标题:新思科技与三星联手给出5nm移动低功耗芯片一次性流片成功的解题思路

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

安富利推出S2-LP超低功耗射频收发器

物联网系统中TCP低功耗产品长连接状态下降低功耗功能的实现方案

低功耗毫米波雷达解决方案使电池供电类接近感应产品实现新功能

新思科技PCIe 7.0验证IP(VIP)的特性

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

新思科技推出业界首款PCIe 7.0 IP解决方案

LP324、LP2902超低功耗四路运算放大器规格书

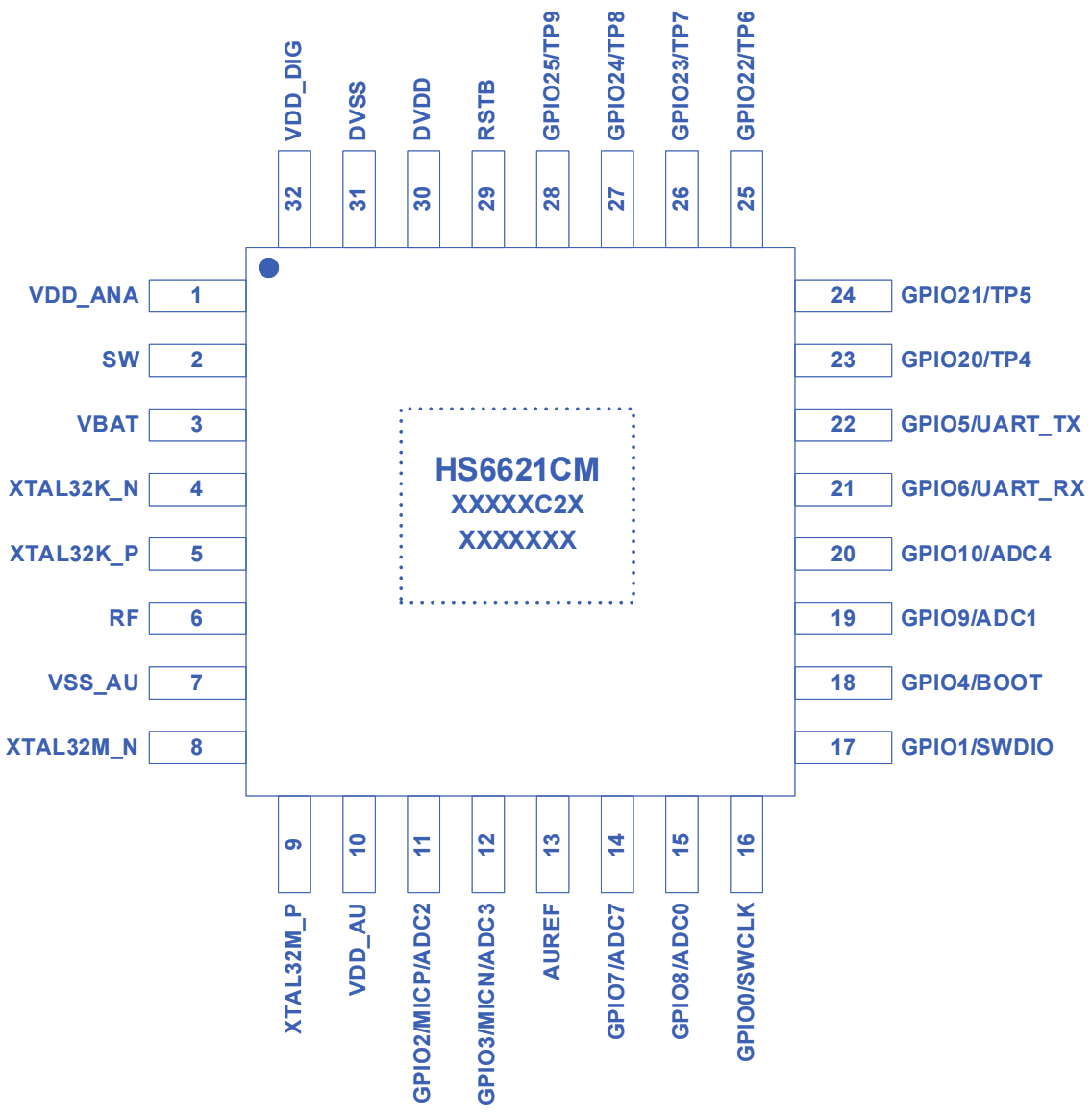

功耗优化的片上系统(SoC)解决方案,引领低功耗蓝牙与2.4GHz应用新潮流

新思科技为AMBA CHI-G协议量身定制一系列AMBA协议解决方案

新思科技硬件加速解决方案技术日在成都和西安站成功举办

Synopsys推出一款低功耗静态规则检查工具—VCLP

新思科技VC LP Advanced静态低功耗验证解决方案

新思科技VC LP Advanced静态低功耗验证解决方案

评论