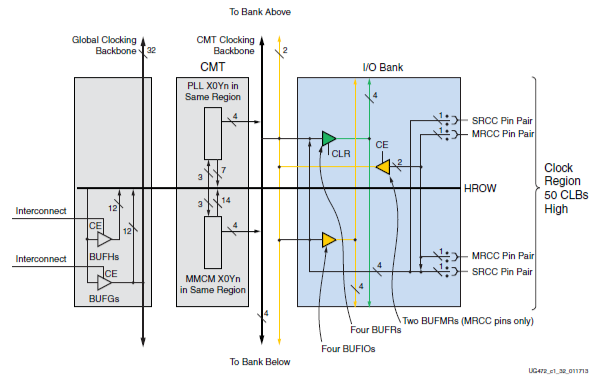

UltraScale架构的设备在时钟架构上有显著的创新,全局时钟缓冲器和局部时钟缓冲器之间的差异很小。因此,7系列的区域时钟缓冲器已被新的时钟缓冲器取代,这些新的时钟缓冲器具有更广泛的全局覆盖范围,同时自动利用局部时钟缓冲器进行时钟的局部分配。CMT模块由一个MMCM和两个PLL组成。MMCM与7系列家族非常相似,而PLL则为I/O PHY时钟提供了新特性,但在时钟设备其他部分的功能和连接性方面有所减少。

与7系列FPGA的关键差异

已从该架构中移除BUFMRs、BUFRs、BUFIOs及其相关的路由资源,并被新的时钟缓冲器、时钟路由和全新的I/O时钟架构所取代。

BUFGCTRL及其衍生物仍然可用。新架构中引入了两种新的全局时钟缓冲器资源BUFGCE和BUFGCE_DIV。在局部时钟层面,新的BUFCE_LEAF时钟缓冲器提供了具有额外特性的局部垂直时钟。

添加了用于GT时钟分频的BUFG_GT缓冲器。

现在可用的是一种新的改进的时钟路由架构。现在有两种类型的全局路由轨迹,称为路由和分发。这两种类型的路由都在CR级别提供了可分段的时钟网络。这两种类型都可以由全局时钟缓冲器驱动。分发轨迹可以由路由轨迹或直接由时钟缓冲器资源驱动。分发轨迹提供了连接到UltraScale设备中所有时钟点的连通性。

CMT现在有两个PLL而不是一个。

MMCM与7系列设备中的MMCM相似。PLL具有与I/O PHY时钟相关的新特性。然而,与其他时钟相关的功能和连通性已经减少,与7系列FPGA相比。例如,PLL不支持相位补偿或外部反馈,输出较少,与PHY时钟共享电压控制振荡器(VCO),并且与其他特性相比,与7系列设备相比有所减少。因此,大多数客户应该使用MMCM进行一般时钟。然而,剩余的PLL也可以使用。

MMCM输出时钟频率可以在不重置MMCM的情况下动态更改。

时钟区域的定义已经改变。时钟区域不再在水平方向跨越半个设备宽度。UltraScale架构的时钟区域具有固定宽度和高度的矩形形状,并以瓦片形式组织。水平和垂直时钟轨迹在时钟区域边界处分段。

时钟能力引脚(CC)已被全局时钟引脚(GC)所取代。此外,UltraScale+架构具有高密度(HD)I/O银行。这些银行包含四个全局时钟引脚,称为HDGC,可以连接到BUFGCEs。

审核编辑:黄飞

-

FPGA

+关注

关注

1628文章

21728浏览量

602945 -

时钟缓冲器

+关注

关注

2文章

96浏览量

50847 -

UltraScale

+关注

关注

0文章

117浏览量

31461

原文标题:UltraScale系列在时钟架构上的升级

文章出处:【微信号:傅里叶的猫,微信公众号:傅里叶的猫】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

针对UltraScale/UltraScale+芯片DFX应考虑的因素有哪些(2)

Xilinx UltraScale 系列发布常见问题汇总

UltraScale– UltraScale FPGA中IODelay相比7Series FPGA的改变

xilinx 7系列FPGA之电源简介

面向移动无线基站的Xilinx(r) Ultrascale(r)系列FPGA/SoC电源解决方案

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计

Xilinx 7系列与Ultrascale系列FPGA的区别

AMD推出全新Spartan UltraScale+ FPGA系列

AMD推出Spartan UltraScale+ FPGA系列产品

AMD推出全新Spartan UltraScale+ FPGA系列

UltraScale系列与7系列FPGA的差异

UltraScale系列与7系列FPGA的差异

评论