3 月 21 日,全球著名半导体公司意法半导体携手韩国科技巨头三星共同发布,18nm FD-SOI 工艺正式落地,该技术将集成嵌入式相变存储器(EPCM)。

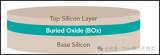

据悉,FD-SOI 是一种先进的平面半导体技术,能够通过简化制作流程进行精准的漏电流控制,相较于现有的 40nm EPM 技术,新工艺大幅度提高了性能指标:能效提升 50%,数字密度增加三倍有余,并能够承载更大的片上存储和更低的噪音系数。

值得注意的是,尽管制程仅为 18nm,但此项工艺依然保证了各种vwin 功能如电源管理及复位系统在 3V 电压环境中正常运行。另外在耐热性、防辐射性能方面都有出色表现,适用于各类严苛的工业领域。

按照计划,首批基于该工艺平台开发的 STM32 MCU 将在下半年投放到选定客户群,预计 2025 年下半年进入大规模生产阶段。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

mcu

+关注

关注

146文章

17123浏览量

350973 -

存储器

+关注

关注

38文章

7484浏览量

163759 -

半导体技术

+关注

关注

3文章

237浏览量

60706

发布评论请先 登录

相关推荐

意法半导体40nm MCU将由华虹代工

近日,欧洲芯片巨头意法半导体(STMicroelectronics,简称ST)宣布了一项与中国第二大晶圆代工厂华虹半导体合作的新计划。双方将携手

FD-SOI成≥12nm和≤28nm区间更好的选择,三星、格罗方德等公司如何布局?

,特别适用于面临性能和功耗双重挑战的相关应用,比如自动驾驶、AIoT、先进传感器和边缘智能等应用。 在2024年第九届上海FD-SOI论坛上,来自芯原股份、三星电子、意

解读芯原股份基于FD-SOI的RF IP技术平台:让SoC实现更好的通信

空间。当然,从AIoT这个应用方向也能够看出,RF IP对于基于FD-SOI工艺打造芯片是至关重要的。 在第九届上海FD-SOI论坛上,芯原股份无线IP平台高级总监曾毅分享了主题为《为SoC设计提供基于

发表于 10-23 16:04

•267次阅读

三星电子:18FDS将成为物联网和MCU领域的重要工艺

德赢Vwin官网

网报道(文/吴子鹏)今年上半年,三星在FD-SOI工艺上面再进一步。3月份,意法半导体

发表于 10-23 11:53

•267次阅读

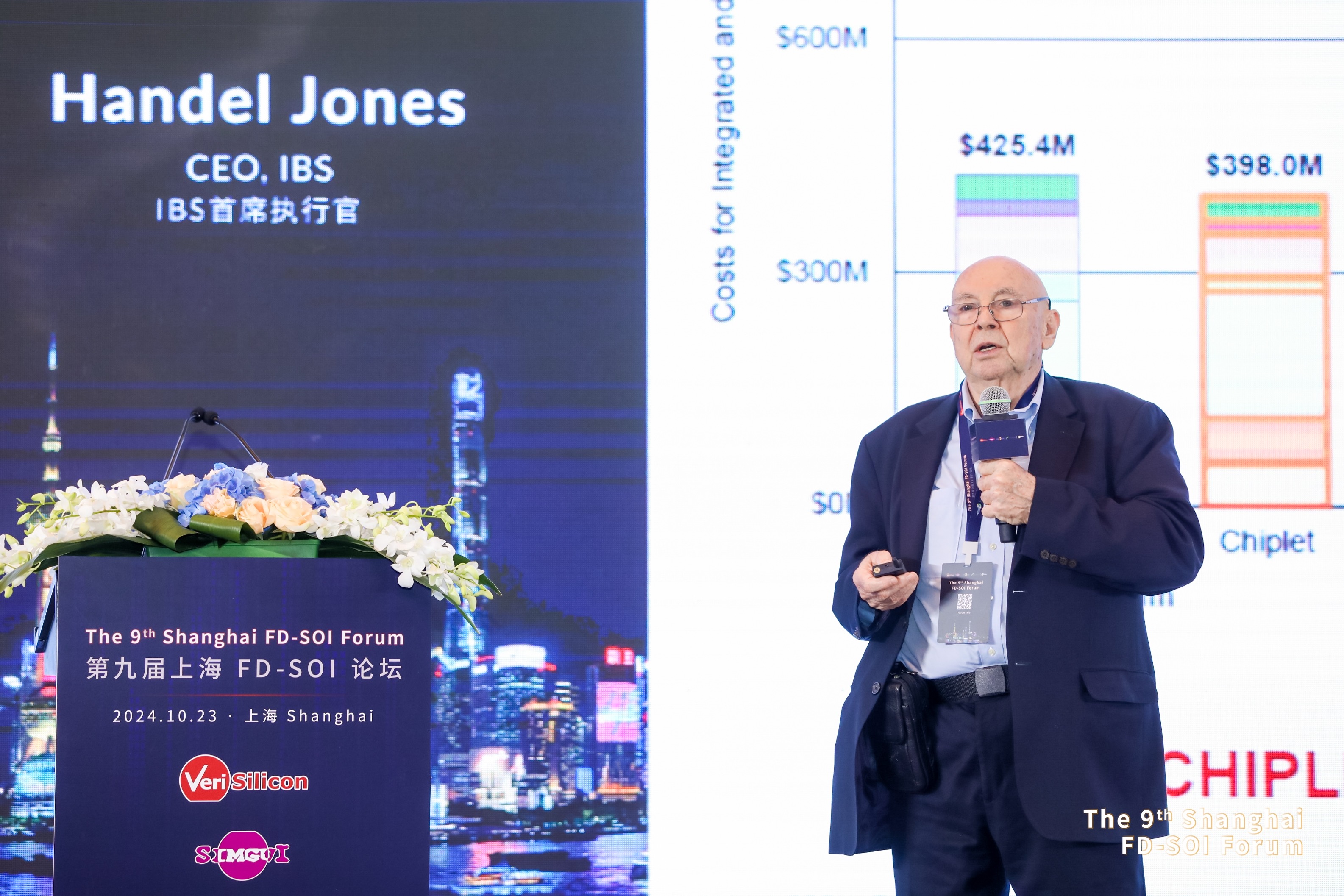

IBS首席执行官再谈FD-SOI对AI的重要性,在≥12nm和≤28nm区间FD-SOI是更好的选择

Handel Jones。 2023年第八届上海FD-SOI论坛,Handel Jones就曾受邀出席,当时他分享的主题是《为什么FD-SOI对生成式人工智能时代的边缘设备非常重要》,主要谈到

发表于 10-23 10:22

•382次阅读

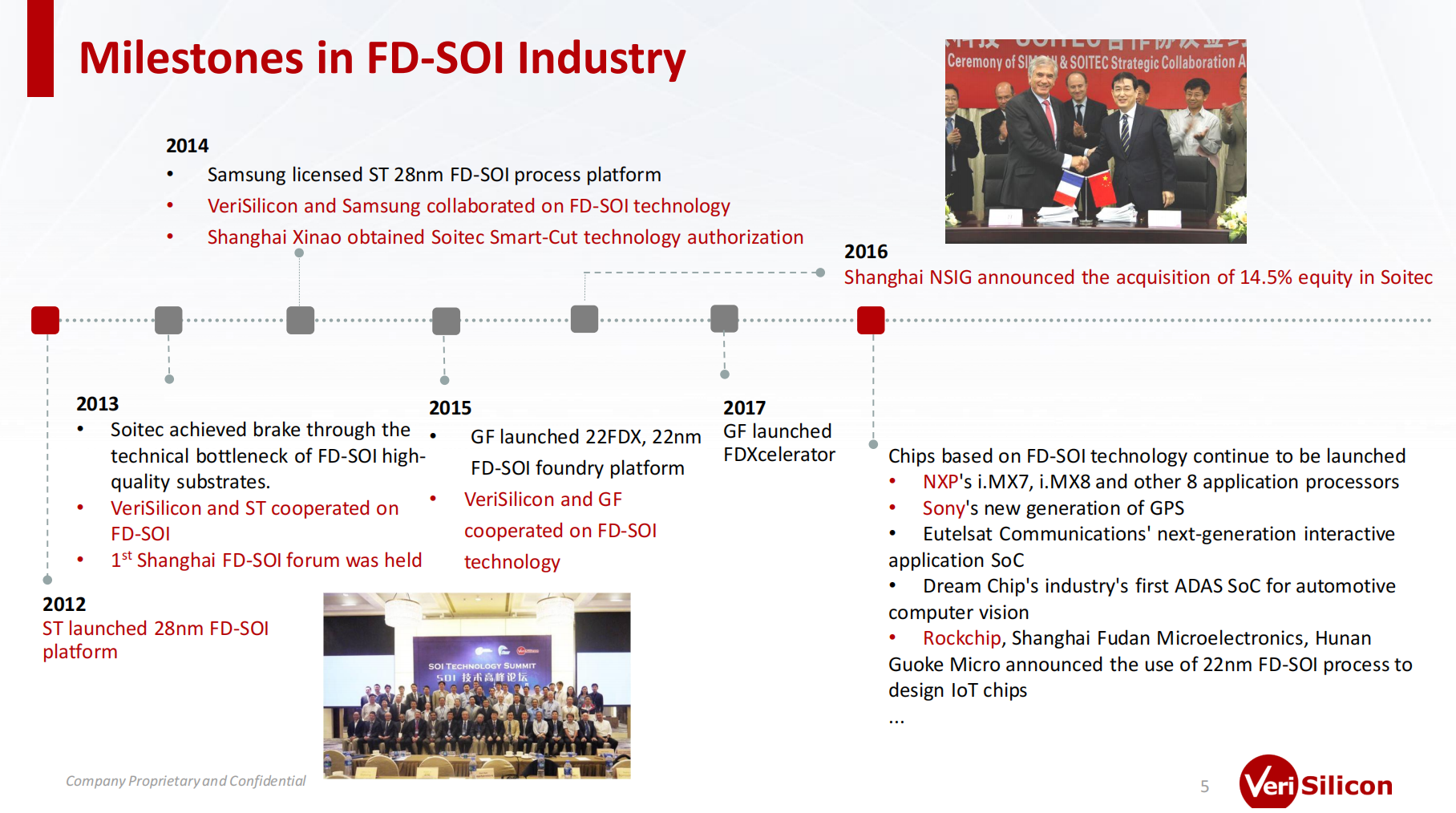

芯原戴伟民博士回顾FD-SOI发展历程并分享市场前沿技术

,以及芯原在FD-SOI提供的解决方案。 全耗尽型绝缘体上硅(FD-SOI)是一种平面工艺技术,从结构上看, FD-SOI晶体管的静电特性优于传统体硅技术。埋氧层可以降低源极和漏极

发表于 10-23 10:02

•512次阅读

意法半导体推出Page EEPROM二合一存储器 提升智能边缘设备的性能和能效

技术的能效和耐用性与闪存的存储容量和读写速度,为面临极端尺寸和功率限制的应用场景提供了一个混合存储器。 嵌入式系统需要支持日益复杂的先进功能,运行数据密集型的边缘 AI 算法,

发表于 10-16 14:18

•367次阅读

三星与新思科技携手,备战2nm工艺量产

在全球半导体行业迈向更高精度和更小尺寸的征途上,三星与新思科技近日宣布了一项重要的合作。这一合作旨在确保三星的2nm制造工艺能够顺利实现量产

意法半导体将推出基于新技术的下一代STM32微控制器

意法半导体(ST)近日宣布,公司成功研发出基于18纳米全耗尽绝缘体上硅(FD-SOI)技术,并整合了嵌入

意法半导体突破20纳米技术节点,打造极具竞争力的新一代MCU

意法半导体(简称ST)发布了一项基于18纳米全耗尽绝缘体上硅(FD-SOI)技术并整合嵌入式

广和通携手意法半导体发布支持Matter协议的智慧家居解决方案

世界移动通信大会2024期间,广和通携手横跨多重应用领域、全球排名前列的半导体公司意法半导体(STMicroelectronics,以下简称

意法半导体推出嵌入式人工智能生态系统ST Edge AI Suite

意法半导体(简称ST)日前宣布推出一项前所未有的技术突破——ST Edge AI Suite,这是一个资源丰富的嵌入式人工智能生态系统,旨在

意法半导体携手三星推出18nm FD-SOI工艺,支持嵌入式相变存储器

意法半导体携手三星推出18nm FD-SOI工艺,支持嵌入式相变存储器

评论