今天给大侠带来Vivado经典案例:使用Simulink设计FIR滤波器,话不多说,上货。

FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

Vivado自带的FIR滤波器IP核已经很好用,这里借FIR滤波器的设计,介绍Simulink图形设计编程方法。Simulink可以使设计更直观,使硬件资源得到更为高效的利用。

使用vivado的System Generator可以在simulink下快速的通过matlab的强大设计功能设计滤波器。这里使用fdatool设计了一个15阶的FIR滤波器。

软件环境:【vivado2014.2+matlab2013b】

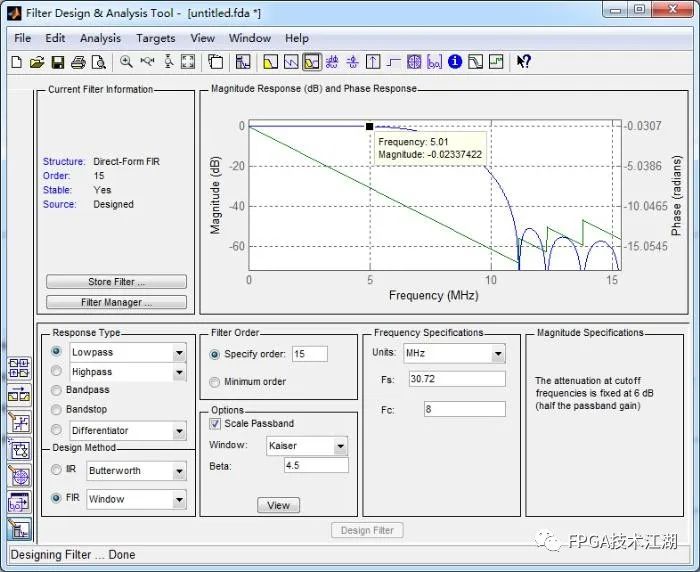

1. fdatool设计滤波器

通过matlab可以快速的设计滤波器,直接导出滤波器系数,方便大家快速设计。上图使用Kaiser窗函数设计了一个采样率为30.72MHz的15阶8M低通滤波器。File – Export 将设计好的滤波器系数Num导出到Workspace。

2.系数处理

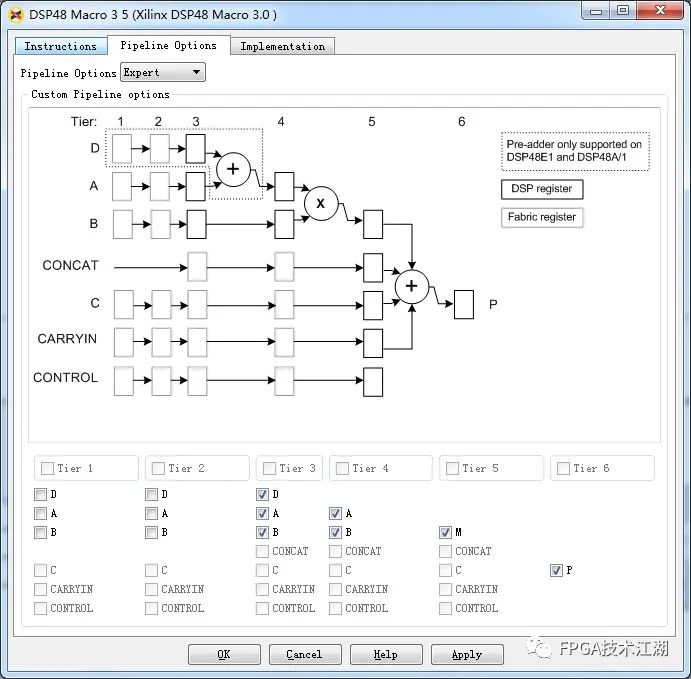

由于系数都是小数,需要重新量化,以充分利用dsp48的精度。

本例直接将系数扩大2^16倍后取整。

Num = { -0.0007 -0.0071 0.0070 0.0287 -0.0305 -0.0827 0.1244 0.4610 0.4610 0.1244 -0.0827 -0.0305 0.0287 0.0070 -0.0071 -0.0007 }

a = round ( Num * 2^16) = { -46 -467 459 1879 -2002 -5418 8152 30211 30211 8152 -5418 -2002 1879 459 -467 -46 }

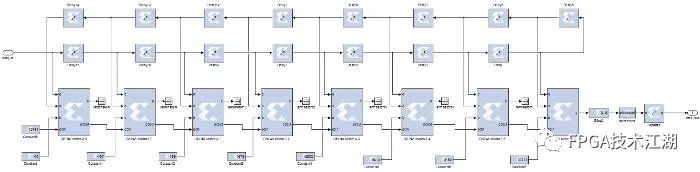

3. Simulink设计模型

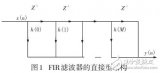

y(n) = h(0)*(x(n)+x(n-15))+h(1)*(x(n-1)+x(n-14))+h(2)*(x(n-2)+x(n-13))+h(3)*(x(n-3)+x(n-12))+h(4)*(x(n-4)+x(n-11))+h(5)*(x(n-5)+x(n-10))+h(6)*(x(n-6)+x(n-9))+h(7)*(x(n-7)+x(n-8))

利用FIR滤波器系数的对称性,采用折叠方式,可节省一半的DSP48用量,考虑到7系的DSP48普遍可以跑到200-300MHz,如信号采样率低的话,可以采用多路复用的方式大量节省DSP使用量,若只有一路信号也可以采用提高工作时钟的方式减少DSP使用量。空间与时间的相互关系,在这里表现的淋漓尽致。

模型设计的时候特别需要注意每个模块的时延,时延一定要计算清楚。

上图设计的fir滤波器,DSP的PCIN输入为上一级DSP的PCOUT信号,这样做的目的是充分利用DSP的快速进位链,使实现变得容易。最后一拍数据直接使用的DSP的P端输出。

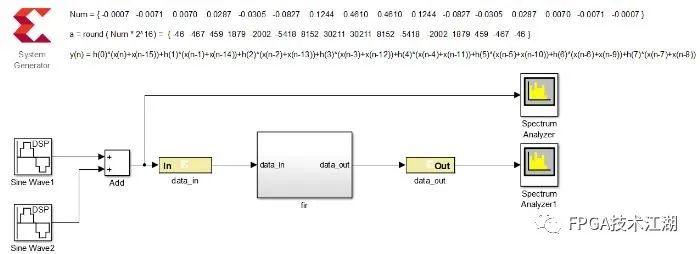

4. 模型仿真

为设计好的模型增加一个顶层,添加两个信号源作为仿真激励,使用两个频谱分析仪观测结果。

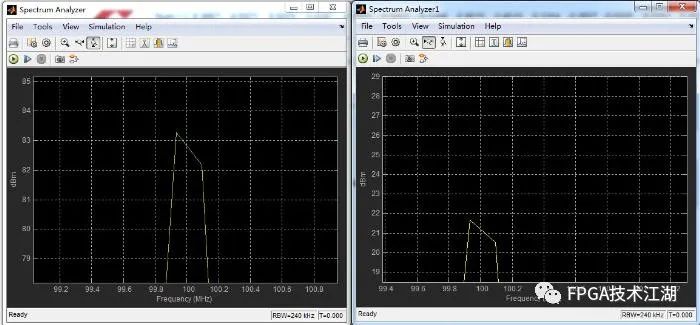

由滤波器幅值响应图可知,当信号采样率为245.76MHz时(提升了8倍),通带(原为5M提升8倍为40MHz)内信号抖动为0.03db以内,此滤波器对100MHz(对应图中12.5MHz)的抑制能力为-61db。

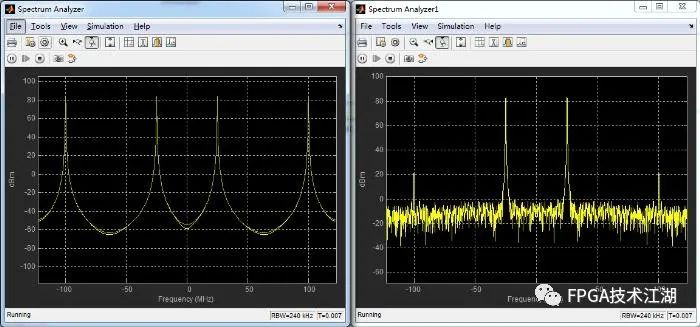

测试使用两个幅度相同、频率不同的正弦信号(25M与100M)相加作为信号输入,使用频谱分析仪观测FIR模型输出,开始仿真观测频谱仪信号。

上面左图为滤波器输入信号,右图为滤波器输出信号。观测可知此滤波器对25MHz信号功率没有影响,对100MHz信号衰减了约60db左右,将图放大可知输入100MHz功率为83.2dbm输出为21.6dbm,衰减了61.2db。由此可知与fdatool设计的滤波器性能相同。

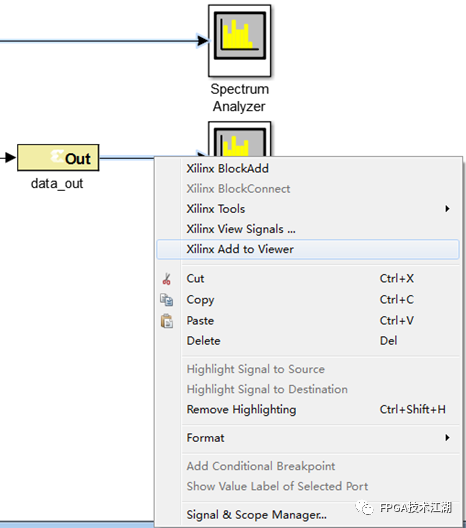

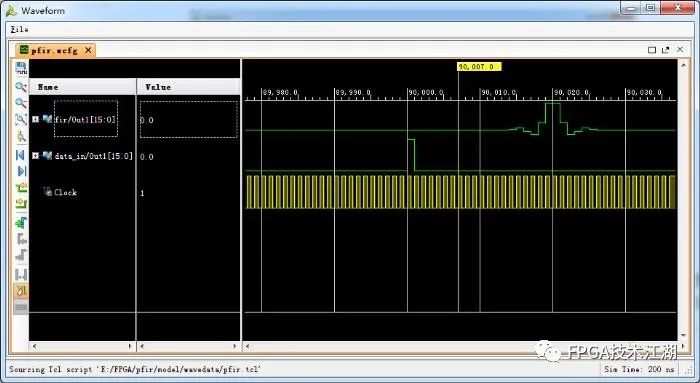

xilinx在新版本的vivado中将simulink中的WaveScope删掉了,信号观测方式换为和vivado debug相同的窗口,更为灵活和人性化。添加信号的方式更为简单,选择好需要观测的信号后直接右键单击Xilinx Add to Viewer。这时启动仿真将自动打开vivado的Waveform窗口,可以在时域上观察每一个点的数据。

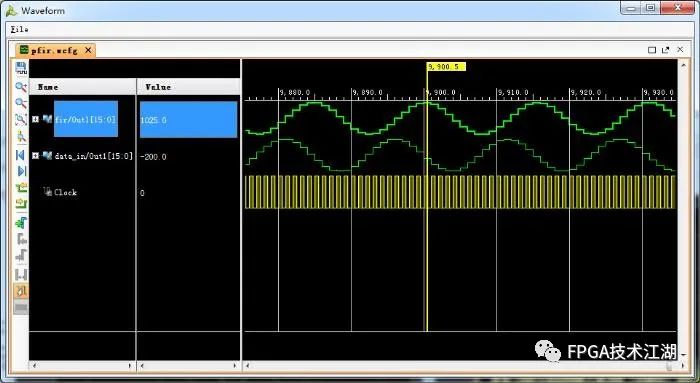

上图为单个25M正弦波作为激励信号的模型输入和输出信号。当前光标位置输入数据为1025,此fir滤波器时域上对信号有19个周期的延迟,19个周期后的数据为1024,那么20lg(1025/1024)=0.008db 抖动小于通带内抖动值0.03db。

通过将输入信号改为脉冲信号,脉冲宽度为1个周期,此时可观测到此fir滤波器的冲击响应。

经过以上步骤,基本验证此滤波器的设计能够达到需求。

5. 将模型导入到vivado工程

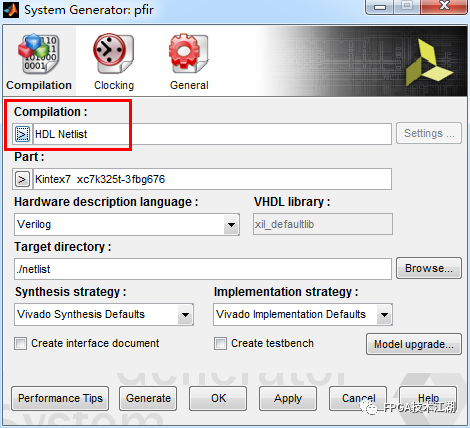

System Generator提供了几种导入方法:

1、 直接生成hdl网表文件。

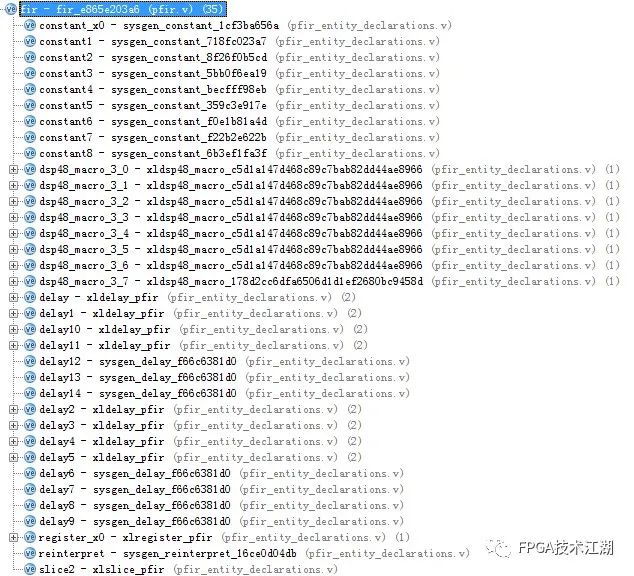

生成的.v或.vhd文件直接例化dsp的IP核,用户可直接将代码文件添加至自己的工程内。就好像模型是自己用代码完成的一样。

2、 以IP核形式生成IP。

添加IP信息,生成IP核。用户以IP核的形式直接调用。

3、 Synthesized Checkpoint形式生成网表文件(推荐)。

选择此项,用户可直接在simulink下综合出网表和约束文件,打包至.dcp文件中,用户可在vivado下直接加载dcp文件调用模型。

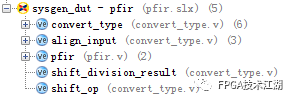

4、 直接在vivado中添加模型文件(推荐)。

Vivado的Add source中可选择Add or Create DSP Sources,直接将模型文件(.mdl或.slx)添加至工程中,综合的时候,系统将自动调用matlab分析模型文件,自动生成需要HDL文件。效果等同于自动操作的方法1,缺点是使用此方法综合工程必须装有对应版本的matlab。

审核编辑:刘清

-

dsp

+关注

关注

553文章

7987浏览量

348726 -

低通滤波器

+关注

关注

14文章

474浏览量

47384 -

Simulink

+关注

关注

22文章

533浏览量

62372 -

fir滤波器

+关注

关注

1文章

95浏览量

19037 -

Vivado

+关注

关注

19文章

812浏览量

66470

原文标题:Vivado 使用Simulink设计FIR滤波器

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何设计低通FIR滤波器

并行FIR滤波器Verilog设计

FIR滤波器系数

高阶FIR正交镜像滤波器的设计

线性相位FIR滤波器设计

FIR滤波器的FPGA设计与实现

Vivado经典案例:使用Simulink设计FIR滤波器

Vivado经典案例:使用Simulink设计FIR滤波器

评论