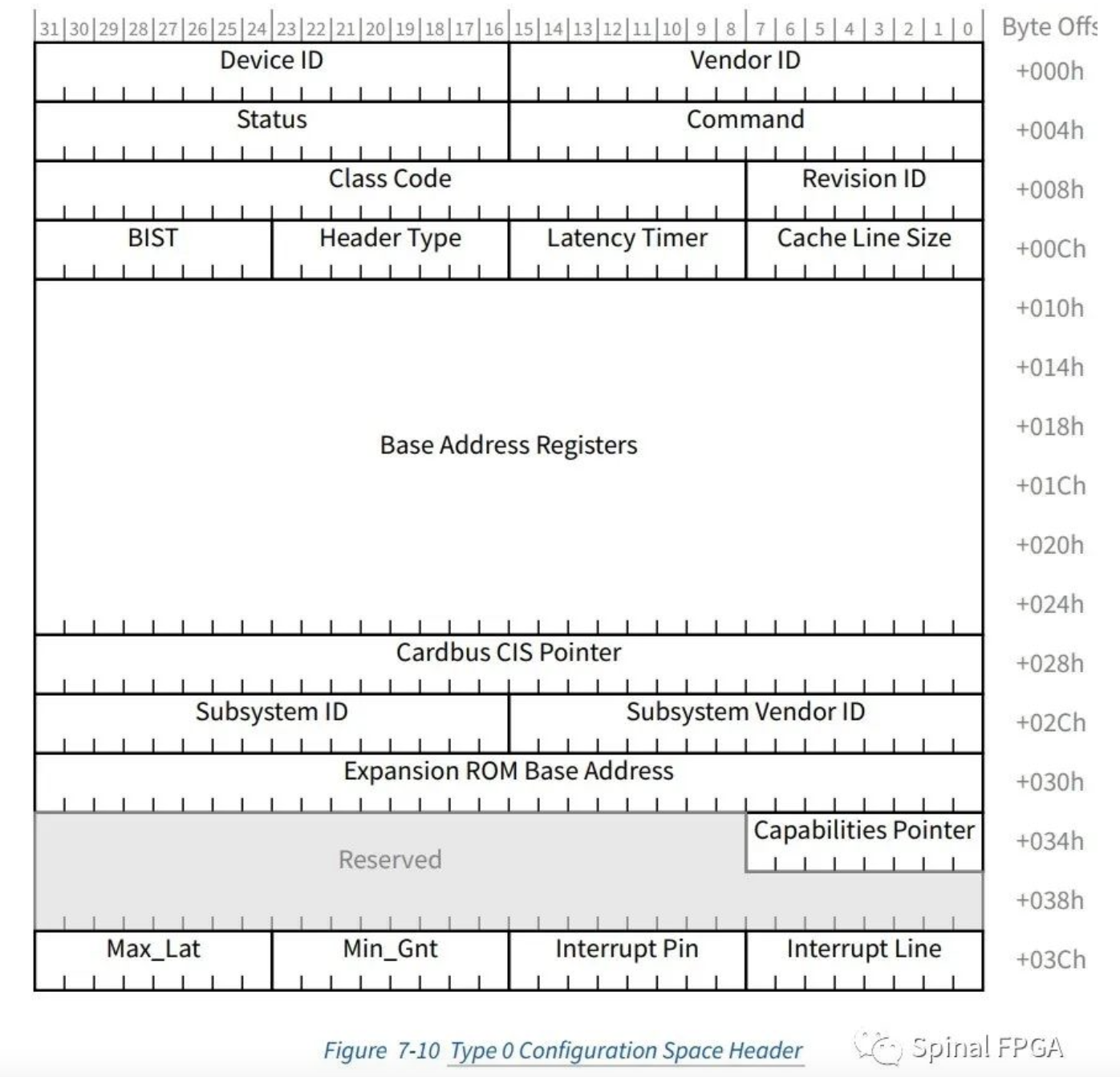

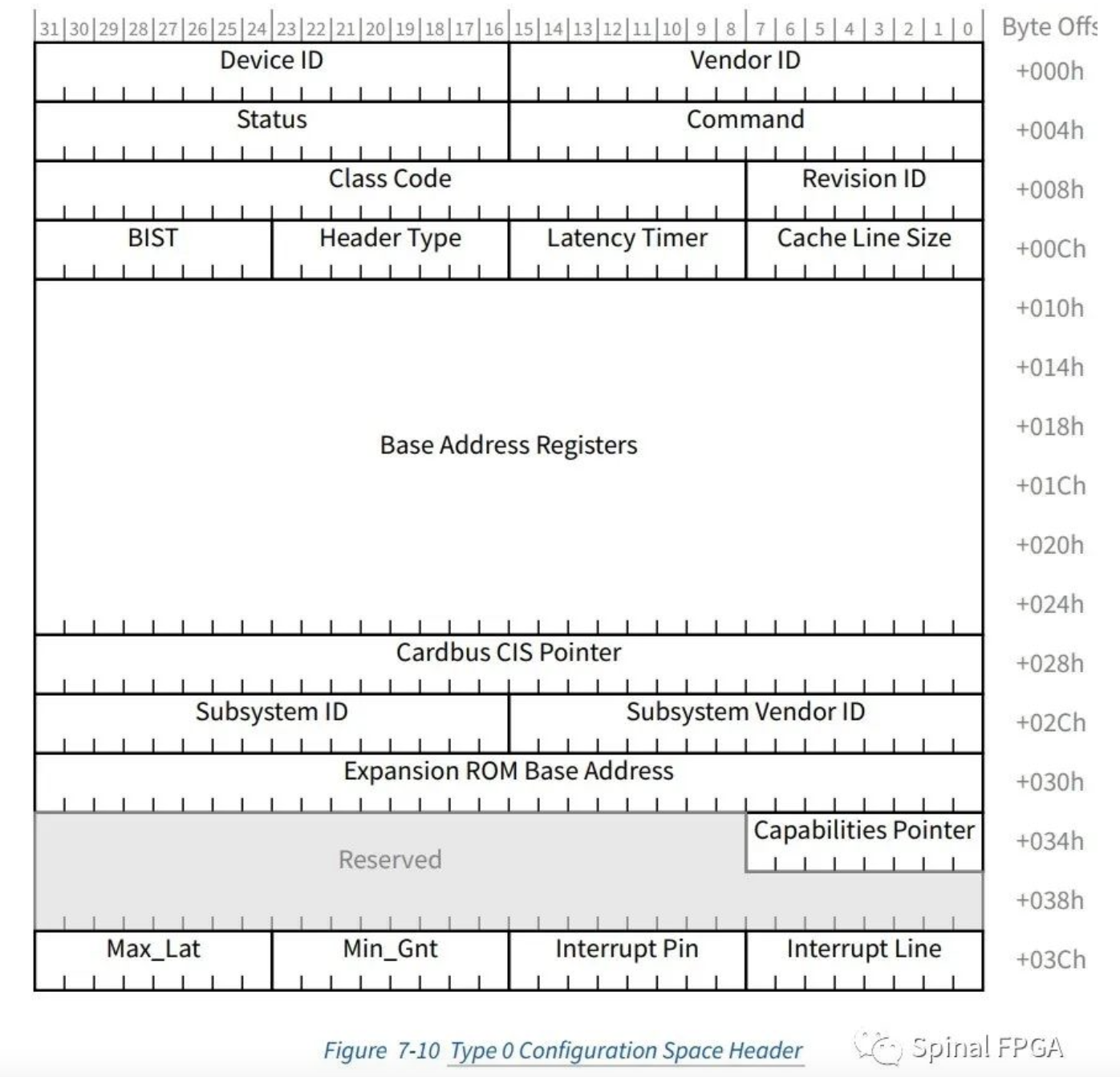

PCIE是一种高速串行总线接口标准,用于连接计算机内部的各种外设和组件。在PCIe架构中,BAR(Base Address Register)空间是用于映射I/O端口或内存地址空间的一组寄存器。

BAR空间是通过PCIe配置空间进行分配和管理的。每个PCIe设备都具有其自己的配置空间,其中包含了一组BAR寄存器。这些寄存器用于告知操作系统和其他设备该设备所需的资源,例如内存地址范围或I/O端口地址范围。

在PCIe设备的BAR寄存器中,可以配置为I/O BAR或者内存BAR。I/O BAR用于映射设备的I/O端口,而内存BAR用于映射设备的内存地址。每个BAR寄存器都包含一个基地址和一些控制位,用于指定地址范围和访问权限。

操作系统在初始化PCIe设备时,会读取BAR寄存器的值,并将相应的资源映射到系统地址空间中,以便应用程序可以通过访问这些地址来与设备进行通信。BAR空间的大小取决于每个BAR寄存器的配置,通常情况下,每个BAR寄存器的大小为32位或64位。

需要注意的是,BAR空间的大小可能会受到一些限制,例如操作系统或主板的限制。因此,在进行PCIe设备设计和驱动程序开发时,需要遵循相关的规范和要求,以确保BAR空间分配的合理性和可用性。

总结起来,PCIe的BAR空间是用于映射设备的I/O端口或内存地址空间的一组寄存器,通过配置寄存器的值,可以告知操作系统和其他设备该设备所需的资源。操作系统会将BAR空间映射到系统地址空间中,以便应用程序可以与设备进行通信。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:pcie的BAR空间的介绍

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

相关推荐

我使用windriver开发了pcie的驱动,可以通过windriver看到分配的bao0和bar1空间,其地址范围对应的是DDR3的空间,此时出现问题:可以通过windriver对

发表于 03-28 16:06

:

1.如何将DM8168 PCIe寄存器(地址是0x51000000)映射到它的内核空间,这样我就可以在内核空间通过访问其对应的虚拟地址查看PCIe寄存

发表于 05-28 01:52

\drv\exampleProjects\PCIE_exampleProject 里面的例子

这个工程可以成功跑起来,并且在PC端通过用WinDriver可以看到设备,但是目前有一个关于例程中BAR配置

发表于 06-19 00:50

设备。现在有几个问题想要搞明白:

1.pdk的PCIE例程中配置了bar1基地址为0x70000000,我通过WinDriver查看bar1基地址也是0x70000000,然后用WinDriver在

发表于 06-19 04:33

link 完成后, 在本地PCIE config空间映射的 EP端的config空间,

后续初始化EP端Bar base地址的时候,就是操作 gpPCIE_remote_EP_reg

发表于 06-21 18:49

it to the internal bus side.”

1.这段话的大概意思是说PCIe接收数据包是有条件的,只有数据包中的PCIe地址在BAR配置的地址范围内时,PCIe模块才

发表于 06-21 18:17

各位大家好,我正在尝试使用我在Xilinx论坛下载的SP605连接套件参考设计,我阅读了用户指南:我了解了如何通过BAR0和BAR1访问(读/写)寄存器,但我不明白如何通过PCIe(当然还有DMA

发表于 07-09 08:40

嗨,我正在使用AXI-PCIe桥接IP与我的逻辑进行通信。我的poroject要求有128K内存。我不知道如何配置AXI BAR地址来扩展内存。我阅读了IP文档,但没有任何意义。目前我能够从具有32K PCIe

发表于 06-19 10:14

板卡集成了16M*32Bit的SDRAM, 可通过BAR3空间+页地址访问。BAR3空间在本协议中规定为1M*32Bit的空间。所有的SDR

发表于 05-14 16:23

| 一、贵司3588J开发板,4x PCIe插槽插入我司的PCIe采集卡,无法进行大容量64MB的高端 BAR Memory地址空间分配问题:1、lspci、lspci -vvv 及相

发表于 10-20 14:56

0x18900000-0x1890ffff pref][5.246523] pci 0000:01:00.0:BAR 0:[mem size 0x400000000 64bit pref]没有空间[5.254191

发表于 04-11 06:30

可以表明主机与FPGA硬核能够链接成功,link_up后主机内核程序可以读到PCIE的配置空间信息,进而给FPGA的PCIE分配PCIE总线域空间

发表于 11-17 14:35

PCIe接口相对来讲还是打交道比较多的接口。无论是Intel还是Xilinx的IP也都接触到过。

![的头像]() 发表于

发表于 06-05 10:47

•6608次阅读

最近在研究cocotbext-pcie的实现,对于学习PCIe还是挺有帮助的,陆陆续续做个总结,有时间也会在SpinalHDL下实现类似的方针功能。

![的头像]() 发表于

发表于 07-03 17:47

•4099次阅读

CPU 发起的,访问PCIe设备配置空间的数据流。这种数据流主要是BIOS/Linux PCIe driver 对设备进行初始化、资源分配时,读写配置空间的。包括

![的头像]() 发表于

发表于 09-15 09:39

•1696次阅读

PCIE的BAR空间介绍

PCIE的BAR空间介绍

评论