在高速数据传输系统中,差分信号作为一种常见的信号传输方式,具有抗噪声能力强、传输距离远等优点。然而,差分信号的传输质量受到诸多因素的影响,其中阻抗匹配是确保信号稳定传输的关键因素之一。本文将详细探讨高速差分信号阻抗匹配的原理、方法及其重要性,以期为工程师和技术人员在实际应用中提供参考。

一、差分信号阻抗匹配的原理

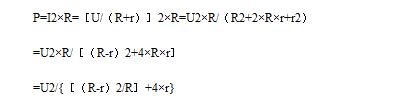

差分信号由两个相位相反、幅值相等的信号组成,通过差分线进行传输。在差分信号传输过程中,差分阻抗(Z_{diff})是一个重要的参数,它指的是差分信号在差分对中受到的阻抗。差分阻抗匹配的原理是使差分信号的源端阻抗与传输线的特征阻抗相匹配,从而减少信号的反射和失真,提高信号的传输质量。

差分阻抗匹配的实现方式有多种,包括串联端接、并联端接、戴维宁端接和RC网络端接等。这些匹配方式各有特点,适用于不同的应用场景。

二、差分信号阻抗匹配的方法

串联端接

串联端接是一种常用的差分信号阻抗匹配方法。在信号源端阻抗低于传输线特征阻抗的条件下,通过在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配。匹配电阻的选择原则是使匹配电阻值与驱动器的输出阻抗之和等于传输线的特征阻抗。串联端接的优点是器件单一、抑制振铃、减少过冲和增强信号完整性,但缺点是接收端的反向反射依然存在,影响信号上升时间并增加信号延时。

并联端接

并联端接是在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。并联端接的实现形式分为单电阻和双电阻两种形式。单电阻并联端接简单易行,但可能无法完全消除反射;双电阻并联端接可以更好地抑制反射,但电路结构相对复杂。

戴维宁端接

戴维宁端接是一种利用戴维宁定理实现的阻抗匹配方法。它通过在传输线的末端连接一个等效电路(包括一个电压源和一个串联电阻),使得从传输线看过去的阻抗与源端阻抗相等。戴维宁端接可以实现较宽的频带匹配,但电路结构较为复杂。

RC网络端接

RC网络端接是通过在传输线的末端连接一个RC网络(包括一个电阻和一个电容)来实现阻抗匹配的。RC网络端接可以在较宽的频带范围内实现阻抗匹配,并且可以通过调整RC参数来优化匹配效果。但是,RC网络端接会增加电路的复杂性和成本。

三、差分信号阻抗匹配的重要性

差分信号阻抗匹配对于高速数据传输系统的重要性不言而喻。首先,阻抗匹配可以减少信号的反射和失真,提高信号的传输质量和可靠性。在高速数据传输中,信号的反射和失真会导致数据丢失和误码率增加,严重影响系统的性能。其次,阻抗匹配可以保护驱动器免受损坏。当驱动器的输出阻抗与传输线的特征阻抗不匹配时,驱动器可能会承受过大的电压或电流,从而导致损坏。最后,阻抗匹配还可以降低系统的电磁干扰(EMI)和射频干扰(RFI)水平。通过优化阻抗匹配,可以减少系统中的噪声和干扰,提高系统的稳定性和可靠性。

四、总结与展望

高速差分信号阻抗匹配是确保高速数据传输系统稳定传输的关键因素之一。本文详细介绍了差分信号阻抗匹配的原理、方法及其重要性,并探讨了不同匹配方式的特点和应用场景。在实际应用中,工程师和技术人员应根据具体的应用需求选择合适的匹配方式,并注意优化匹配效果以提高系统的性能和稳定性。

随着电子技术的不断发展和高速数据传输系统的广泛应用,差分信号阻抗匹配技术也将不断发展和完善。未来,我们可以期待更先进的阻抗匹配方法和更高效的优化算法的出现,以满足日益增长的数据传输需求。

-

阻抗匹配

+关注

关注

14文章

350浏览量

30794 -

差分信号

+关注

关注

3文章

367浏览量

27676

发布评论请先 登录

相关推荐

详解高速PCB设计中的阻抗匹配

高速PCB设计中的阻抗匹配

高速PCB中的阻抗匹配

高速差分信号阻抗匹配详解

高速差分信号阻抗匹配详解

评论