TTL三态门电路的输出状态

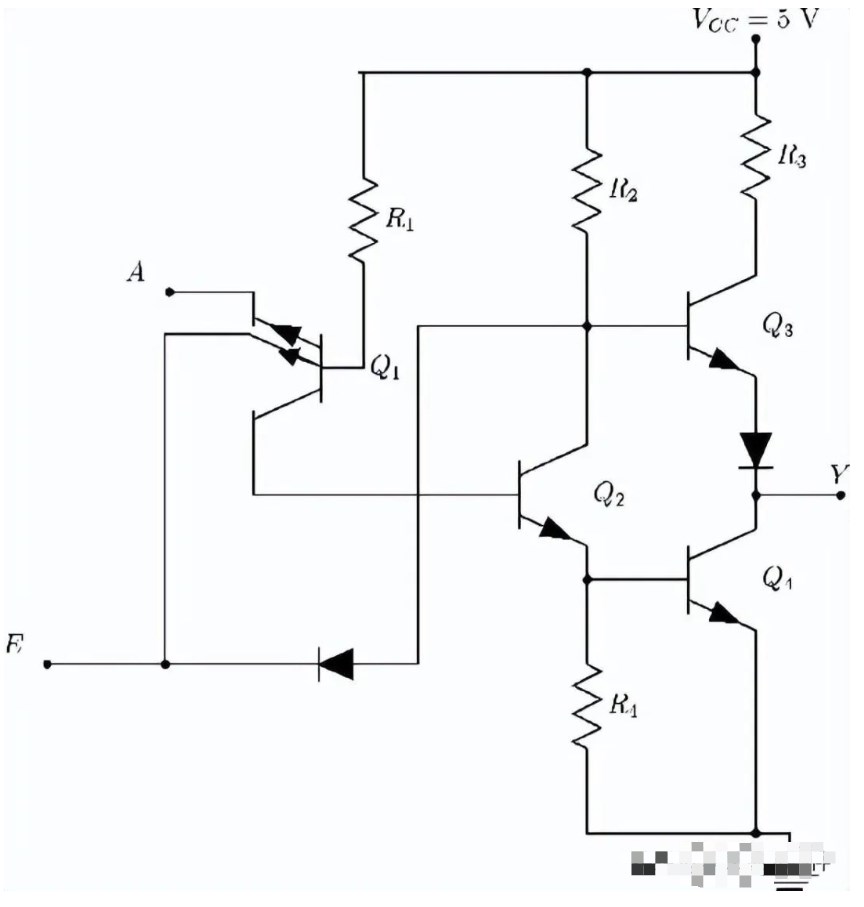

TTL(晶体管-晶体管逻辑)三态门是一种特殊类型的数字逻辑门,它具有三种输出状态:高电平、低电平和高阻抗状态(也称为三态或高阻态)。三态门的设计允许它在不输出任何信号时不会影响到总线上的其他设备,这使得多个设备可以共享同一通信总线。

TTL三态门的基本工作原理

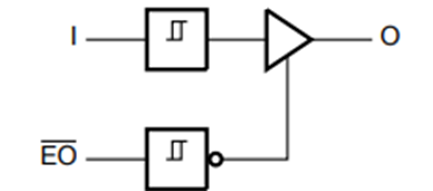

TTL三态门通常由一个或多个TTL逻辑门和一个额外的控制机制组成,这个控制机制负责将输出置于高阻抗状态。在最基本的形式中,一个TTL三态缓冲器可以简化为一个非门(NOT gate)和一个控制输入。

输出状态详解

- 高电平输出 :当控制信号被激活(通常是低电平有效),三态门将允许其内部逻辑门的输出被驱动到输出端。如果内部逻辑为非门,那么输入信号的反相将被驱动到输出。

- 低电平输出 :与高电平输出类似,当控制信号被激活时,如果内部逻辑状态为低,则输出也将为低。

- 高阻抗状态(三态) :当控制信号不被激活(通常是高电平有效),三态门的输出将进入高阻抗状态。在这种状态下,输出端不驱动任何信号,相当于开路。这允许其他设备控制总线,而不会受到这个三态门的影响。

TTL三态门的控制方式

控制三态门输出状态的是使能信号,它可以是主动低(当使能信号为低电平时允许输出)或主动高(当使能信号为高电平时允许输出)。这个使能信号通常由一个单独的逻辑电路或控制逻辑提供。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TTL

+关注

关注

7文章

503浏览量

70229 -

晶体管

+关注

关注

77文章

9682浏览量

138073 -

三态门

+关注

关注

1文章

34浏览量

18815 -

门电路

+关注

关注

7文章

199浏览量

40158

发布评论请先 登录

相关推荐

SN74AVC2T244的使能引脚OE到底是OE=低电平时输出三态,还是OE=高电平时输出三态?

SN74AVC2T244的使能引脚OE到底是OE=低电平时输出三态,还是OE=高电平时输出三态?

TI的手册也能漏洞百出?

发表于 12-04 07:48

TTL门电路的基本概念、工作原理及特性参数

TTL(晶体管-晶体管逻辑)门电路是数字电子学中的一种基本组件,广泛应用于计算机、通信和其他数字系统中。TTL门电路的工作原理基于晶体管的开关特性,通过控制输入信号的逻辑关系来实现

三态缓冲器的工作原理和应用

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,是一种特殊的逻辑门电路,其工作原理主要基于三态

三态输出门可以实现线与功能吗

三态输出门(Tri-State Output Gate)是一种特殊类型的逻辑门,它具有三个状态:高电平、低电平和高阻抗状态(也称为高阻抗或浮

TTL门电路和CMOS有什么特点及区别

基于双极型晶体管的数字逻辑电路,其工作原理是利用晶体管的开关特性来实现逻辑运算。在TTL门电路中,输入信号通过晶体管的基极-发射极结进行放大,然后通过集电极-发射极结进行开关控制,最终在输出

cmos或非门电路与ttl或非门电路的逻辑功能

本文就CMOS或非门电路和TTL或非门电路的逻辑功能进行了详细讲解。首先介绍了CMOS和TTL两种电路的基本原理和实现方式。然后分别从输入特

TTL三态门电路的输出状态?

TTL三态门电路的输出状态?

评论