本节内容主要讲述CortexR52内核Cache的具体操作包括使缓存无效(invalidate)操作,清除(clean)缓存。有的时候客户可能需要对cache做一些清理,比如invalidate,clean等操作。虽然目前在cortex R52内核很少需要操作cache,但是本节依然给一些操作指导和实践,以备以后不时之须。

操作Cache的指令

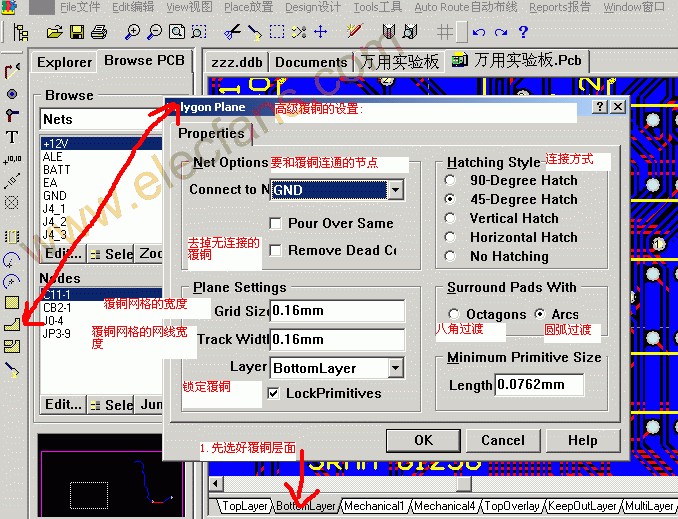

关于操作cache的指令需要参考arm cortex r52内核技术手册:

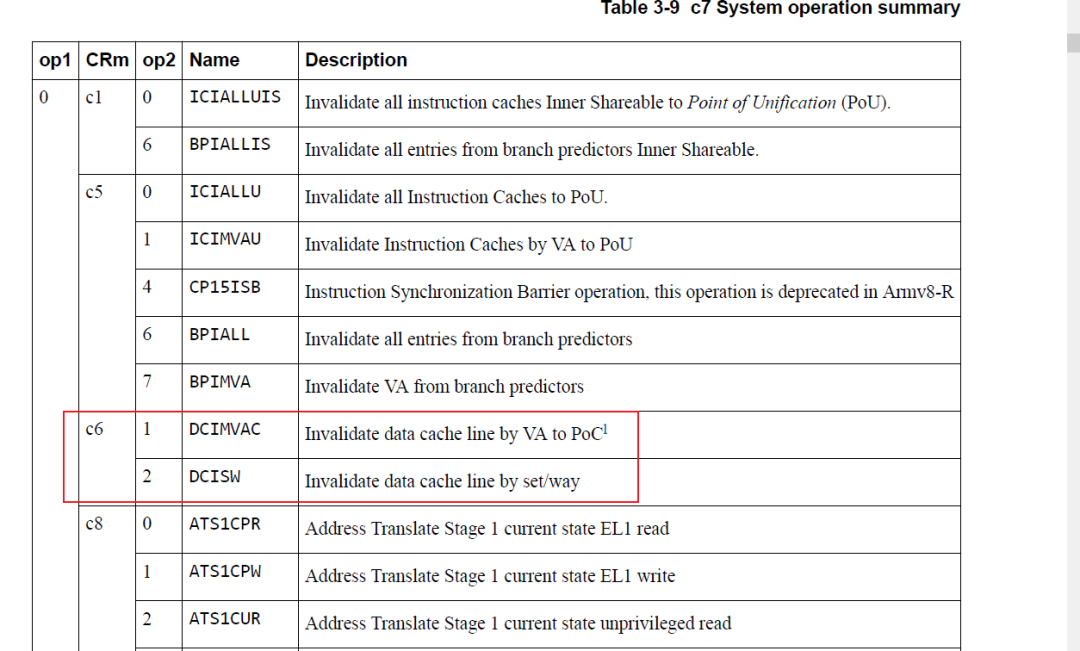

3.2.9 c7 System operations

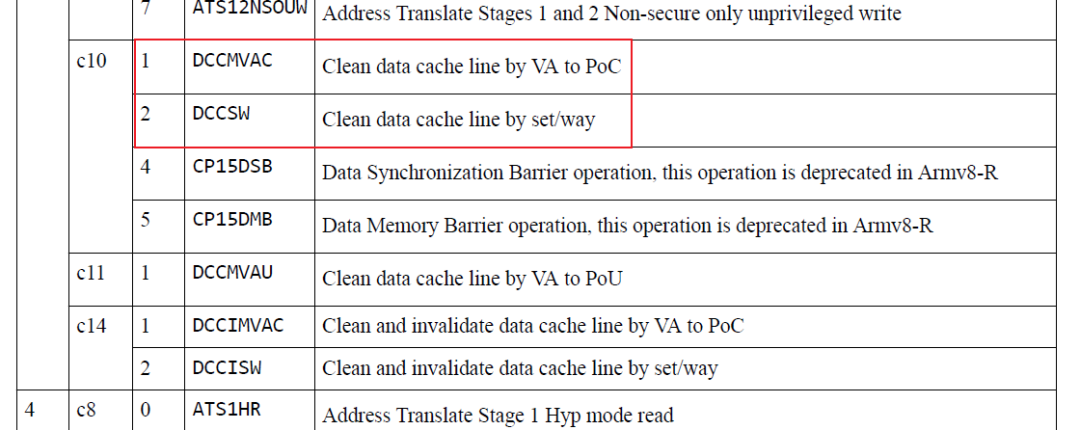

如下表中对cache的invalidate操作和clean操作。下表中其它的操作也可以根据具体的项目需求实践。

点击可查看大图

点击可查看大图

Invalidate data cache line by VA to PoC” 和 “Invalidate data cache line by set/way” 是在处理缓存时常见的两种操作方式,它们的主要区别在于缓存失效(Invalidate)的范围和方式。

1Invalidate data cache line by VA to PoC

这种操作通过虚拟地址(Virtual Address,VA)来使缓存行无效。

“PoC”代表“Point of Coherency”,意味着失效操作会影响到数据在内存中的一致性点。

这种失效方式通常用于需要保证数据一致性的情况,例如在多处理器系统中,如果一个处理器修改了内存中的数据,需要确保其他处理器不会使用到旧的缓存数据。

2Invalidate data cache line by set/way

这种操作通过缓存的集合(set)或者组(way)来使缓存行无效。

它通常用于更细粒度的缓存控制,可以针对特定的缓存集合或组进行失效操作。

这种方式可能更适用于一些特定的优化场景,例如在某些情况下只需要失效某些缓存组而不是全部的缓存行。

总的来说,两种方式都是用于使缓存行无效的操作,但在具体的应用场景中,可能会根据需要选择合适的方式来进行缓存控制。

Cache Line缓存行的概念

缓存行(Cache Line)是计算机体系结构中的一个重要概念,用于描述缓存系统中数据的基本单位。它定义了在缓存中连续的一组数据块,这些数据块在缓存中的存储和管理是以缓存行为单位进行的。

在多数现代处理器中,缓存被组织成一系列的缓存行,每个缓存行可以存储一定数量的数据。当CPU访问内存时,它通常会先检查缓存以查看所需数据是否已经存在于其中。如果数据位于缓存行中,这被称为“命中”(Cache Hit),CPU可以直接从缓存中读取数据,而不必访问主存。如果数据不在缓存中,就需要从主存加载,这称为“缓存未命中”(Cache Miss)。

缓存行的大小在不同的体系结构中可能会有所不同,但通常是64字节(或者更大)。当CPU请求一个地址中的数据时,它实际上会请求整个缓存行,而不仅仅是单个数据。这是因为缓存的性能通常会受益于数据的局部性原则,即一旦某个数据被访问,其周围的数据也很可能会被接下来访问。通过将连续的数据存储在同一个缓存行中,可以提高缓存的命中率和性能。

理解缓存行的概念对于优化程序的性能至关重要。程序员可以通过合理地利用数据的局部性原则,以及避免缓存未命中的情况,来优化程序的访存模式,从而提高整体性能。

-

内核

+关注

关注

3文章

1372浏览量

40274 -

指令

+关注

关注

1文章

607浏览量

35692 -

Cortex

+关注

关注

2文章

202浏览量

46479

原文标题:解密Cortex R52内核Cache:操作实践、性能测试与深度解析(3)

文章出处:【微信号:瑞萨MCU小百科,微信公众号:瑞萨MCU小百科】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

已知S参数和等效电路,请问怎么具体操作ADS可以得到其中的L、C大小?

看门狗定时器的具体操作

移植Miracl库的具体操作步骤

AssistiveTouch的辅助功能锁定屏幕如何具体操作呢

Protel在线教程:如何在PCB中给PCB补泪滴的具体操作

Allegro打过孔的具体操作步骤

PCB电镀工艺流程及具体操作方法

三坐标测量仪的具体操作步骤

CortexR52内核Cache的具体操作

CortexR52内核Cache的具体操作

评论