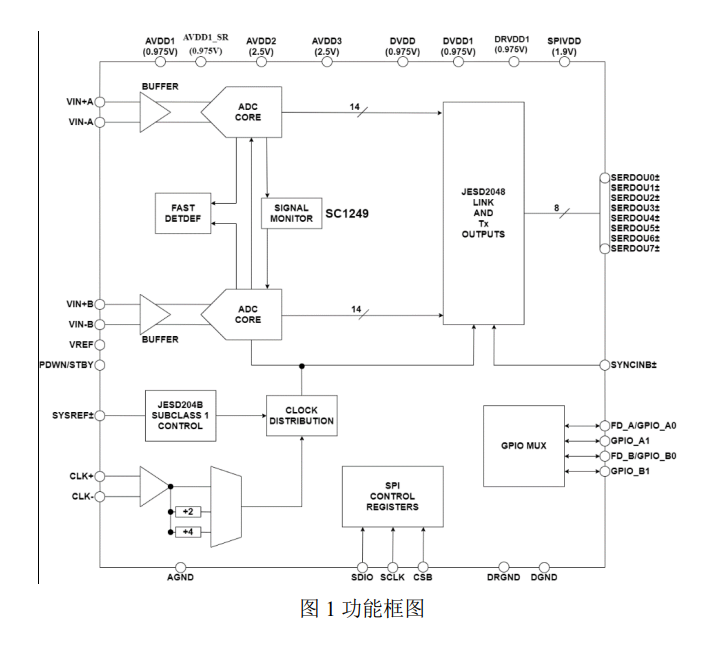

SC1249 是一款双通道、14 位、3GSPS 模数转换器ADC。该器件内置片内缓冲器和采样保持 电路,专门针对低功耗、小尺寸和易用性而设计。该产品设计支持通信应用,能够实现高达 5GH z 的宽带宽vwin 信号直接采样。SC1249 在多方面进行了优化,其中包括宽输入带宽、高采样速 率、出色的线性度以及小封装低功耗。 这款双通道 ADC 内核采用多级、差分流水线架构,并集成了输出纠错逻辑。每个 ADC 均具 有宽带宽输入。集成基准电压源可简化设计考量。模拟输入和时钟信号均为差分输入信号。 SC1249 利用 ADC 的寄存器(0x0245)中的快速检测控制信号,可编程阈值检测器可以监控输 入信号功率。如果输入信号电平超过可编程阈值,快速检测指示器就会变为高电平。由于该阈值 指示器的延迟极短,因此用户能够快速调低系统增益,从而避免 ADC 输入端出现超量程现象。除 了快速检测输出外,SC1249 还具有信号监控能力。信号监控模块可提供 ADC 进行数字化处理信 号的其它信息。 用户可将 JESD204B(子类 1)的高速串行输出设置为各种单通道、双通道、四通道和八通道 配置,具体取决于接收逻辑器件的可接受通道速率。SYSREF±和 SYNCINB±输入引脚支持多芯片 同步。 SC1249 具有灵活的关断选项,在需要时可以大幅降低功耗。所有这些特性均可通过三线串行 接口(SPI)进行编程。 SC1249 采用 196 引脚 BGA 封装,额定温度范围为−40°C 至+85°C。 产品特色 ◼ 支持约 5 GHz 的直接射频(RF)信号采样。 ◼ SPI 控制各种产品特性和功能,满足特定系统要求。 ◼ 可编程的快速超范围检测和信号监测。 ◼ 196 球 BGA 封装(12mmx12mm) 无需散热器

操作原理 SC1249 具有两个模拟输入通道和八个 JESD204B 输出通道对。 ADC 能接受的采样带宽最高达 5GHz。SC1249 有着宽输入带宽、高采样率、出色的线性度 及小封装和低功耗等特点。 双 ADC 内核采用多级差分流水线架构,带有集成的输出纠错逻辑。每个 ADC 都具有宽带宽 输入,支持各种用户可选择的输入范围。集成电压基准简化了设计考虑。 SC1249具有多种功能,可简化通信接收器中的AGC功能。可编程阈值检测器允许使用ADC 的快速检测信号来监控输入信号功率。如果输入信号电平超过可编程阈值,则快速检测指示器变 高。由于该阈值指示器具有低延迟,因此用户可以快速调低系统增益以避免 ADC 输入出现超量 程情况。 基于 JESD204B(子类 1)的高速串行输出数据通道可以配置为单通道 (L = 1)、双通道 (L =2)、 四通道 (L =4) 和八通道 (L = 8) 配置,取决于采样率和抽取率。通过 SYSREF± 和 SYNCINB±输 入引脚支持多器件同步。SC1249 中的 SYSREF±引脚还可用作数据通过 ADC 并从 JESD204B 接 口输出时的时钟指示信号。 ADC 架构 SC1249 的由一个输入缓冲流水线 ADC 组成。输入缓冲器为模拟输入信号提供端接阻抗。该 终端阻抗设置为 200Ω。输入缓冲器针对高线性度、低噪声和低功耗进行了优化。 模拟输入注意事项 SC1249 的模拟输入是一个差分缓冲器。缓冲器的内部共模电压为 1.5V。时钟信号在采样模 式和保持模式之间交替切换输入电路。 可以在输入端放置一个差分电容或两个单端电容(或两者的组合)以提供匹配的无源网络。 这些电容最终会形成一个低通滤波器,以限制不需要的宽带噪声。 通常,精确的前端网络组件值取决于应用程序。 差分输入配置 有多种驱动 SC1249 的方法,可以是主动的,也可以是被动的。通过差分模拟输入实现最佳 性能。 对于要求 SNR 和 SFDR 关键参数的应用,推荐使用差分变压器耦合作为输入配置(见图 30 和表 7),因为大多数放大器的噪声性能不足以实现 SC1249 的真实性能。

审核编辑 黄宇

-

adc

+关注

关注

98文章

6495浏览量

544461 -

雷达

+关注

关注

50文章

2930浏览量

117465 -

GSPS

+关注

关注

0文章

48浏览量

16917

发布评论请先 登录

相关推荐

ADC12DJ5200SE 10.4GSPS单通道或5.2GSPS双通道12位射频采样模数转换器(ADC)数据表

ADC12DJ2700 5.4GSPS单通道或2.7GSPS双通道12位射频采样模数转换器(ADC)数据表

ADC12DJ3200 6.4GSPS单通道或3.2GSPS双通道12位射频采样模数转换器(ADC)数据表

ADC08DJ3200 6.4GSPS单通道或3.2GSPS双通道8位射频采样模数转换器数据表

AD9208双通道、14位、3 GSPS模数转换器(ADC)英文手册

ADC12DJ4000RF 8GSPS单通道或4GSPS双通道、12位射频采样模数转换器(ADC)数据表

ADC12DL3200 6.4GSPS单通道或3.2GSPS双通道12位模数转换器(ADC)数据表

ADC32RF5x双通道14位2.6至3GSPS射频采样数据转换器数据表

ADC34RF55四通道14位3GSPS射频采样数据转换器数据表

ADC12DJ5200-SP 10.4GSPS单通道或5.2GSPS双通道12位射频采样模数转换器(ADC)数据表

双通道3GSPS ADC SC1249替代ADI的AD9208用于测绘雷达

双通道3GSPS ADC SC1249替代ADI的AD9208用于测绘雷达

评论